# CPLD Schematic Design Guide

Getting Started with Schematic Design

**Design Entry Techniques**

Controlling Design Implementation

**Design Applications**

**Attributes**

CPLD Library Selection Guide

Fitter Command and Option Summary

**Simulation Summary**

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A. Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreGenerator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, Select-RAM, Select-RAM+, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1999 Xilinx, Inc. All Rights Reserved.

### **About This Manual**

This *CPLD Schematic Design Guide* provides information on using the CPLD fitter and supported CAE interfaces to create designs for Xilinx CPLD devices. It focuses on schematic design techniques, including making the best use of library components in schematics. For more detailed information about using CPLD with CAE tool interfaces, refer to the following:

Libraries Guide

For related information about CPLD design entry, refer also to the following:

CPLD Synthesis Design Guide

#### **Additional Resources**

For additional information, go to http://support.xilinx.com. Use the search function at the top of the support.xilinx.com page or click links that take you directly to online resources.

The following table provides information on tutorials and some of the resources you can access using the support.xilinx.com advanced Answers Search function.

| Resource            | Description/URL                                                                                                                                                          |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tutorial            | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                    |  |

| Answers<br>Database | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm |  |

| Resource          | Description/URL                                                                                                                                                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application Notes | Descriptions of device-specific design techniques and approaches<br>http://www.support.xilinx.com/apps/appsweb.htm                                                                                                                                                  |

| Data Book         | Pages from <i>The Programmable Logic Data Book</i> , which describe device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://www.support.xilinx.com/partinfo/databook.htm |

| Xcell Journals    | Quarterly journals for Xilinx programmable logic users http://www.support.xilinx.com/xcell/xcell.htm                                                                                                                                                                |

| Tech Tips         | Latest news, design tips, and patch information on the Xilinx design environment http://www.support.xilinx.com/support/techsup/journals/index.htm                                                                                                                   |

#### **Manual Contents**

This manual covers the following topics:

- Chapter 1, "Getting Started with Schematic Design" chapter, presents an overview of schematic design for CPLD devices, including a simple example design.

- Chapter 2, "Design Entry Techniques", describes the fundamental techniques for expressing logic in a schematic design for a CPLD device.

- Chapter 3, "Controlling Design Implementation", discusses techniques for controlling how various parts of your design are implemented into a CPLD device.

- Chapter 4, "Design Applications", describes useful techniques for expressing efficient CPLD designs.

- Appendix A, "Attributes" lists and describes CPLD schematic attributes, which allow access to CPLD architectural features.

- Appendix B, "CPLD Library Selection Guide" lists all the symbols that may be used in CPLD schematic designs.

- Appendix C, "Fitter Command and Option Summary" summarizes implementation options of the Design Manager, and lists parameters for the the cpld command.

• Appendix D, "Simulation Summary" appendix shows how to sumulate from the Design Manager and command line.

### Conventions

This manual uses the following typographical and online document conventions. An example illustrates each typographical convention.

### **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: -100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt_del_net=

```

Courier bold also indicates commands that you select from a menu.

```

\textbf{File} \rightarrow \textbf{Open}

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

```

edif2ngd design_name

```

References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on | off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

```

allow block block name loc1 loc2 . . . locn;

```

#### **Online Document**

The following conventions are used for online documents.

- Red-underlined text indicates an interbook link, which is a cross-reference to another book. Click the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click the blue-underlined text to open the specified cross-reference.

## **Contents**

|           | Additional Resources Manual Contents Typographica Online Document                                                                                                                                                                                                                                                                                                                                                                                                                                          | . vi<br>.l ix                                                                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 | Getting Started with Schematic Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 1-1                                                                                                                                             |

|           | Overview of Schematic Design Methods Design Flow Summary Generated Reports Timing Simulation Schematic Design Flow Example Configuring the Design Entry Tool Workview Office Project Manager Viewlogic On Workstations Mentor Drawing the Design Performing Functional Simulation (Optional) Viewlogic Mentor Implementing the Design Creating an EDIF Netlist Implementing from Design Manager Examining the Reports Performing Timing Simulation Workview Office and Powerview Mentor Device Programming | . 1-2<br>. 1-3<br>. 1-3<br>. 1-4<br>. 1-5<br>. 1-5<br>. 1-6<br>. 1-7<br>. 1-7<br>. 1-8<br>. 1-9<br>. 1-10<br>. 1-11<br>. 1-11<br>. 1-12<br>. 1-13 |

| Chapter 2 | Design Entry Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                   |

|           | Library Symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 2-1<br>. 2-2                                                                                                                                    |

|           | Primitives, Macros and User-Generated Symbols | 2-2  |

|-----------|-----------------------------------------------|------|

|           | Power and Ground Signals                      |      |

|           | Input/Output Buffers                          | 2-4  |

|           | Inputs, Outputs, and Bidirectionals           | 2-4  |

|           | Clock Inputs                                  | 2-5  |

|           | Output Enable Signals                         | 2-7  |

|           | Asynchronous Clear and Preset                 | 2-9  |

|           | Clock Enable                                  |      |

|           | Tristate Multiplexing                         |      |

|           | LogiBlox Modules                              |      |

|           | Program Inputs and Outputs                    | 2-14 |

|           | Schematic Design Flow                         | 2-15 |

|           | Changing a Schematic Module                   | 2-16 |

|           | Behavioral Modules                            | 2-16 |

|           | Compiling Behavioral Logic                    | 2-16 |

|           | Behavioral Module Symbols in Schematics       | 2-17 |

|           | Behavioral Module Example for Viewlogic       |      |

|           | Hierarchical Design                           |      |

|           | Custom Macro Example for Viewlogic            | 2-20 |

|           | Retargeting a Design From a Different Family  | 2-21 |

|           | Schematic Conversion Procedure                | 2-21 |

|           | Using Workview Office                         | 2-22 |

|           | Using Viewlogic Powerview on Workstations     | 2-23 |

|           | Processing a Design After Conversion          | 2-24 |

|           | Attribute Compatibility                       | 2-25 |

|           | Converting Behavioral Modules                 | 2-25 |

| Chapter 3 | Controlling Design Implementation             | 3-1  |

|           |                                               |      |

|           | Target Device Selection                       | 3-1  |

|           | Controlling Preload Values                    |      |

|           | Controlling Power Consumption                 |      |

|           | Changing Power Mode for a Specific Componen   |      |

|           | Changing Global Power Mode                    | 3-4  |

|           | Controlling Output Slew Rate                  | 3-4  |

|           | Controlling the Pinout                        |      |

|           | Pin Locking                                   |      |

|           | Guide Files                                   | 3-1  |

|           | Pin Assignment                                |      |

|           | Constraints Editor                            |      |

|           | LOC Attribute Ignoring the LOC Attribute      |      |

|           |                                               |      |

| Function Block and Macrocell Assignment              | 3-9  |

|------------------------------------------------------|------|

| Prohibiting the Use of Device Pins                   | 3-9  |

| Pin Assignment Precautions                           |      |

| Controlling Logic Optimization                       | 3-10 |

| Collapsing Product Term Limit                        |      |

| Controlling Pterm Limits in Design Manager           | 3-11 |

| If the Path Delay is Not Satisfactory                | 3-11 |

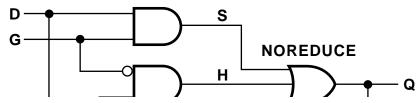

| Preventing Collapsing of a Logic Node                | 3-11 |

| Forcing Collapsing of a Logic Node                   | 3-12 |

| Multilevel Logic Optimization                        | 3-12 |

| Setting Multilevel Logic Optimization                | 3-13 |

| Controlling Timing Paths                             | 3-14 |

| Timing Optimization                                  | 3-14 |

| Timing Specifications                                | 3-15 |

| Entering Timing Specifications using the             |      |

| Constraints Editor                                   | 3-15 |

| From the Global Tab Window                           |      |

| Clock Period                                         | 3-16 |

| Pad to Setup                                         | 3-17 |

| Clock to Pad                                         |      |

| Pad to Pad                                           | 3-18 |

| From the Ports Tab Window                            |      |

| Pad to Setup                                         |      |

| Clock to Pad                                         | 3-18 |

| Slow/Fast Path Exceptions (FROM/THRU/TO)             | 3-19 |

| Entering Timing Specifications in a Schematic        | 3-19 |

| Entering Timing Specifications in a Constraints File | 3-21 |

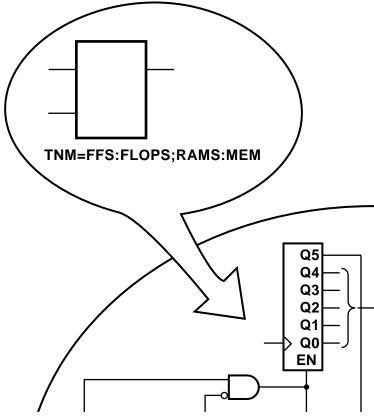

| Specifying Groups in TS Attributes                   |      |

| Using Predefined Groups                              | 3-21 |

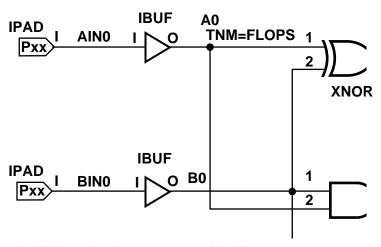

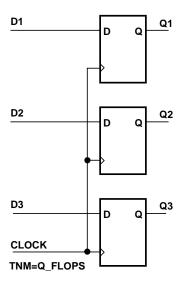

| Creating User-Defined Groups Using TNMs              |      |

| Creating New Groups from Existing Groups             | 3-28 |

| Combining Multiple Groups into One                   | 3-30 |

| Creating Groups by Exclusion                         | 3-30 |

| Defining Flip-Flop Subgroups by Clock Sense          | 3-31 |

| Creating Groups by Pattern Matching                  |      |

| Basic TIMESPEC Syntax                                | 3-33 |

| Specifying Time Delay in TS Attributes               | 3-34 |

| Specifying a TS Attribute Delay in Terms of Another  | 3-34 |

| Setting TIMESPEC Priorities                          | 3-35 |

| Defining a Clock Period                              | 3-35 |

| Specifying Setup Time Using the OFFSET Constraint    | 3-36 |

|            | Specifying Clock-to-Output Delay Using the |            |

|------------|--------------------------------------------|------------|

|            | OFFSET Constraint                          | 3-37       |

|            | Constraints Priority                       | 3-37       |

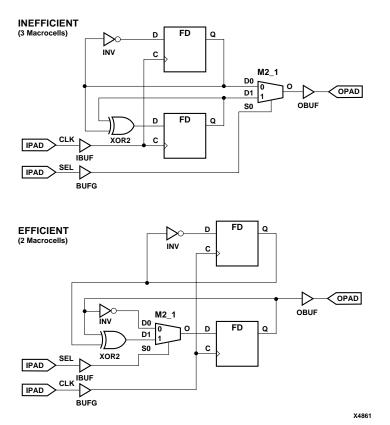

|            | Reducing Levels of Logic                   | 3-38       |

|            | Controlling XC9500 Local Feedback Routing  | 3-39       |

| Chapter 4  | Design Applications                        | 4-1        |

|            | Read-Back Registers                        | 4-1        |

|            | Bidirectional Signals and Buses            | 4-2        |

|            | Multiplexing Tristate Signals              | 4-3        |

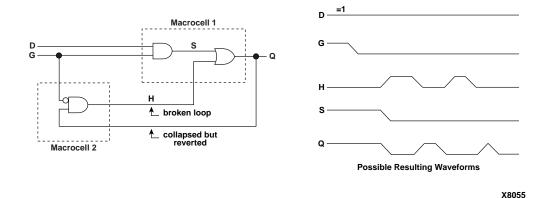

|            | Combinatorial Feedback Loops               |            |

| Appendix A | Attributes                                 | <b>A-1</b> |

|            | Introduction                               | A-1        |

|            | Inputs to Global Nets — BUFG               |            |

|            | Applicable Elements                        |            |

|            | Description                                |            |

|            | Syntax                                     |            |

|            | Schematic                                  |            |

|            | UCF/NCF file                               | <b>A-2</b> |

|            | Collapsing a Node — COLLAPSE               | A-2        |

|            | Applicable Elements                        | A-2        |

|            | Description                                | A-2        |

|            | Syntax                                     | A-3        |

|            | Schematic                                  |            |

|            | UCF/NCF file                               | A-3        |

|            | Target Device Selection — PART             |            |

|            | Applicable Elements                        |            |

|            | Description                                |            |

|            | Syntax                                     |            |

|            | Schematic                                  | A-3        |

|            | Clock Cycle Time — PERIOD                  | A-4        |

|            | Applicable Elements                        |            |

|            | Description                                |            |

|            | Syntax                                     |            |

|            | Schematic                                  |            |

|            | UCF/NCF file                               |            |

|            | Constraints Editor                         |            |

|            | Behavioral Modules — FILE                  |            |

|            | Applicable Elements                        |            |

|            | Description                                | A-5        |

| Syntax                                  | A-5  |

|-----------------------------------------|------|

| Schematic                               |      |

| Pin and Function Block Assignment — LOC | A-5  |

| Applicable Elements                     | A-5  |

| Applicable Elements  Description        | A-5  |

| Syntax                                  | A-5  |

| Schematic                               |      |

| UCF/NCF File                            | A-6  |

| Contraints Editor                       | Δ-6  |

| Pin Reservation — PROHIBIT              | Δ-6  |

| Applicable Elements                     | Δ-6  |

| Description                             |      |

| Syntax                                  |      |

| Schematic                               |      |

| UCF/NCF File                            |      |

| Constraints Editor                      |      |

| Power Setting — PWR_MODE                | A-1  |

|                                         |      |

| Applicable Elements                     | A-/  |

| Description                             |      |

| Syntax                                  |      |

| Schematic                               |      |

| UCF/NCF                                 |      |

| Preserving a Node — KEEP                |      |

| Applicable Elements                     | A-8  |

| Description                             | A-8  |

| Syntax                                  |      |

| Schematic                               |      |

| UCF/NCF                                 | A-8  |

| Register Preload State — INIT           |      |

| Applicable Elements                     | A-8  |

| Description                             | A-8  |

| Syntax                                  |      |

| Schematic                               |      |

| UCF                                     | A-9  |

| Output Slew Rate — FAST, SLOW           |      |

| Applicable Elements                     | A-9  |

| Description                             | A-9  |

| Syntax                                  |      |

| Schematic                               | A-9  |

| UCF/NCF file                            | A-10 |

| Constraint Editor                       | A-10 |

| A-10   |

|--------|

| A-10   |

| A-11   |

| A-11   |

| A-11   |

| A-11   |

| A-12   |

| A-13   |

| A-13   |

| s A-13 |

| A-13   |

| A-13   |

| A-13   |

| A-13   |

| A-13   |

| B-1    |

| C-1    |

| C-1    |

| C-1    |

| C-2    |

| C-5    |

| r C-5  |

| C-6    |

| D-1    |

| D-1    |

| D-1    |

| D-2    |

|        |

| NGD2EDIF                           | D-3 |

|------------------------------------|-----|

| Syntax                             | D-3 |

| Options                            | D-3 |

| NGD2VHDL                           | D-4 |

| Syntax D                           | 4   |

| Options                            |     |

| NGD2VER                            | D-5 |

| Syntax                             | D-5 |

| Options                            |     |

| Simulating Power-On Initialization |     |

## Chapter 1

## Getting Started with Schematic Design

This chapter will help you quickly understand how to develop a schematic-based CPLD design using the Xilinx design implementation software (fitter). A brief schematic design example is included, illustrating device-independent schematic design entry and simulation processes. This section in this chapter include:

- "Overview of Schematic Design Methods" section

- "Design Flow Summary" section

- "Schematic Design Flow Example" section

## **Overview of Schematic Design Methods**

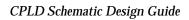

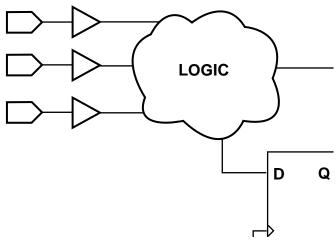

A schematic design defines the functionality of a logic circuit using one or more schematic files, each of which contains components from a Xilinx-supplied library, such as gates, flip-flops and building-block functions similar to 74xx TTL devices. Schematics can also contain "custom" symbols for which you define the functionality using behavioral modules (similar to PAL devices). Behavioral modules are discussed fully in the "Design Entry Techniques" chapter. The following figure summarizes the design flow.

Figure 1-1 Basic Schematic Design Flow

Currently, the Viewlogic, Mentor and Cadence software packages are directly supported by the Xilinx CPLD library and interface for CPLD design entry and simulation. Xilinx also provides the Foundation development system. Other compatible interfaces and CPLD libraries may be available from their manufacturers.

## **Design Flow Summary**

The Design Manager/Flow Engine takes EDIF netlist, XNF or PLD files from your design tool and fits them onto Xilinx devices. You can select a specific device or let the Design Manager select a device for you, based on the most economical solution that will satisfy the functional and timing parameters of the design.

### **Generated Reports**

By default the fitter produces the following significant output files:

- Fitting report (*design\_name*.rpt) lists summary and detailed information about the logic and I/O pin resources used by the design, including the pinout, error and warning messages, and Boolean equations representing the implemented logic.

- Static timing report (design\_name.tim) shows a summary report of worst-case timing for all paths in the design; optionally includes a complete listing of all delays on each individual path in the design.

- Guide file (design\_name.gyd) contains all resulting pinout information required to reproduce the current pinout if the "pinfreeze" option is specified during the next invocation of the cpld command for the same design name. (The Guide file is written only upon successful completion of the fitter.)

- Programming file (design\_name.jed for XC9000) is a JEDECformatted (9k) programming file to be down-loaded into the cpld device.

- Timing simulation database (design\_name.nga) a binary database representing the implemented logic of the design, including all delays, consisting of Xilinx simulation model primitives (simprims).

The Design Manager contains a Report Browser for examining selected reports. If you have already run the fitter, the Report Browser contains the Fitting Report and the Translation Report, and, if you have selected timing simulation options, it also contains simulation reports. To access the Report Browser from the Design Manager:

```

Utilities \rightarrow Report Browser

```

After the Report Browser displays, to read any of the reports simply double-click the appropriate report icon.

### **Timing Simulation**

The Design Manager optionally produces timing simulation data when you implement your design, and produces either an EDIF, VHDL or Verilog HDL formatted netlist for your simulator..

## **Schematic Design Flow Example**

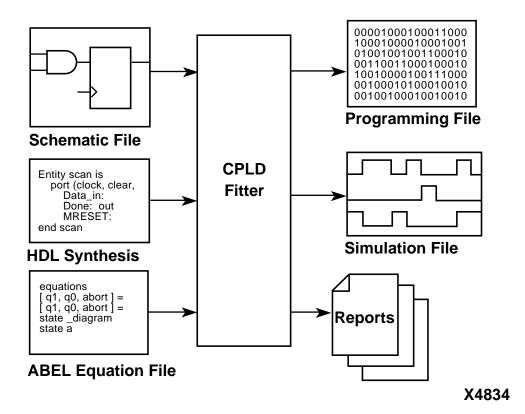

This section runs through the entire schematic design process, from creating a design to programming and simulating the design. The following device-independent design, a 4-bit Johnson counter, is used as an example:

Figure 1-2 Example 4-Bit Johnson Counter Design

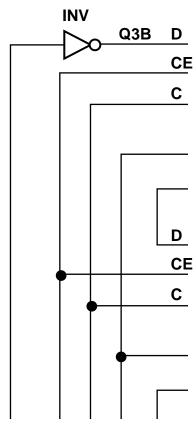

Simulation results for this design are shown in the "Example Viewlogic Functional Simulation Results" figure.

The design entry and simulation steps are summarized for Viewlogic and Mentor software. Other supported schematic design software

has similar procedures; refer to the appropriate Xilinx interface guide, if applicable, or the manufacturer's documentation.

YROF

Figure 1-3 Example Viewlogic Functional Simulation Results

### **Configuring the Design Entry Tool**

Many design entry tools have a project management facility that you can use to create a working directory for your design and to select the vendor component libraries to use in your design.

#### **Workview Office Project Manager**

Call up the Viewlogic Project Manager by selecting the Project Manager icon in the Workview Office icon group. Create a new project named jcount.

$\mathtt{File} o \mathtt{New}$

- 2. Select a directory and name the new project jcount.

- 3. Call up the libraries you need to create your design.

Project → Libraries...

- The Library Search Order dialog box displays. Use this tool to add the XC9000 library, plus the builtin and simprims libraries.

- 5. Use the Browse key to select directories and the Add key to add libraries. For example, browse to installation\_path/viewlog/data/xc9000 (for XC9500 target devices) where installation\_path is the root directory where the Xilinx software package was installed. Then click Add and the xc9000 libraries

will be added to the list. When you have all the libraries you need for the project, click **OK**.

#### Viewlogic On Workstations

- To create a working directory for your design in Viewlogic's Powerview, use the Project → Create command.

- 2. Configure the design entry tool to access the Xilinx CPLD component library for schematics you develop in the project you just created. In Powerview, use the Project → Search Order command to open a dialog window listing the configured libraries. On the first available library line, enter the directory path where the CPLD Viewlogic library is installed on your system. For example, enter installation\_path/viewlog/data/xc9000 (for XC9500 target devices), where installation\_path is the root directory where the Xilinx software package was installed. Under the "Library" column, enter xC9000, which is also known as the library alias. Under the Type column, select Megafile (compressed read-only format).

- 3. If you are not using the Viewlogic project manager, you can make a copy of the viewdraw.ini file in your project directory (copied from the Viewlogic standard directory) and add one of the following lines to the end of the file:

DIR [m] installation\_path/viewlog/data/xc9000 (xc9000)

where *installation\_path* is the root directory where the Xilinx software package was installed.

4. If you plan to simulate using Viewsim, you also need to include the Xilinx "simprims" and Viewlogic "builtin" library in the Search Order window or the viewdraw.ini file.

**DIR** [m] installation\_path/viewlog/data/simprims (simprims)

DIR [m] installation\_path/viewlog/data/builtin (builtin)

#### Mentor

- Call up the Mentor Design Manager as follows: pld dmgr

- Select the Tools icon. Then go to Tools program group and select pld\_da (Design Architect).

### **Drawing the Design**

- 1. Invoke the schematic drawing tool and draw the design.

- If you are using Workview Office or Powerview, invoke the ViewDraw tool.

- If you are using Mentor Graphics you would invoke pld\_da (Design Architect).

- 2. If you prefer to use the completed schematic shown in "Example 4-bit Johnson Counter" figure as a sample design, copy the jcount schematic file from the examples directory of the Xilinx software.

- For Viewlogic, copy all files and subdirectories under the installation\_path\viewlog\tutorial\jcount directory into your local directory (the schematic file is jcount.1 under the sch subdirectory).

- For Mentor select the Find Comp icon in the Design Architect and browse to installation\_path\mentor\tutorial\jcount, then select jcount.

When drawing a schematic representing a CPLD device, or any sub-sheet in a CPLD design, you should not use any symbols from any other library than the Xilinx XC9000 library. For example, be careful not to use symbols from the Viewlogic builtin library. You may, however, create your own custom symbols representing sub-sheets (hierarchical schematics) or behavioral modules, as described in the "Design Entry Techniques" chapter.

It is important that you label the nets that represent device input/output pins in your design. These are the nets connecting between IPAD and IBUF symbols, and between OBUF and OPAD symbols. These names appear in the fitter reports as your pin names and are used as your top-level signal names during timing simulation, after design implementation.

3. Save your schematic when finished. The Viewdraw Write command performs schematic rule checking and writes a "wirelist" file in the wir directory (wir/jcount.1).

### **Performing Functional Simulation (Optional)**

Xilinx schematic capture libraries contain simulation models allowing you to perform functional simulation directly from your

ı

schematic. In most libraries, models for all registered symbols contain a global signal named PRLD which, when pulsed high, initializes all the flip-flops inside the symbol's model. Remember to pulse the PRLD signal high and drive all your top-level input signals (pins) to valid logic levels before running your simulation vectors.

#### **Viewlogic**

If you are using Viewlogic, Xilinx provides a Viewsim command file for the jcount design that can be found in <code>installation\_path/viewlog/tutorial/jcount/jcount.cmd</code>. The JCOUNT design is simulated using the following Viewsim commands:

```

vector Q Q[3:0]

wave jcount.wfm CLK CE CLR Q

clock c 1 0

step 50ns

h prld

h CE

1 CLR

cycle

1 prld

cycle 5

1 CE

cycle 2

h CE

cycle 5

h CLR

cycle 2

1 CLR

cycle 3

```

The wave command automatically invokes a ViewTrace window which displays the input and output simulation waveforms graphically.

#### Mentor

You can functionally simulate XNF or EDIF based designs by using pld\_xnf2sim or pld\_edif2sim to convert the designs to a Mentor simulation model. The EDIF design must be Xilinx compatible and expressed in Unified Library components.

Performing functional simulation on a pure schematic design consists of creating a viewpoint in pld\_dve from the schematic that you

created in Design Architect and using pld\_quicksim to simulate the design. For more information see the *Mentor Graphics Interface Guide*.

### Implementing the Design

Before implementing the design, your schematic must first be translated into an EDIF 2.0.0 formatted netlist. When netlisting, make sure the netlist hierarchy stops at the Xilinx library primitives and does not expand into any functional simulation models that may exist beneath the Xilinx primitive symbols.

#### Creating an EDIF Netlist

From Viewlogic Workview Office:

1. Go to the ViewDraw tool and select:

$\mathtt{Tools} o \mathtt{Export} \ \mathtt{EDIF}$

- The EDIF Interfaces Dialog Box appears. Select the EDIF

Netlist Writer tab and Browse to the jcount.1 schematic.

Enter xilinx in the level field.

- To create the .edn file click once on Apply.

For Viewlogic Powerview:

- Invoke the edifneto command

- 2. Specify "XILINX" as the "level" attribute ("-1 xilinx" option on the edifneto command line).

From *Mentor* you must convert to EDIF with the pld\_men2edif utility before implementing the design with the Design Manager.

To convert your design to EDIF, follow these steps.

- 1. In the Mentor Design Manager, double-click the left mouse button on the pld\_men2edif icon.

- The dialog box labeled "Mentor to EDIF Netlist appears.

- 2. In the Component Name field, enter the component name, or click Navigator to browse a list of design names.

- 3. In the From Viewpoint field, you can enter the viewpoint name if you do not want to use the default viewpoint. Alternatively, in step 2 you can select a viewpoint under the component.

- 4. Select the appropriate architecture for your design in the PLD Technology field.

- 5. Select the appropriate Bus Dimension Separator Style.

This is important if you are merging components from other design-entry tools into a single design. Choosing a bus-index delimiter lets you insure that the bus-index delimiters that pld\_men2edif writes out are consistent with those of any other design-entry tools with which you are interfacing. Mentor EDIF uses parentheses. Synopsys EDIF uses angle brackets.

6. Click or.

Pld\_men2edif now produces an EDIF file that you can submit to the Xilinx Design Manager. The output name is component\_name.edif.

#### **Implementing from Design Manager**

Start the Xilinx Design Manager. From the Windows Program Manager click the Design Manager icon. If you are using the UNIX command line enter the following command.

dsgnmgr

2. From the Design Manager, create a new project and select jcount.edn as its input.

File  $\rightarrow$  New Project

- 3. The New Project dialog box appears. Select Browse for Input Design and find jcount.edn, then click OK. The project should appear in the Design Manager.

- Implement the design.

$\mathtt{Design} \to \mathtt{Implement}$

The Implement dialog box appears. This box allows you to select a specific Xilinx device to implement your design.

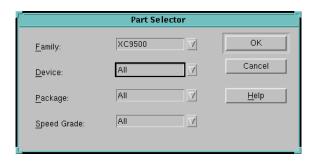

- Click once on Select and select for XC9500, XC9500XL or XC9500XV Family; leave Device, Package and Speed Grade set to AUTO.

- 6. Click **OK** when you have finished.

- 7. Click Run to implement the design.

### **Examining the Reports**

Examine the reports to verify that the design was implemented as you expected. The following report files (plain text) are automatically produced by the fitter. If you are using a Design Manager you may select a report from the report browser as follows:

#### Utilities $\rightarrow$ Report Browser

or select the report browser icon. The following reports are most useful for schematic designs:

#### Figure 1-4 Report Browser

- Fitter Report (jcount.rpt)- The fitter report shows the device resources used by the design, how the external nets in your design were mapped to the device pins, and the physical allocation of all device resources.

- Timing Report (jcount.tim) A timing summary report shows the calculated worst-case timing for the logic paths in your design.

### **Performing Timing Simulation**

To perform timing simulation you must extract a new EDIF netlist from the implemented design. To avoid overwriting, you may want to specify and output filename different than your design entry netlist.

The Design Manager optionally produces timing simulation data when you implement your design.

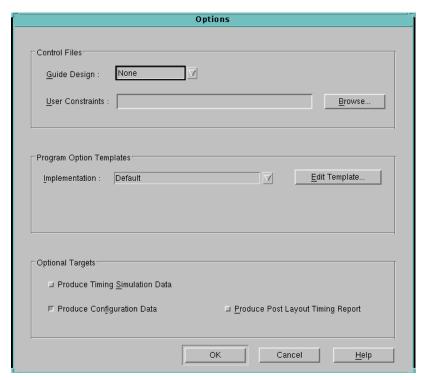

1. To produce timing data go to the options menu:

$\mathtt{Design} \to \mathtt{Implement}$

2. The Implementation menu will appear. Click once on the Options key to get the Options dialog box.

- 3. Select Produce Timing Simulation Data.

- 4. Go to the Interface template and select EDIF as the simulation netlist format. When the fitter runs it generates the appropriate data. If you have already run the fitter, go back to the Flow Engine; a Timing block will appear in the flow.

- 5. Press the forward arrow to resume the program from the Fit block.

#### Workview Office and Powerview

In most cases, you can use the same command file you used during functional simulation to perform the timing simulation. You may need to make minor adjustments to the command file used to functionally simulate the design before it can be used to perform a timing simulation.

The typical procedure for performing a timing simulation is as follows.

- Import the EDIF file with timing information produced by the fitter to create a wire-list file.

- 2. Create the timing simulation network (VSM file).

- 3. Start ViewSim.

- 4. Load the VSM file into ViewSim.

- 5. Simulate the device's startup sequence.

- Execute the command file used during functional simulation. For the JCOUNT sample design, a Viewsim command file can be found in *installation\_path*/viewlog/tutorial/jcount/jcount.cmd

- 7. VewTrace is automatically opened in response to the WAVE command. View the waveforms produced by the simulation.

- 8. Repeat steps 5 and 6 as necessary to verify the timing information.

See the *Viewlogic Interface Guide* for detailed information on each of the above steps.

#### Mentor

During design implementation, the Xilinx Design Manager can produce an EDIF (EDN) file. For EDIF files, the process of timing simulation consists of converting the EDIF netlist to a Mentor EDDM model, creating a component and a viewpoint, and simulating the design with pld\_quicksim.

- Double-click the left mouse button on the pld\_edif2tim icon in the Mentor Design Manager Tools window.

- The dialog box labeled EDIF to Mentor Eddm Sing Object appears.

- 2. Enter the name of the EDN file in the EDIF Input File field, or click Navigator to browse the available files.

The component created from the EDN file is put into a design library called *my\_design\_lib*. If you have already implemented your design at least once, this directory already exists. If you don't wish to copy over it, move it to another directory before proceding.

- Click OK.

- Invoke DVE, by double-clicking the left mouse button on the pld\_dve icon in the Mentor Design Manager Tools window.

The Pld\_dve Dialog Box appears.

- 5. Enter the top-level component name created by pld\_edif2tim in the my\_design\_lib directory.

- 6. Use the Navigate button to navigate all the way down to the "default" viewpoint and select the viewpoint.

- Select the Simulation Button.

- 8. Select the appropriate technology from the PLD Technology box.

- Click OK.

You can now submit the design to pld\_quicksim for timing simulation.

1. To invoke pld\_quicksim, double-click the left mouse button on the pld\_quicksim icon in the Design Manger Tools window.

The pld\_quicksim dialog box appears. For more detailed information on the dialog box options, refer to the Mentor Graphics documentation.

- 2. In the Design field, enter the name of the top-level design created by pld\_edif2tim.

- 3. In the Select Desired Mode field, select Cross-Probing.

Normally, you select cross-probing for back-end EDDM designs but not for front-end designs. You can only cross-probe back-end designs that contain either pure schematic or schematics that contain EDDM hierarchical models. You cannot cross-probe designs written in HDL or that contain HDL models.

**Warning:** In order for cross-probing to work, other sessions of Design Viewpoint Editor and QuickSim must be closed. Otherwise, the interprocess communication gets confused. This includes another user's session invoked by rlogin from another workstation.

- 4. Set the timing modes as desired.

- 5. Click ox.

Pld\_quicksim now simulates the design. The QuickSim graphical user interface appears. If you selected cross-probing, DVE is invoked as well.

- 6. In DVE, open the viewpoint of the front-end schematic design, that is, the viewpoint submitted to pld\_men2edif.

- 7. Open the sheet of the design, and select signals that you wish to trace.

These signals are automatically added to the QuickSim trace window. If you have a file that sets up your trace window and stimulus, use that instead. Any signals selected in the trace window will select the same on the schematic on which they reside in the DVE window. If such sheets have not been opened in DVE yet, you must open them to see the selections.

#### **Device Programming**

The fitter automatically creates a JEDEC programming file, jcount.jed, whenever a design is successfully implemented. Once you are satisfied with the results of the fitter (reports and timing simula-

tion), you can download the programming file to the device using the techniques described in the *JTAG Programmer Guide*.

## **Design Entry Techniques**

This chapter discusses the fundamental techniques for expressing logic in a schematic design for CPLDs. It concentrates mainly on the symbols you place in your schematic and how you interconnect them. It also explains how to retarget an existing schematic for an FPGA design to a CPLD. This chapter includes the following sections:

- "Library Symbols" section

- "Input/Output Buffers" section

- "LogiBlox Modules" section

- "Behavioral Modules" section

- "Hierarchical Design" section

- "Retargeting a Design From a Different Family" section

### **Library Symbols**

The Xilinx XC9000 library contains all component symbols used by the Xilinx XC9500, XC9500XL, and XC9500XV device families. While most symbols of the library are common to all families, there are some symbols which are specific to CPLDs.

Physically, each major Xilinx device family (for example, 3000, 4000, 9000) has its own schematic library, implemented for each of the supported schematic entry tools. For each tool, there is a library directory for the XC9000 device family, which supports XC9500, XC9500XL, and XC9500XV devices. When a library component is supported by multiple device families, its symbol appears in each of the corresponding library directories.

When a component of the same name appears in multiple family libraries, it has the same functionality and graphic symbol body, and

similarly named pins. However, the component's implementation, including whether the symbol is a primitive or macro (with underlying schematic), may vary between families. Maintaining consistent functionality and "footprint" facilitates retargeting existing schematic designs between Xilinx device families. The *Libraries Guide* shows the applicability of each library symbol to each of the Xilinx device families.

When drawing a schematic representing a CPLD device, or any subsheet in a CPLD design, you should not use any symbols from any other library than the one for your target device family. For example, be careful not to use symbols that belong to a CAE tool's simulation modelling library.

### **Specific Components**

To make your design device-independent, use only the symbols common to all Xilinx device families in which you are interested. The design implementation software automatically maps the symbols in your design onto the chosen target device. Creating a device-independent design allows you to easily test your design with different Xilinx devices.

For example, if you want to create a schematic which can be migrated to different Xilinx device families without modification, you should use the generic IBUF symbol instead of device-specific input buffers (like BUFGSR) and allow the fitter to automatically allocate global set/reset resources.

### **Primitives, Macros and User-Generated Symbols**

The following types of symbols can appear in your schematic:

- · Library primitives

- · Library macros

- User macros (including hierarchical sheet symbols)

- Behavioral modules

- LogiBLOX modules

The library contains the first two types of components: primitives and library macros. Primitives are those symbols recognized directly by the implementation software such as pads, gates, flip-flops and

buffers. Library macros are symbols functionally defined by macro schematics contained in the library. Macro schematics contain primitives and sometimes other macros. Library macros have pre-defined functionality, but often their implementation is subject to the optimizations performed by the fitter software. Macros are always expanded into the netlist during schematic-to-netlist translation before the netlist is read by the fitter. EDIF netlists may either be in hierarchical or flattened form; this has no impact on the fitter's performance.

User macros are custom symbols generated by the user which are functionally defined by user-generated macro schematics. User macro symbols and schematics can be stored in your project directory or in a user library directory that you create. User macro schematics can consist of any mixture of the four types of symbols listed previously.

You can create user macros to represent frequently used logic functions and instantiate them in one or more designs. It is often convenient to copy a Xilinx CPLD library macro symbol and schematic to your project directory as a template, then rename the symbol and schematic, and modify the symbol pins and schematic to suit your needs. You should not, however, modify any of the Xilinx CPLD library macros themselves or store new user macros in the Xilinx CPLD library directory.

You can add hierarchical structure to a large design by partitioning your logic into multiple schematic sheets. You then create user symbols to represent the schematic sub-sheets in the same manner as you would create user macro symbols. Your schematic partitioning has no effect on the implementation or optimization of your design by the fitter.

Behavioral modules are user-generated custom symbols functionally defined by some logic description other than a schematic. Typically, logic descriptions defining behavioral modules are expressed in Boolean equations or HDL, and processed by a PLD compiler (like XABEL) or a synthesis tool prior to running the fitter. Behavioral modules are discussed later in this chapter.

LogiBLOX modules are high-level, customizable library macros that are available for some schematic entry tools. LogiBLOX modules are described later in this chapter.

## **Power and Ground Signals**

Unused inputs on symbols should not be left unconnected. You should never assume a default value for any unconnected symbol input except basic logic gates such as AND or OR, or asynchronous clear (CLR) or preset (PRE) inputs on flip-flops and other registered macros. Unconnected AND-gate, OR-gate, CLR and PRE inputs are simply discarded, as if the component had fewer inputs.

If a control input to a library macro is left unconnected, the resulting behavior may be different than what you would expect. In some cases, the resulting behavior may be different than if the input were tied either High or Low. If you leave a macro input unconnected, the fitter is usually able to detect it and issue a warning. Timing simulation after fitting will exhibit the actual resulting behavior.

Unused inputs should be tied to a constant High or Low logic level in the schematic. Use the VCC or GND symbol from the library to source a constant logic High or Low value.

# **Input/Output Buffers**

This section discusses techniques for specifying device I/O pins using both general-purpose and special-purpose input/output buffer symbols.

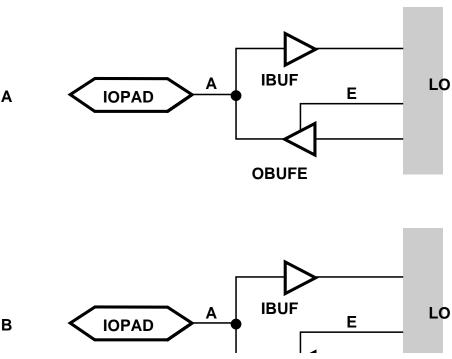

## Inputs, Outputs, and Bidirectionals

To represent an ordinary device input, use an IPAD connected to one IBUF symbol. The IBUF can then connect to any number of on-chip logic symbols. An I/O pin of the CPLD device will be allocated to receive the input, and its output driver will be permanently disabled.

To represent an ordinary device output, use an OBUF that is driven by exactly one on-chip logic source. Connect the output of the OBUF to an OPAD symbol. To specify a tristate device output, use an OBUFE or OBUFT instead of the OBUF, and connect its enable/disable input to any on-chip logic source. An I/O pin will be allocated to drive the signal, either always active (if OBUF) or controlled by your enable/disable signal, and the input received by the device pin will be ignored.

To represent a bidirectional device I/O, use an OBUFE or OBUFT whose output is connected to both an IOPAD symbol and to the input of an IBUF, as shown in the "Bidirectional I/O Pin" figure.

Figure 2-1 Bidirectional I/O Pin

It is important that you label the nets that represent device input/output pins in your design. These are the nets connecting between IPAD and IBUF symbols, and between OBUF and OPAD symbols. These names appear in the fitter reports as your pin names and are used as signal names during simulation.

**Note:** Do not use the reserved names "GND," "VCC," "PRLD" or "MRESET" as labels for any nets or component instances in your design.

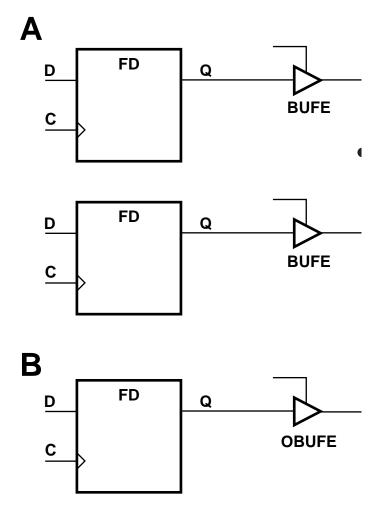

## **Clock Inputs**

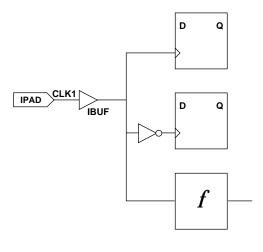

To use a device input as a clock source, you can simply connect an IBUF to the clock input of one or more flip-flops in your design. The fitter automatically uses one of the global clock pins (GCK) of the CPLD whenever possible.

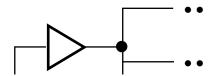

A clock input signal may pass through an inverter to perform negative-edge clocking and the fitter can still use a global clock pin to implement it. The same global clock input may even be used both inverted and non-inverted to clock different flip-flops on opposite edges of the clock signal, as shown in "Input CLK1 can be Optimized onto a Global Clock Pin (GCK)" figure. Global clock inputs may also be used as ordinary input signals to other logic elsewhere in the design.

X8058

Figure 2-2 Input CLK1 can be Optimized onto a Global Clock Pin (GCK)

If a device input passes through any logic function (other than an inverter) before it is used as a clock by any flip-flop, the input cannot be routed using the global clock path. Instead, the clock signal will be routed through the logic array for all flip-flops clocked by such a device input.

There are a limited number of global clock pins on each CPLD device (consult the device data sheet). If you need to explicitly control the use of global clock pins, you can use the BUFG symbol in place of an IBUF. You could alternatively apply the BUFG=CLK attribute to an IBUF symbol or the pad net.

The global clock pins provide much shorter clock-to-output delays than clocks routed through the logic array. Routing a clock through the logic array also uses up one extra p-term for each flip-flop.

You can prevent the fitter from automatically mapping IBUF symbols to the global clock pins.

- On the Design Manager graphical interface, go to the Flow Engine and select Setup → Options

- 2. The Design Implementation Option menu appears. Select Edit Template

- 3. Then select Basic Options

- 4. Place a check on the Off box adjacent to Use Global Clocks.

If global clock optimization is disabled, IBUF inputs used as clocks always pass through the logic array. You can still use BUFG symbols or the BUFG=CLK attribute to explicitly specify global clock inputs.

## **Output Enable Signals**

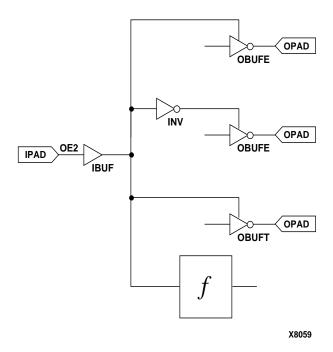

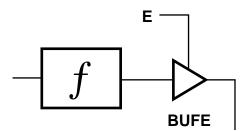

To use a device input to control tristate device outputs, you can simply connect an IBUF to the enable/disable input of one or more OBUFE or OBUFT symbols in your design. The fitter automatically uses one of the global tristate control pins (GTS) of the CPLD whenever possible.

A global tristate control input signal may pass through an inverter or control the disable input (T) of an OBUFT symbol to perform an active-low output-enable. The same tristate control input may even be used both inverted and non-inverted to enable alternate groups of device outputs, as shown in the "Input OE2 can be Optimized onto a Global Tristate Control Pin (GTS)" figure. Global tristate control inputs may also be used as ordinary input signals to other logic elsewhere in the design.

Figure 2-3 Input OE2 can be Optimized onto a Global Tristate Control Pin (GTS)

If a device input passes through any logic function (other than an inverter) before it is used as a tristate control by any output, the input cannot be routed using the global tristate control path. Instead, the output enable signal is routed through the logic array, for all device outputs controlled by such an input.

There are a limited number of global tristate control pins on each XC9500 device (consult the device data sheet). If you need to explicitly control the use of global tristate control pins, you can use the BUFGTS symbol. You can alternatively apply the attribute BUFG=OE to an IBUF symbol or the pad net.

The global tristate control pins provide much shorter input-tooutput-enable delays than tristate controls routed through the logic array. Routing a tristate control signal through the logic array also uses up one extra p-term for each output. You can prevent the fitter from automatically using the global tristate control pins.

- In the Design Manager, go to the Flow Engine and select Setup

→ Options

- 2. The Design Implementation Option menu appears. Select Edit Template

- Then select Basic Options

- 4. Disable the box adjacent to Use Global Output Enables.

If global output enable optimization is disabled, IBUF inputs used for tristate control always pass through the logic array. You can still use BUFGTS symbols or the BUFG=OE attribute to explicitly specify global tristate control inputs.

## **Asynchronous Clear and Preset**

To use a device input as an asynchronous clear or preset source, you can simply connect an IBUF to the CLR or PRE input of one or more flip-flops in your design. The fitter automatically uses the global set/reset pin (GSR) of the CPLD whenever possible. A global set/reset input signal may pass through an inverter to perform active-low clear or preset. A global set/reset inputs may also be used as an ordinary input signal to other logic elsewhere in the design.

If a device input passes through any logic function other than an inverter before it is used as an asynchronous clear or preset by any flip-flop, the input cannot be routed using the global set/reset path. Instead, the clear or preset signal will be routed through the logic array for all flip-flops controlled by such an input. Routing a clear or preset through the logic array uses up one extra p-term for each flip-flop.

There is only one global set/reset pin on each XC9500 device. If you need to explicitly control the use of the global set/reset pin, you can use the BUFGSR symbol in place of an IBUF. You can alternatively apply the attribute BUFG=SR to an IBUF symbol or the pad net.

You can prevent the fitter from using the global set/reset pin. In the Design Manager, disable the Use Global Set/Reset option in the Basic Options template of the Flow Engine.

**Note:** If a flip-flop has both a clear and preset input and you assert both the clear and preset concurrently, its Q-output is unpredictable. This is because the fitter may arbitrarily invert the logic stored in a flip-flop to achieve better logic optimization. Individual clear and preset operations still produce the correct final logic state as dictated by the user design. Functional simulation does not accurately predict the ultimate behavior of the chip when clear and preset are asserted concurrently. Timing simulation, however, is performed after logic optimization and behaves exactly as the chip will when programmed.

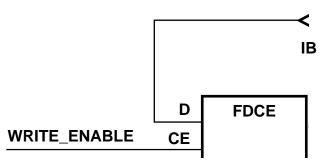

#### **Clock Enable**

When targeting an XC9500 device, any FDCE or FDPE primitives in your design will be expanded into an ordinary D-type flip-flop with its Q-feedback multiplexed into its D-input. This implementation will be similar to the way the FDCPE macro is expanded in the XC9000 schematic library.

When targeting an XC9500XL device, logic connected to the clock enable (CE) input of FDCE and FDPE primitives in your design will be unconditionally implemented using the clock enable p-term of the XC9500XL macrocell. Only the FDCE and FDPE primitives use the clock enable p-term.

If you use FDCE or FDPE components and target an XC9500XL device, you may find that the logic connected to the clock enable input on some components may not get optimized into the same macrocell as the flip-flop. The XC9500XL macrocell contains only a single product-term to implement clock enable input logic. The CPLD fitter does not attempt to transform your clock enable input logic onto the D-input of the flip-flop if it cannot be completely implemented using the clock enable p-term. In general, only primary inputs (device input pins or macrocell feedbacks), their complements or positive-logic AND-gate functions of primary inputs or their complements can be completely implemented using the p-term. If you connect a more complex logic function to the clock enable input of an FDCE or FDPE component and it does not get completely implemented on the clock enable p-term, your design may incur extra macrocell resources and combinatorial macrocell feedback delays.

If you have an existing CPLD schematic containing FDCE or FDPE components and you do not want the logic connected to the CE input of the components to be implemented using the clock enable p-term

in the XC9500XL macrocell, you can simply replace FDCE or FDPE components in your schematic with FDCPE components from the XC9000 library. The FDCPE component is a macro which always gets expanded into a simple D-type flip-flop with its Q-feedback multiplexed into its D-input; the clock enable p-term is not used. After substitution, the unconnected PRE or CLR input to the FDCPE is automatically trimmed away by the CPLD fitter.

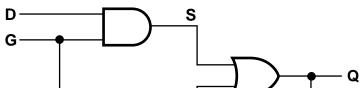

## **Tristate Multiplexing**

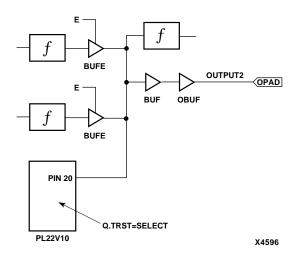

XC9500 CPLD devices can emulate tristate bussing between on-chip signal sources by gating the macrocell feedback to the FastCON-NECT structure. (Macrocell feedback signals are never physically in a high-impedance state.) Multiple feedbacks emulating tristate signals can be wire-ANDed in the FastCONNECT to emulate bussing and tristate multiplexing. When an on-chip tristate signal is "disabled", the macrocell feedback is forced High so that it does not affect the wire-AND. The signal on the wire-AND will therefore follow the logic value of the "enabled" feedback.

To represent tristate multiplexing (bussing) in the schematic, tie together the outputs of multiple tristate buffer symbols, like BUFE and BUFT, as in the "Correct On-Chip Tristate Multiplexing" figure. You cannot, however, connect such tied signals directly to an output buffer; instead you must pass a tied signal through a logic symbol, like BUF, before driving an output port.

**Note:** XC9500XL does not support internal tristate bussing. Never use BUFE or BUFT components in an XC9500XL design. On-chip tristate bussing is supported by some of the FPGA device families.

Figure 2-4 Correct On-Chip Tristate Multiplexing

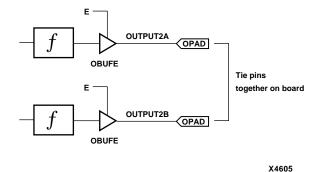

If your design calls for tristate bussing of multiple signals driven offchip, it may be better to output each signal source on its own tristate output pin and tie the pins together off-chip, as shown in the "Correct Off-Chip Tristate Multiplexing of CPLD Outputs" figure. You cannot connect more than one signal source to the same OBUF or OPAD, as shown in the "Incorrect Tristate Multiplexing of CPLD Outputs" figure.

**Note:** XC9500XL and XC9500XV devices do not support internal tristate bussing. Never use BUFE or BUFT components in an XC9500XL or XC9500XV design. On-chip tristate bussing is supported by some of the FPGA device families.

CORRECT

Figure 2-5 Correct Off-Chip Tristate Multiplexing of CPLD Outputs

### **INCORRECT**

Figure 2-6 Incorrect Tristate Multiplexing of CPLD Outputs

## **LogiBlox Modules**

LogiBLOX is a graphical interactive tool for creating high-level modules, such as counters, shift registers, and multiplexers. Logi-BLOX includes both a library of generic modules and a set of tools for customizing them. For detailed information see the *LogiBLOX User Guide*.

The modules you create with LogiBLOX can be used in designs generated with schematic editors from Aldec, Viewlogic, Mentor Graphics, and Cadence.

Use LogiBLOX modules whenever you need a customized version of a standard function. In contrast, a standard ready-made counter has a previously defined set of functions. If you want to use a counter with specific capabilities, you need to have available a library of different counters, one of which contains the functions you need. However, with a LogiBLOX counter, you start with a generic template and tailor its functionality to your needs.

You can use LogiBLOX to design your modules. The Module Selector is a graphical user interface. Use it to tailor modules to your requirements. This is the most common way to design modules in Logi-BLOX.

### **Program Inputs and Outputs**

The Module Selector is the LogiBLOX graphical user interface that you use to create a LogiBLOX module. Specifying a LogiBLOX module consists of a) selecting or deselecting optional pins on the symbol, and b) specifying various module attributes. The result is a module customized for a specific function.

After you complete the module specification, LogiBLOX uses its symbol generator, model generator, and netlist generator to create the following three outputs and store them in the current project directory:

- A schematic symbol for inclusion on the schematic

The symbol generator creates a symbol definition file that your third-party interface converts into a schematic symbol.

- A behavioral VHDL simulation model

The model generator creates a behavioral VHDL simulation model for the LogiBLOX module.

The behavioral model permits the design to be simulated immediately in those environments that support mixed schematic and behavioral simulation.

Verilog and EDIF gate-level netlists, produced as an alternative simulation medium

The netlist generator creates a gate-level netlist for the LogiBLOX module that is converted to the third-party's simulation format. These netlists permit immediate simulation of the design in gate-level simulation environments.

## **Schematic Design Flow**

To use the program in a schematic-based environment, follow these steps:

- 1. Invoke the Module Selector from within your design entry tool.

- Configure your project directory using the LogiBLOX Setup window.

- 3. Select a base module type (for example, Counter, Memory, or Shift-register)

- 4. Customize the module by selecting pins and specifying attributes.

- 5. After completely specifying a module, click on the OK button. Selecting OK initiates the generation of a schematic symbol and a simulation model for the selected module.

- 6. Place the module on your schematic.

- 7. Connect the LogiBLOX module to the other components on your schematic using ordinary nets, buses, or both.

- 8. Functionally simulate your design at any time.

- 9. Implement your design with the Xilinx implementation tools.

- 10. To simulate your design post-layout, convert your design to a timing netlist and use the back-annotation flow appropriate to your CAE tools.

## **Changing a Schematic Module**

To change a module that you have already placed on your schematic, select the module and invoke the Module Selector. The Module Selector displays the settings of the module that you want to edit.

### **Behavioral Modules**

Behavioral modules are user-generated symbols functionally defined by some logic description other than a schematic, typically Boolean equations or HDL. Some reasons why you may want to use behavioral modules in your schematic are:

- You may want to re-use existing design solutions that are expressed in Boolean equation or HDL form.

- It is often easier to express combinatorial logic functions and state machines using Boolean equations or HDL than using schematics.

The Xilinx CPLD fitter also accepts entirely behavioral designs which use no schematics. Similar to behavioral modules for schematic designs, behavioral designs are expressed using Boolean equations or HDL and compiled using a PLD compiler (like XABEL) or a logic synthesis tool. Unlike behavioral modules, behavioral designs contain all the device I/O port information in its behavioral description.

This manual describes only schematic-based designs and the behavioral modules which may be contained in them. The procedures for creating behavioral modules in CPLD schematics is essentially the same as for all other Xilinx device families.

### **Compiling Behavioral Logic**

The equation or HDL files defining behavioral modules must be compiled before they can be used by the fitter. There are a variety of PLD compilers and synthesis tools that support design entry for CPLD devices.

Behavioral compilers which are compatible with the CPLD fitter translate their logic descriptions into EDIF or XNF formatted netlists.

**Note:** Previous versions of the CPLD fitter used the PLUSASM equation language as an interchange language in place of XNF or EDIF for

I

some behavioral compilers, such as XABEL. PLUSASM is still recognized and processed by this version of the fitter for the sake of existing behavioral modules based on that interface. However, future versions of the software will not support PLUSASM and it should not be used when creating any new behavioral modules.

If the behavioral compiler tool supports the development of completely behavioral designs, make sure you select the appropriate mode of operation or compilation flow for producing logic modules, not stand-alone designs. The netlist produced by the compiler must not contain device I/O pin information. If any of the terminal nodes (inputs or outputs) of your behavioral module are to be connected to CPLD device pins, you must use IBUF and OBUF symbols in your schematic.

**Note:** If you are using a synthesis tool to prepare a behavioral module, make sure you target the appropriate CPLD technology library.

Your compiled behavioral module file is normally stored in your project directory. You can also copy it to a user library directory if you want to use it for more than one project.

## **Behavioral Module Symbols in Schematics**

Using a behavioral module in a schematic design involves creating a symbol to represent your logic, placing the symbol into your schematic and applying necessary attributes to identify the logic-defining file.

Use the symbol editing facility of your schematic entry tool to create a symbol representing your behavioral logic. Generally, the name of your symbol will be the name of the behavioral module, although this is not mandatory.

Place a pin on your symbol for each terminal node (input or output port) in your behavioral design that needs to be connected to other logic or I/O ports in your schematic. "Buried" nodes that connect only between logic functions within the behavioral module do not require pins on your symbol.

Some tools have commands or utilities that automatically generate symbols based on the terminal nodes defined in your behavioral module.

ı

I

2. Some schematic entry tools distinguish between two types of symbols: primitive symbols (sometimes called "module") and hierarchical symbols (sometimes called "composite") that link to schematics beneath them. When creating a symbol to represent a behavioral module, create it as a primitive symbol.

When your symbol is complete, store it in your project directory or in a user library directory if you want to use the symbol in more than one project.

- 3. Instantiate the new symbol one or more times in your design schematic and connected it to other logic and I/O buffers as needed. As with library symbols, unused input pins on your behavioral module symbol should be tied to VCC or GND.

- 4. Add an attribute to each instance of a behavioral module symbol in your schematic to identify the compiled behavioral logic file. The format of the attribute is

```

FILE=filename

```

where filename is the name of the file produced by the behavioral compiler, either with or without extension. If the compiled file is stored in a different directory (such as a user library), include the complete directory path qualification in the FILE attribute.

## **Behavioral Module Example for Viewlogic**

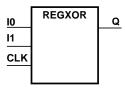

This simple example shows you how to develop a behavioral module defined by an ABEL-language equation file and represented by a custom symbol in a Viewlogic schematic.

1. Create the following ABEL file named regxor.abl.

```

MODULE regxor

TITLE 'Registered XOR gate'

IO pin;

Il pin;

CLK pin;

Q pin istype 'reg';

EQUATIONS

Q := IO $ I1;

Q.C = CLK;

end

```

2. Compile the file to create an EDIF netlist file named regxor.edn.

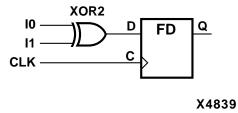

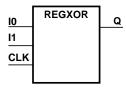

3. In Viewdraw, open a symbol window and create a new symbol named regxor as shown in the "The REGXOR Symbol" figure. The symbol has three input pins and one output pin corresponding to the pins defined in the ABEL equation file.

X4864

Figure 2-7 The REGXOR Symbol

- 4. Make sure the symbol is defined as a primitive. For example, if you are using WorkView Office, use the Change → Symbol Type → Module command to indicate that there is no underlying schematic for the symbol. Then save the symbol in your project directory.