# Volume 2(a): PPC405 User Manual

## Virtex-II Pro™ Platform FPGA Developer's Kit

March 2002 Release

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

"Xilinx" and the Xilinx logo are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved.

CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, XC5210 are registered Trademarks of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator, CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroBlaze, MicroVia, MultiLINX, Nano-Blaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, Rocket I/O, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex-II Pro, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACT-Floorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker, XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both: IBM IBM Logo PowerPC PowerPC Logo Blue Logic CoreConnect CodePack

All other trademarks are the property of their respective owners.

Xilinx does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or information shown or described herein "as is." By providing the design, code, or information as one possible implementation of a feature, application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 2002 Xilinx, Inc. All Rights Reserved.

##

## Preface

## About This Book

This document is intended to serve as a stand-alone reference for application and system programmers of the PowerPC<sup>®</sup> 405D5 processor. It combines information from the following documents:

- *PowerPC 405 Embedded Processor Core User's Manual* published by IBM Corporation (IBM order number SA14-2339-01).

- The IBM PowerPC Embedded Environment Architectural Specifications for IBM PowerPC Embedded Controllers, published by IBM Corporation.

- *PowerPC Microprocessor Family: The Programming Environments* published by IBM Corporation (IBM order number G522-0290-01).

- IBM PowerPC Embedded Processors Application Note: *PowerPC 400 Series Caches: Programming and Coherency Issues.*

- IBM PowerPC Embedded Processors Application Note: PowerPC 40x Watch Dog Timer.

- IBM PowerPC Embedded Processors Application Note: *Programming Model Differences* of the IBM PowerPC 400 Family and 600/700 Family Processors.

## **Document Organization**

- Chapter 1, Introduction to the PPC405, provides a general understanding of the PPC405 as an implementation of the PowerPC embedded-environment architecture. This chapter also contains an overview of the features supported by the PPC405.

- Chapter 2, Operational Concepts, introduces the processor operating modes, execution model, synchronization, operand conventions, and instruction conventions.

- Chapter 3, User Programming Model, describes the registers and instructions available to application software.

- Chapter 4, PPC405 Privileged-Mode Programming Model, introduces the registers and instructions available to system software.

- Chapter 5, Memory-System Management, describes the operation of the memory system, including caches. Real-mode storage control is also described in this chapter.

- Chapter 6, Virtual-Memory Management, describes virtual-to-physical address translation as supported by the PPC405. Virtual-mode storage control is also described in this chapter.

- Chapter 7, Exceptions and Interrupts, provides details of all exceptions recognized by the PPC405 and how software can use the interrupt mechanism to handle exceptions.

- Chapter 8, Timer Resources, describes the timer registers and timer-interrupt controls available in the PPC405.

- Chapter 9, **Debugging**, describes the debug resources available to software and hardware debuggers.

- Chapter 10, **Reset and Initialization**, describes the state of the PPC405 following reset

and the requirements for initializing the processor.

- Chapter 11, Instruction Set, provides a detailed description of each instruction supported by the PPC405.

- Appendix A, **Register Summary**, is a reference of all registers supported by the PPC405.

- Appendix B, Instruction Summary, lists all instructions sorted by mnemonic, opcode, function, and form. Each entry for an instruction shows its complete encoding. General instruction-set information is also provided.

- Appendix C, Simplified Mnemonics, lists the simplified mnemonics recognized by many PowerPC assemblers. These mnemonics provide a shorthand means of specifying frequently-used instruction encodings and can greatly improve assembler code readability.

- Appendix D, Programming Considerations, provides information on improving performance of software written for the PPC405.

- Appendix E, PowerPC<sup>®</sup> 6xx/7xx Compatibility, describes the programming model differences between the PPC405 and PowerPC 6xx and 7xx series processors.

- Appendix F, PowerPC<sup>®</sup> Book-E Compatibility, describes the programming model differences between the PPC405 and PowerPC Book-E processors.

## **Document Conventions**

## **General Conventions**

Table 1 lists the general notational conventions used throughout this document.

| Convention            | Definition                                                                                                                                 |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| mnemonic              | Instruction mnemonics are shown in lower-case bold.                                                                                        |  |

| . (period)            | Update. When used as a character in an instruction mnemonic, a period (.) means that the instruction updates the condition-register field. |  |

| ! (exclamation)       | In instruction listings, an exclamation (!) indicates the start of a comment.                                                              |  |

| variable              | Variable items are shown in italic.                                                                                                        |  |

| <optional></optional> | Optional items are shown in angle brackets.                                                                                                |  |

| ActiveLow             | An overbar indicates an active-low signal.                                                                                                 |  |

| n                     | A decimal number.                                                                                                                          |  |

| 0x <i>n</i>           | A hexadecimal number.                                                                                                                      |  |

| 0b <i>n</i>           | A binary number.                                                                                                                           |  |

| ( <b>r</b> <i>n</i> ) | The contents of GPR <b>r</b> <i>n</i> .                                                                                                    |  |

| (rA 0)                | The contents of the register <b>r</b> A, or 0 if the <b>r</b> A instruction field is 0.                                                    |  |

| cr_bit                | Used in simplified mnemonics to specify a CR-bit position (0 to 31) used as an operand.                                                    |  |

www.xilinx.com

1-800-255-7778

Table P-1: General Notational Conventions

| Convention             | Definition                                                                                                                |

|------------------------|---------------------------------------------------------------------------------------------------------------------------|

| cr_field               | Used in simplified mnemonics to specify a CR field (0 to 7) used as an operand.                                           |

| OBJECTb                | A single bit in any object (a register, an instruction, an address, or a field) is shown as a subscripted number or name. |

| OBJECT <sub>b:b</sub>  | A range of bits in any object (a register, an instruction, an address, or a field).                                       |

| OBJECT <sub>b,b,</sub> | A list of bits in any object (a register, an instruction, an address, or a field).                                        |

| REGISTER[FIELD]        | Fields within any register are shown in square brackets.                                                                  |

| REGISTER[FIELD, FIELD] | A list of fields in any register.                                                                                         |

| REGISTER[FIELD:FIELD]  | A range of fields in any register.                                                                                        |

Table P-1:

General Notational Conventions (Continued)

## **Instruction Fields**

Table 2 lists the instruction fields used in the various instruction formats. They are found in the instruction encodings and pseudocode, and are referred to throughout this document when describing instructions. The table includes the bit locations for the field within the instruction encoding.

Table P-2: Instruction Field Definitions

| Field        | Location | Description                                                                                                                                                                                                                                                                                                                           |  |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

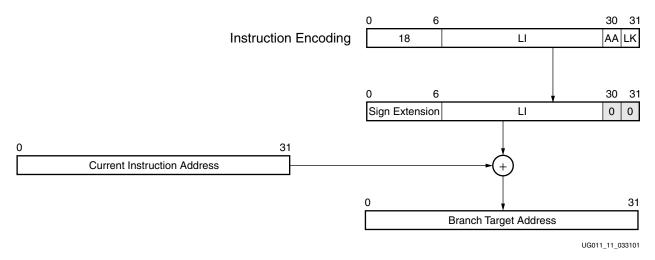

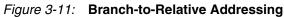

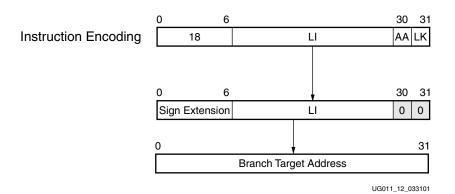

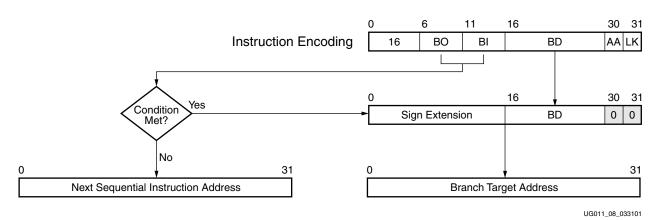

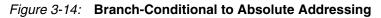

| AA           | 30       | Absolute-address bit (branch instructions).                                                                                                                                                                                                                                                                                           |  |

|              |          | 0—The immediate field represents an address <i>relative</i> to the current instruction address (CIA). The effective address (EA) of the branch is either the sum of the LI field sign-extended to 32 bits and the branch instruction address, or the sum of the BD field sign-extended to 32 bits and the branch instruction address. |  |

|              |          | 1—The immediate field represents an <i>absolute</i> address. The EA of the branch is either the LI field or the BD field, sign-extended to 32 bits.                                                                                                                                                                                   |  |

| BD           | 16:29    | An immediate field specifying a 14-bit signed two's-complement<br>branch displacement. This field is concatenated on the right with<br>0b00 and sign-extended to 32 bits.                                                                                                                                                             |  |

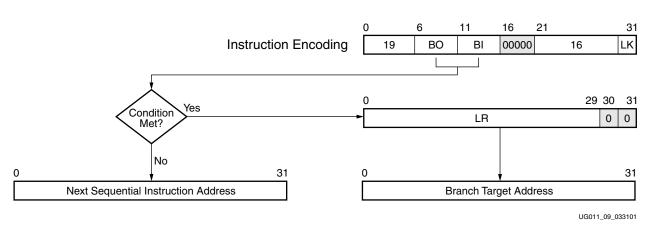

| BI           | 11:15    | Specifies a bit in the CR used as a source for the condition of a conditional-branch instruction.                                                                                                                                                                                                                                     |  |

| ВО           | 6:10     | Specifies options for conditional-branch instructions. See<br><b>Conditional Branch Control</b> , page 367                                                                                                                                                                                                                            |  |

| crbA         | 11:15    | Specifies a bit in the CR used as a source of a CR-logical instruction.                                                                                                                                                                                                                                                               |  |

| <b>crb</b> B | 16:20    | Specifies a bit in the CR used as a source of a CR-logical instruction.                                                                                                                                                                                                                                                               |  |

| crbD         | 6:10     | Specifies a bit in the CR used as a destination of a CR-Logical instruction.                                                                                                                                                                                                                                                          |  |

| Field        | Location | Description                                                                                                                                                                                     |  |

|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>crf</b> D | 6:8      | Specifies a field in the CR used as a target in a compare or <b>mcrf</b> instruction.                                                                                                           |  |

| crfS         | 11:13    | Specifies a field in the CR used as a source in a <b>mcrf</b> instruction.                                                                                                                      |  |

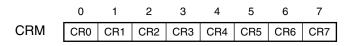

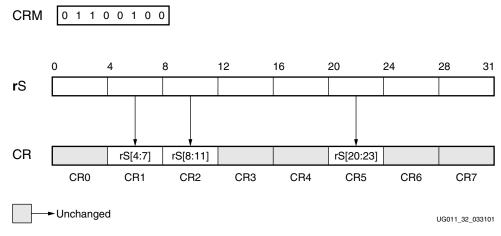

| CRM          | 12:19    | The field mask used to identify CR fields to be updated by the <b>mtcrf</b> instruction.                                                                                                        |  |

| d            | 16:31    | Specifies a 16-bit signed two's-complement integer displacement for load/store instructions.                                                                                                    |  |

| DCRF         | 11:20    | A split field used to specify a device control register (DCR). The field is used to form the DCR number (DCRN).                                                                                 |  |

| Е            | 16       | A single-bit immediate field in the <b>wrteei</b> instruction specifying the value to be written to the MSR[EE] bit.                                                                            |  |

| LI           | 6:29     | An immediate field specifying a 24-bit signed two's-complement<br>branch displacement. This field is concatenated on the right with<br>0b00 and sign-extended to 32 bits.                       |  |

| LK           | 31       | Link bit.                                                                                                                                                                                       |  |

|              |          | 0—Do not update the link register (LR).                                                                                                                                                         |  |

|              |          | 1—Update the LR with the address of the next instruction.                                                                                                                                       |  |

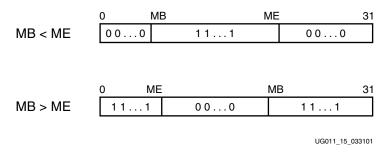

| MB           | 21:25    | Mask begin. Used in rotate-and-mask instructions to specify the beginning bit of a mask.                                                                                                        |  |

| ME           | 26:30    | Mask end. Used in rotate-and-mask instructions to specify the ending bit of a mask.                                                                                                             |  |

| NB           | 16:20    | Specifies the number of bytes to move in an immediate-string load or immediate-string store.                                                                                                    |  |

| OE           | 21       | Enables setting the OV and SO fields in the fixed-point exception register (XER) for extended arithmetic.                                                                                       |  |

| OPCD         | 0:5      | Primary opcode. Primary opcodes, in decimal, appear in the instruction format diagrams presented with individual instructions. The OPCD field name does not appear in instruction descriptions. |  |

| rA           | 11:15    | Specifies a GPR source operand and/or destination operand.                                                                                                                                      |  |

| rB           | 16:20    | Specifies a GPR source operand.                                                                                                                                                                 |  |

| Rc           | 31       | Record bit.                                                                                                                                                                                     |  |

|              |          | 0—Instruction does not update the CR.                                                                                                                                                           |  |

|              |          | 1—Instruction updates the CR to reflect the result of an operation.                                                                                                                             |  |

|              |          | See <b>Condition Register (CR)</b> , page 361 for a further discussion of how the CR bits are set.                                                                                              |  |

| -            | 6:10     | Specifies a GPR destination operand.                                                                                                                                                            |  |

| rD           |          |                                                                                                                                                                                                 |  |

| rD<br>rS     | 6:10     | Specifies a GPR source operand.                                                                                                                                                                 |  |

#### Table P-2: Instruction Field Definitions (Continued)

| Field | Location | Description                                                                                                                                                                                                                                 |  |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SIMM  | 16:31    | An immediate field used to specify a 16-bit signed-integer value.                                                                                                                                                                           |  |

| SPRF  | 11:20    | A split field used to specify a special purpose register (SPR). The field is used to form the SPR number (SPRN).                                                                                                                            |  |

| TBRF  | 11:20    | A split field used to specify a time-base register (TBR). The field is used to form the TBR number (TBRN).                                                                                                                                  |  |

| ТО    | 6:10     | Specifies the trap conditions, as defined in the <b>tw</b> and <b>twi</b> instruction descriptions.                                                                                                                                         |  |

| UIMM  | 16:31    | An immediate field used to specify a 16-bit unsigned-integer value.                                                                                                                                                                         |  |

| ХО    | 21:30    | Extended opcode for instructions <i>without</i> an OE field. Extended opcodes, in decimal, appear in the instruction format diagrams presented with individual instructions. The XO field name does not appear in instruction descriptions. |  |

| ХО    | 22:30    | Extended opcode for instructions <i>with</i> an OE field. Extended opcodes, in decimal, appear in the instruction format diagrams presented with individual instructions. The XO field name does not appear in instruction descriptions.    |  |

#### Table P-2: Instruction Field Definitions (Continued)

## **Pseudocode Conventions**

Table 3 lists additional conventions used primarily in the pseudocode describing the operation of each instruction.

| Convention       | Definition                                                                 |

|------------------|----------------------------------------------------------------------------|

| $\leftarrow$     | Assignment                                                                 |

| ^                | AND logical operator                                                       |

| -                | NOT logical operator                                                       |

| V                | OR logical operator                                                        |

| $\oplus$         | Exclusive-OR (XOR) logical operator                                        |

| +                | Two's-complement addition                                                  |

| _                | Two's-complement subtraction, unary minus                                  |

| ×                | Multiplication                                                             |

| ÷                | Division yielding a quotient                                               |

| %                | Remainder of an integer division. For example, $(33 \% 32) = 1$ .          |

|                  | Concatenation                                                              |

| =, ≠             | Equal, not-equal relations                                                 |

| <,>              | Signed comparison relations                                                |

| u u<br><, >      | Unsigned comparison relations                                              |

| c <sub>0:3</sub> | A four-bit object used to store condition results in compare instructions. |

Table P-3:

Pseudocode Conventions

| Convention Definition |                                                                                                                                                                                                                                                            |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| nþ                    | The bit or bit value $b$ is replicated $n$ times.                                                                                                                                                                                                          |  |

| x                     | Bit positions that are don't-cares.                                                                                                                                                                                                                        |  |

| CEIL(n)               | Least integer $\geq n$ .                                                                                                                                                                                                                                   |  |

| CIA                   | Current instruction address. The 32-bit address of the instruction<br>being described by a sequence of pseudocode. This address is<br>used to set the next instruction address (NIA). Does not<br>correspond to any architected register.                  |  |

| DCR(DCRN)             | A specific device control register, as indicated by DCRN.                                                                                                                                                                                                  |  |

| DCRN                  | The device control register number formed using the split DCRF field in a <b>mfdcr</b> or <b>mtdcr</b> instruction.                                                                                                                                        |  |

| do                    | Do loop. "to" and "by" clauses specify incrementing an iteration variable. "while" and "until" clauses specify terminating conditions. Indenting indicates the scope of a loop.                                                                            |  |

| EA                    | Effective address. The 32-bit address that specifies a location in main storage. Derived by applying indexing or indirect addressing rules to the specified operand.                                                                                       |  |

| EXTS(n)               | The result of extending <i>n</i> on the left with sign bits.                                                                                                                                                                                               |  |

| ifthenelse            | Conditional execution: if <i>condition</i> then <i>a</i> else <i>b</i> , where <i>a</i> and <i>b</i> represent one or more pseudocode statements. Indenting indicates the ranges of <i>a</i> and <i>b</i> . If <i>b</i> is null, the else does not appear. |  |

| instruction(EA)       | An instruction operating on a data-cache block or instruction-<br>cache block associated with an EA.                                                                                                                                                       |  |

| leave                 | Leave innermost do-loop or the do-loop specified by the leave statement.                                                                                                                                                                                   |  |

| MASK(MB,ME)           | Mask having 1's in positions MB through ME (wrapping if $MB > ME$ ) and 0's elsewhere.                                                                                                                                                                     |  |

| MS(addr, n)           | The number of bytes represented by <i>n</i> at the location in main storage represented by <i>addr</i> .                                                                                                                                                   |  |

| NIA                   | Next instruction address. The 32-bit address of the next instruction to be executed. In pseudocode, a successful branch is indicated by assigning a value to NIA. For instructions that do not branch, the NIA is CIA +4.                                  |  |

| RESERVE               | Reserve bit. Indicates whether a process has reserved a block of storage.                                                                                                                                                                                  |  |

| ROTL((RS),n)          | Rotate left. The contents of RS are shifted left the number of bits specified by <i>n</i> .                                                                                                                                                                |  |

| SPR(SPRN)             | A specific special-purpose register, as indicated by SPRN.                                                                                                                                                                                                 |  |

#### Table P-3: Pseudocode Conventions (Continued)

| Convention | Definition                                                                                                             |

|------------|------------------------------------------------------------------------------------------------------------------------|

| SPRN       | The special-purpose register number formed using the split<br>SPRF field in a <b>mfspr</b> or <b>mtspr</b> instruction |

| TBR(TBRN)  | A specific time-base register, as indicated by TBRN.                                                                   |

| TBRN       | The time-base register number formed using the split TBRF field in a <b>mftb</b> instruction.                          |

## **Operator Precedence**

Table 4 lists the pseudocode operators and their associativity in descending order of precedence

| Operators                                                    | Associativity |

|--------------------------------------------------------------|---------------|

| REGISTER <sub>b</sub> , REGISTER[FIELD], function evaluation | Left to right |

| <sup>n</sup> b                                               | Right to left |

| -, – (unary minus)                                           | Right to left |

| X, ÷                                                         | Left to right |

| +, -                                                         | Left to right |

|                                                              | Left to right |

| =, ≠, <, >, <sup>u</sup> <, <sup>u</sup> >                   | Left to right |

| ∧,⊕                                                          | Left to right |

| V                                                            | Left to right |

| ←                                                            | None          |

## **Registers**

Table 5 lists the PPC405 registers and their descriptive names.

Table P-5: PPC405 Registers

| Register | Descriptive Name                  |

|----------|-----------------------------------|

| CCR0     | Core-configuration register 0     |

| CR       | Condition register                |

| CTR      | Count register                    |

| DACn     | Data-address compare <i>n</i>     |

| DBCRn    | Debug-control register <i>n</i>   |

| DBSR     | Debug-status register             |

| DCCR     | Data-cache cacheability register  |

| DCWR     | Data-cache write-through register |

| Register Descriptive Name |                                                                                                                      |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| DEAR                      | Data-error address register                                                                                          |  |

| DVCn                      | Data-value compare <i>n</i>                                                                                          |  |

| ESR                       | Exception-syndrome register                                                                                          |  |

| EVPR                      | Exception-vector prefix register                                                                                     |  |

| GPR                       | General-purpose register. Specific GPRs are identified using the notational convention <b>r</b> <i>n</i> (see below) |  |

| IACn                      | Instruction-address compare <i>n</i>                                                                                 |  |

| ICCR                      | Instruction-cache cacheability register                                                                              |  |

| ICDBDR                    | Instruction-cache debug-data register                                                                                |  |

| LR                        | Link register                                                                                                        |  |

| MSR                       | Machine-state register                                                                                               |  |

| PID                       | Process ID                                                                                                           |  |

| PIT                       | Programmable-interval timer                                                                                          |  |

| PVR                       | Processor-version register                                                                                           |  |

| <b>r</b> n                | Specifies GPR <i>n</i> ( <b>r</b> 15, for example)                                                                   |  |

| SGR                       | Storage-guarded register                                                                                             |  |

| SLER                      | Storage little-endian register                                                                                       |  |

| SPRGn                     | SPR general-purpose register <i>n</i>                                                                                |  |

| SRRn                      | Save/restore register <i>n</i>                                                                                       |  |

| SUOR                      | Storage user-defined 0 register                                                                                      |  |

| TBL                       | Time-base lower                                                                                                      |  |

| TBU                       | Time-base upper                                                                                                      |  |

| TCR                       | Timer-control register                                                                                               |  |

| TSR                       | Timer-status register                                                                                                |  |

| USPRGn                    | User SPR general-purpose register <i>n</i>                                                                           |  |

| XER                       | Fixed-point exception register                                                                                       |  |

| ZPR                       | Zone-protection register                                                                                             |  |

|                           |                                                                                                                      |  |

#### Table P-5: PPC405 Registers (Continued)

## Terms

| atomic access | A memory access that attempts to read from and write to the<br>same address uninterrupted by other accesses to that address.<br>The term refers to the fact that such transactions are indivisible. |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| big endian    | A memory byte ordering where the address of an item corresponds to the most-significant byte.                                                                                                       |

| Book-E            | An version of the PowerPC architecture designed specifically for embedded applications.                                                                                                                                                            |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cache block       | Synonym for <i>cacheline</i> .                                                                                                                                                                                                                     |

| cacheline         | A portion of a cache array that contains a copy of contiguous system-memory addresses. Cachelines are 32-bytes long and aligned on a 32-byte address.                                                                                              |

| clear             | To write a bit value of 0.                                                                                                                                                                                                                         |

| cache set         | Synonym for <i>congruence class</i> .                                                                                                                                                                                                              |

| congruence class  | A collection of cachelines with the same index.                                                                                                                                                                                                    |

| dirty             | An indication that cache information is more recent than the copy in memory.                                                                                                                                                                       |

| doubleword        | Eight bytes, or 64 bits.                                                                                                                                                                                                                           |

| effective address | The untranslated memory address as seen by a program.                                                                                                                                                                                              |

| exception         | An abnormal event or condition that requires the processor's attention. They can be caused by instruction execution or an external device. The processor records the occurrence of an exception and they often cause an <i>interrupt</i> to occur. |

| fill buffer       | A buffer that receives and sends data and instructions between<br>the processor and PLB. It is used when cache misses occur and<br>when access to non-cacheable memory occurs.                                                                     |

| flush             | A cache or TLB operation that involves writing back a modified entry to memory, followed by an invalidation of the entry.                                                                                                                          |

| GB                | Gigabyte, or one-billion bytes.                                                                                                                                                                                                                    |

| halfword          | Two bytes, or 16 bits.                                                                                                                                                                                                                             |

| hit               | For cache arrays and TLB arrays, an indication that requested information exists in the accessed array.                                                                                                                                            |

| interrupt         | The process of stopping the currently executing program so that an exception can be handled.                                                                                                                                                       |

| invalidate        | A cache or TLB operation that causes an entry to be marked as invalid. An invalid entry can be subsequently replaced.                                                                                                                              |

| КВ                | Kilobyte, or one-thousand bytes.                                                                                                                                                                                                                   |

| line buffer       | A buffer located in the cache array that can temporarily hold the contents of an entire cacheline. It is loaded with the contents of a cacheline when a cache hit occurs.                                                                          |

| little endian     | A memory byte ordering where the address of an item corresponds to the least-significant byte.                                                                                                                                                     |

| logical address   | Synonym for <i>effective address</i> .                                                                                                                                                                                                             |

| МВ                | Megabyte, or one-million bytes.                                                                                                                                                                                                                    |

| memory            | Collectively, cache memory and system memory.                                                                                                                                                                                                      |

| miss              | For cache arrays and TLB arrays, an indication that requested information does not exist in the accessed array.                                                                                                                                    |

| OEA              | The PowerPC operating-environment architecture, which<br>defines the memory-management model, supervisor-level<br>registers and instructions, synchronization requirements, the<br>exception model, and the time-base resources as seen by<br>supervisor programs. |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| on chip          | In system-on-chip implementations, this indicates on the same<br>chip as the processor core, but external to the processor core.                                                                                                                                   |

| pending          | As applied to interrupts, this indicates that an exception occurred, but the interrupt is disabled. The interrupt occurs when it is later enabled.                                                                                                                 |

| physical address | The address used to access physically-implemented memory.<br>This address can be translated from the effective address. When<br>address translation is not used, this address is equal to the<br>effective address.                                                |

| PLB              | Processor local bus.                                                                                                                                                                                                                                               |

| privileged mode  | The operating mode typically used by system software.<br>Privileged operations are allowed and software can access all<br>registers and memory.                                                                                                                    |

| process          | A program (or portion of a program) and any data required for the program to run.                                                                                                                                                                                  |

| problem state    | Synonym for <i>user mode</i> .                                                                                                                                                                                                                                     |

| real address     | Synonym for <i>physical address</i> .                                                                                                                                                                                                                              |

| scalar           | Individual data objects and instructions. Scalars are of arbitrary size.                                                                                                                                                                                           |

| set              | To write a bit value of 1.                                                                                                                                                                                                                                         |

| sticky           | A bit that can be set by software, but cleared only by the processor. Alternatively, a bit that can be cleared by software, but set only by the processor.                                                                                                         |

| string           | A sequence of consecutive bytes.                                                                                                                                                                                                                                   |

| supervisor state | Synonym for privileged mode.                                                                                                                                                                                                                                       |

| system memory    | Physical memory installed in a computer system external to the processor core, such RAM, ROM, and flash.                                                                                                                                                           |

| tag              | As applied to caches, a set of address bits used to uniquely<br>identify a specific cacheline within a congruence class. As<br>applied to TLBs, a set of address bits used to uniquely identify<br>a specific entry within the TLB.                                |

| UISA             | The PowerPC user instruction-set architecture, which defines<br>the base user-level instruction set, registers, data types, the<br>memory model, the programming model, and the exception<br>model as seen by user programs.                                       |

| user mode        | The operating mode typically used by application software.<br>Privileged operations are not allowed in user mode, and<br>software can access a restricted set of registers and memory.                                                                             |

www.xilinx.com 1-800-255-7778

| VEA             | The PowerPC virtual-environment architecture, which defines<br>a multi-access memory model, the cache model, cache-control<br>instructions, and the time-base resources as seen by user<br>programs.         |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| virtual address | An intermediate address used to translate an effective address<br>into a physical address. It consists of a process ID and the<br>effective address. It is only used when address translation is<br>enabled. |

| word            | Four bytes, or 32 bits.                                                                                                                                                                                      |

## **Additional Reading**

In addition to the source documents listed on page 311, the following documents contain additional information of potential interest to readers of this manual:

- The PowerPC Architecture: A Specification for a New Family of RISC Processors, IBM 5/1994. Published by Morgan Kaufmann Publishers, Inc. San Francisco (ASIN: 1558603166).

- Book E: Enhanced PowerPC Architecture, IBM 3/2000.

- *The PowerPC Compiler Writer's Guide*, IBM 1/1996. Published by Warthman Associates, Palo Alto, CA (ISBN 0-9649654-0-2).

- Optimizing PowerPC Code : Programming the PowerPC Chip in Assembly Language, by Gary Kacmarcik (ASIN: 0201408392)

- PowerPC Programming Pocket Book, by Steve Heath (ISBN 0750621117).

- *Computer Architecture: A Quantitative Approach,* by John L. Hennessy and David A. Patterson.

- ٠

## Chapter 1

## Introduction to the PPC405

The PPC405 is a 32-bit implementation of the *PowerPC*<sup>®</sup> *embedded-environment architecture* that is derived from the PowerPC architecture. Specifically, the PPC405 is an embedded PowerPC 405D5 processor core.

The PowerPC architecture provides a software model that ensures compatibility between implementations of the PowerPC family of microprocessors. The PowerPC architecture defines parameters that guarantee compatible processor implementations at the application-program level, allowing broad flexibility in the development of derivative PowerPC implementations that meet specific market requirements.

This chapter provides an overview of the PowerPC architecture and an introduction to the features of the PPC405 core.

## **PowerPC Architecture Overview**

The PowerPC architecture is a 64-bit architecture with a 32-bit subset. The material in this document only covers aspects of the 32-bit architecture implemented by the PPC405.

In general, the PowerPC architecture defines the following:

- Instruction set

- Programming model

- Memory model

- Exception model

- Memory-management model

- Time-keeping model

#### Instruction Set

The *instruction set* specifies the types of instructions (such as load/store, integer arithmetic, and branch instructions), the specific instructions, and the encoding used for the instructions. The instruction set definition also specifies the addressing modes used for accessing memory.

#### Programming Model

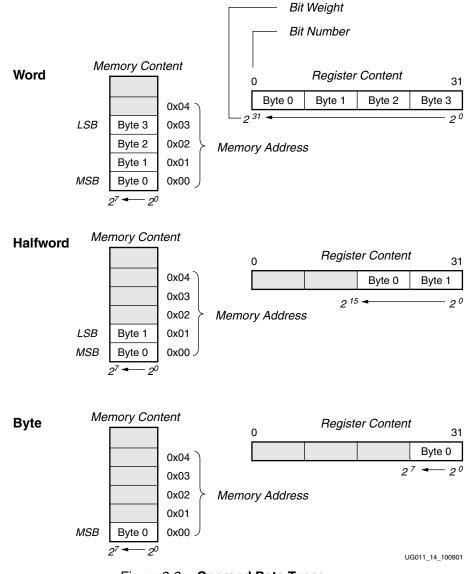

The *programming model* defines the register set and the memory conventions, including details regarding the bit and byte ordering, and the conventions for how data are stored.

#### Memory Model

The *memory model* defines the address-space size and how it is subdivided into pages. It also defines attributes for specifying memory-region cacheability, byte ordering (big-endian or little-endian), coherency, and protection.

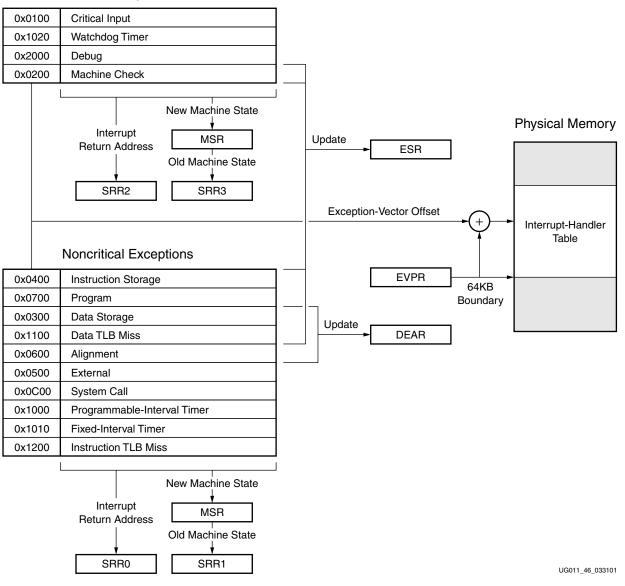

## Exception Model

The *exception model* defines the set of exceptions and the conditions that can cause those exceptions. The model specifies exception characteristics, such as whether they are precise or imprecise, synchronous or asynchronous, and maskable or non-maskable. The model defines the exception vectors and a set of registers used when interrupts occur as a result of an exception. The model also provides memory space for implementation-specific exceptions.

### Memory-Management Model

The *memory-management model* defines how memory is partitioned, configured, and protected. The model also specifies how memory translation is performed, defines special memory-control instructions, and specifies other memory-management characteristics.

### Time-Keeping Model

The *time-keeping model* defines resources that permit the time of day to be determined and the resources and mechanisms required for supporting timer-related exceptions.

## PowerPC Architecture Levels

These above aspects of the PowerPC architecture are defined at three levels . This layering provides flexibility by allowing degrees of software compatibility across a wide range of implementations. For example, an implementation such as an embedded controller can support the user instruction set, but not the memory management, exception, and cache models where it might be impractical to do so.

The three levels of the PowerPC architecture are defined in Table 1-1.

|   | User Instruction-Set Architecture<br>(UISA)                                                                                  | Virtual Environment Architecture<br>(VEA)                                                                                               | Operating Environment<br>Architecture (OEA)                                                                                           |

|---|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|   | Defines the architecture level to<br>which user-level (sometimes<br>referred to as problem state)<br>software should conform | <ul> <li>Defines additional user-level<br/>functionality that falls outside<br/>typical user-level software<br/>requirements</li> </ul> | <ul> <li>Defines supervisor-level<br/>resources typically required by<br/>an operating system</li> <li>Defines the memory-</li> </ul> |

| • | instruction set, user-level<br>registers, data types, floating-<br>point memory conventions,                                 | • Describes the memory model for<br>an environment in which<br>multiple devices can access<br>memory                                    | management model, supervisor-<br>level registers, synchronization<br>requirements, and the exception<br>model                         |

|   | exception model as seen by user<br>programs, memory model, and<br>the programming model                                      | <ul> <li>Defines aspects of the cache model and cache-control instructions</li> </ul>                                                   | • Defines the time-base resources from a supervisor-level perspective                                                                 |

|   |                                                                                                                              | • Defines the time-base resources from a user-level perspective                                                                         |                                                                                                                                       |

|   | <b>Note:</b> All PowerPC implementations adhere to the UISA.                                                                 | <b>Note:</b> Implementations that conform to the VEA level are guaranteed to conform to the UISA level.                                 | <b>Note:</b> Implementations that conform to the OEA level are guaranteed to conform to the UISA and VEA levels.                      |

www.xilinx.com

1-800-255-7778

#### Table 1-1: Three Levels of PowerPC Architecture

The PowerPC architecture requires that all PowerPC implementations adhere to the UISA, offering compatibility among all PowerPC application programs. However, different versions of the VEA and OEA are permitted.

Embedded applications written for the PPC405 are compatible with other PowerPC implementations. Privileged software generally is not compatible. The migration of

privileged software from the PowerPC architecture to the PPC405 is in many cases straightforward because of the simplifications made by the PowerPC embeddedenvironment architecture. Software developers who are concerned with crosscompatibility of privileged software between the PPC405 and other PowerPC implementations should refer to Appendix E, PowerPC<sup>®</sup> 6xx/7xx Compatibility.

### Latitude Within the PowerPC Architecture Levels

Although the PowerPC architecture defines parameters necessary to ensure compatibility among PowerPC processors, it also allows a wide range of options for individual implementations. These are:

- Some resources are optional, such as certain registers, bits within registers, instructions, and exceptions.

- Implementations can define additional privileged special-purpose registers (SPRs), exceptions, and instructions to meet special system requirements, such as power management in processors designed for very low-power operation.

- Implementations can define many operating parameters. For example, the PowerPC architecture can define the possible condition causing an alignment exception. A particular implementation can choose to solve the alignment problem without causing an exception.

- Processors can implement any architectural resource or instruction with assistance from software (that is, they can trap and emulate) as long as the results (aside from performance) are identical to those specified by the architecture. In this case, a complete implementation requires both hardware and software.

- Some parameters are defined at one level of the architecture and defined more specifically at another. For example, the UISA defines conditions that can cause an alignment exception and the OEA specifies the exception itself.

#### Features Not Defined by the PowerPC Architecture

Because flexibility is an important feature of the PowerPC architecture, many aspects of processor design (typically relating to the hardware implementation) are not defined, including the following:

#### System-Bus Interface

Although many implementations can share similar interfaces, the PowerPC architecture does not define individual signals or the bus protocol. For example, the OEA allows each implementation to specify the signal or signals that trigger a machine-check exception.

#### Cache Design

The PowerPC architecture does not define the size, structure, replacement algorithm, or mechanism used for maintaining cache coherency. The PowerPC architecture supports, but does not require, the use of separate instruction and data caches.

#### **Execution Units**

The PowerPC architecture is a RISC architecture, and as such has been designed to facilitate the design of processors that use pipelining and parallel execution units to maximize instruction throughput. However, the PowerPC architecture does not define the internal hardware details of an implementation. For example, one processor might implement two units dedicated to executing integer-arithmetic instructions and another might implement a single unit for executing all integer instructions.

#### Other Internal Microarchitecture Issues

The PowerPC architecture does not specify the execution unit responsible for executing a particular instruction. The architecture does not define details regarding the instruction-fetch mechanism, how instructions are decoded and dispatched, and how results are written to registers. Dispatch and write-back can occur in-order or out-of-order. Although

the architecture specifies certain registers, such as the GPRs and FPRs, implementations can use register renaming or other schemes to reduce the impact of data dependencies and register contention.

#### Implementation-Specific Registers

Each implementation can have its own unique set of implementation registers that are not defined by the architecture.

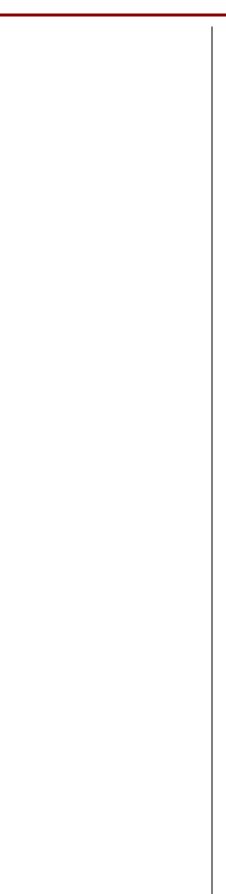

## PowerPC Embedded-Environment Architecture

The PowerPC embedded-environment architecture is optimized for embedded controllers. This architecture is a forerunner to the PowerPC Book-E architecture. The PowerPC embedded-environment architecture provides an alternative definition for certain features specified by the PowerPC VEA and OIA. Implementations that adhere to the PowerPC embedded-environment architecture also adhere to the PowerPC UISA. PowerPC embedded-environment processors are 32-bit only implementations and thus do not include the special 64-bit extensions to the PowerPC UISA. Also, floating-point support can be provided either in hardware or software by PowerPC embedded-environment processors.

Figure 1-1 shows the relationship between the PowerPC embedded-environment architecture, the PowerPC architecture, and the PowerPC Book-E architecture.

#### Figure 1-1: Relationship of PowerPC Architectures

The PowerPC embedded-environment architecture features:

- Memory management optimized for embedded software environments.

- Cache-management instructions for optimizing performance and memory control in complex applications that are graphically and numerically intensive.

- Storage attributes for controlling memory-system behavior.

www.xilinx.com

1-800-255-7778

- Special-purpose registers for controlling the use of debug resources, timer resources, interrupts, real-mode storage attributes, memory-management facilities, and other architected processor resources.

- A device-control-register address space for managing on-chip peripherals such as memory controllers.

- A dual-level interrupt structure and interrupt-control instructions.

- Multiple timer resources.

- Debug resources that enable hardware-debug and software-debug functions such as instruction breakpoints, data breakpoints, and program single-stepping.

## Virtual Environment

The virtual environment defines architectural features that enable application programs to create or modify code, to manage storage coherency, and to optimize memory-access performance. It defines the cache and memory models, the timekeeping resources from a user perspective, and resources that are accessible in user mode but are primarily used by system-library routines. The following summarizes the virtual-environment features of the PowerPC embedded-environment architecture:

- Storage model:

- Storage-control instructions as defined in the PowerPC virtual-environment architecture. These instructions are used to manage instruction caches and data caches, and for synchronizing and ordering instruction execution.

- Storage attributes for controlling memory-system behavior. These are: write-through, cacheability, memory coherence (optional), guarded, and endian.

- Operand-placement requirements and their effect on performance.

- The time-base function as defined by the PowerPC virtual-environment architecture, for user-mode read access to the 64-bit time base.

## **Operating Environment**

The operating environment describes features of the architecture that enable operating systems to allocate and manage storage, to handle errors encountered by application programs, to support I/O devices, and to provide operating-system services. It specifies the resources and mechanisms that require privileged access, including the memory-protection and address-translation mechanisms, the exception-handling model, and privileged timer resources. Table 1-2 summarizes the operating-environment features of the PowerPC embedded-environment architecture.

| Table 1-2: | <b>Operating-Environment Features of the PowerPC Embedded-Environment Architecture</b> |

|------------|----------------------------------------------------------------------------------------|

|------------|----------------------------------------------------------------------------------------|

| Operating<br>Environment | Features                                                                                                       |     |

|--------------------------|----------------------------------------------------------------------------------------------------------------|-----|

| Register model           | <ul> <li>Privileged special-purpose registers (SPRs) and instructions for accessing those registers</li> </ul> |     |

|                          | • Device control registers (DCRs) and instructions for accessing those registers                               |     |

| Storage model            | Privileged cache-management instructions                                                                       |     |

| 0                        | Storage-attribute controls                                                                                     |     |

|                          | Address translation and memory protection                                                                      |     |

|                          | Privileged TLB-management instructions                                                                         |     |

| Exception model          | Dual-level interrupt structure supporting various exception types                                              |     |

| 1                        | Specification of interrupt priorities and masking                                                              |     |

|                          | Privileged SPRs for controlling and handling exceptions                                                        |     |

|                          | Interrupt-control instructions                                                                                 |     |

|                          | <ul> <li>Specification of how partially executed instructions are handled when an interru occurs</li> </ul>    | upt |

| Debug model              | Privileged SPRs for controlling debug modes and debug events                                                   |     |

| 0                        | Specification for seven types of debug events                                                                  |     |

|                          | <ul> <li>Specification for allowing a debug event to cause a reset</li> </ul>                                  |     |

|                          | • The ability of the debug mechanism to freeze the timer resources                                             |     |

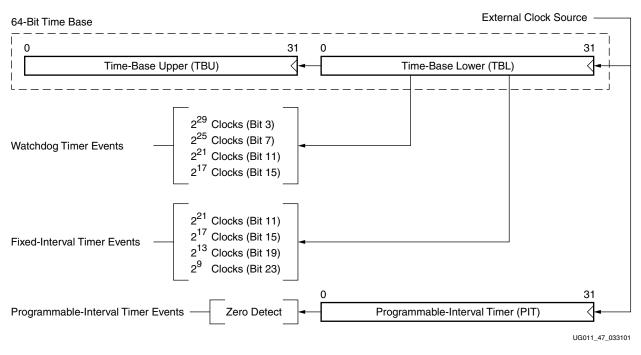

| Time-keeping model       | • 64-bit time base                                                                                             |     |

|                          | <ul> <li>32-bit decrementer (the programmable-interval timer)</li> </ul>                                       |     |

|                          | Three timer-event interrupts:                                                                                  |     |

|                          | - Programmable-interval timer (PIT)                                                                            |     |

|                          | - Fixed-interval timer (FIT)                                                                                   |     |

|                          | - Watchdog timer (WDT)                                                                                         |     |

|                          | <ul> <li>Privileged SPRs for controlling the timer resources</li> </ul>                                        |     |

|                          | The ability to freeze the timer resources using the debug mechanism                                            |     |

| Synchronization          | Requirements for special registers and the TLB                                                                 |     |

| requirements             | <ul> <li>Requirements for instruction fetch and for data access</li> </ul>                                     |     |

|                          | Specifications for context synchronization and execution synchronization                                       |     |

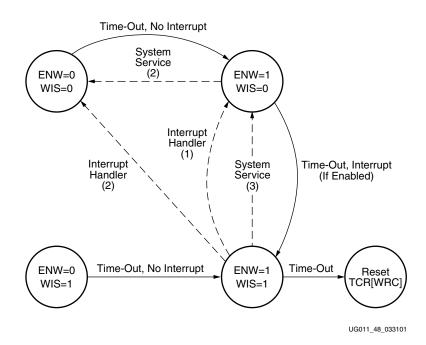

| Reset and initialization | Specification for two internal mechanisms that can cause a reset:                                              |     |

| requirements             | - Debug-control register (DBCR)                                                                                |     |

|                          | - Timer-control register (TCR)                                                                                 |     |

|                          | Contents of processor resources after a reset                                                                  |     |

|                          | • The software-initialization requirements, including an initialization code examp                             | ole |

## PowerPC Book-E Architecture

The PowerPC Book-E architecture extends the capabilities introduced in the PowerPC embedded-environment architecture. Although not a PowerPC Book-E implementation, many of the features available in the 32-bit subset of the PowerPC Book-E architecture are available in the PPC405. The PowerPC Book-E architecture and the PowerPC embedded-environment architecture differ in the following general ways:

- 64-bit addressing and 64-bit operands are available. Unlike 64-bit mode in the PowerPC UISA, 64-bit support in PowerPC Book-E architecture is non-modal and instead defines new 64-bit instructions and flags.

- Real mode is eliminated, and the memory-management unit is active at all times. The elimination of real mode results in the elimination of real-mode storage-attribute registers.

- Memory synchronization requirements are changed in the architecture and a memory-barrier instruction is introduced.

- A small number of new instructions are added to the architecture and several instructions are removed.

- Several SPR addresses and names are changed in the architecture, as are the assignment and meanings of some bits within certain SPRs.

Embedded applications written for the PPC405 are compatible with PowerPC Book-E implementations. Privileged software is, in general, not compatible, but the differences are relatively minor. Software developers who are concerned with cross-compatibility of privileged software between the PPC405 and PowerPC Book-E implementations should refer to Appendix F, PowerPC<sup>®</sup> Book-E Compatibility.

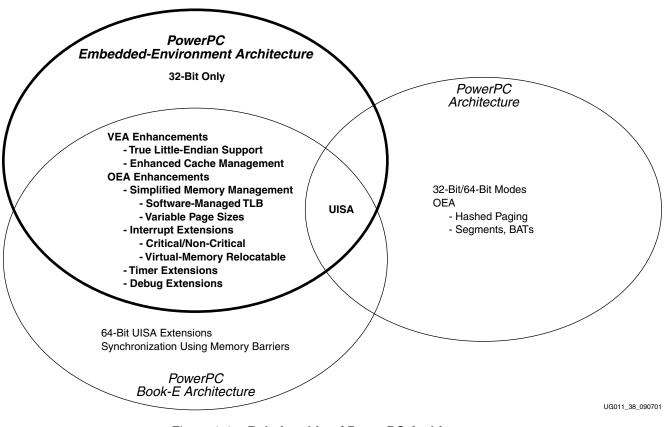

## **PPC405 Features**

The PPC405 processor core is an implementation of the PowerPC embedded-environment architecture. The processor provides fixed-point embedded applications with high performance at low power consumption. It is compatible with the PowerPC UISA. Much of the PPC405 VEA and OEA support is also available in implementations of the PowerPC Book-E architecture. Key features of the PPC405 include:

- A fixed-point execution unit fully compliant with the PowerPC UISA:

- 32-bit architecture, containing thirty-two 32-bit general purpose registers (GPRs).

- PowerPC embedded-environment architecture extensions providing additional support for embedded-systems applications:

- True little-endian operation

- Flexible memory management

- Multiply-accumulate instructions for computationally intensive applications

- Enhanced debug capabilities

- 64-bit time base

- 3 timers: programmable interval timer (PIT), fixed interval timer (FIT), and watchdog timer (All are synchronous with the time base)

- Performance-enhancing features, including:

- Static branch prediction

- Five-stage pipeline with single-cycle execution of most instructions, including loads and stores

- Multiply-accumulate instructions

- Hardware multiply/divide for faster integer arithmetic (4-cycle multiply, 35-cycle divide)

- Enhanced string and multiple-word handling

- Support for unaligned loads and unaligned stores to cache arrays, main memory, and on-chip memory (OCM)

- Minimized interrupt latency

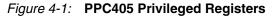

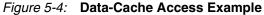

- Integrated instruction-cache:

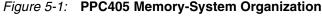

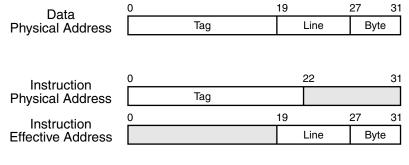

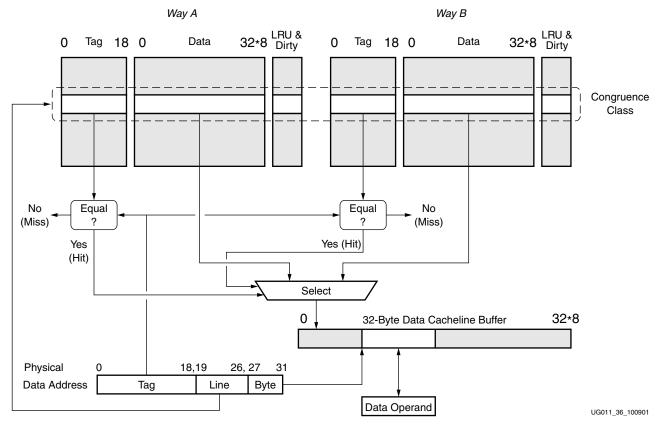

- 16 KB, 2-way set associative

- Eight words (32 bytes) per cacheline

- Fetch line buffer

- Instruction-fetch hits are supplied from the fetch line buffer

- Programmable prefetch of next-sequential line into the fetch line buffer

- Programmable prefetch of non-cacheable instructions: full line (eight words) or half line (four words)

- Non-blocking during fetch line fills

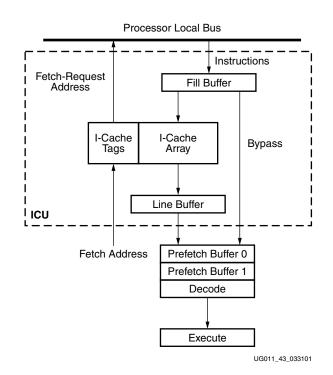

- Integrated data-cache:

- 16 KB, 2-way set associative

- Eight words (32 bytes) per cacheline

- Read and write line buffers

- Load and store hits are supplied from/to the line buffers

- Write-back and write-through support

- Programmable load and store cacheline allocation

- Operand forwarding during cacheline fills

- Non-blocking during cacheline fills and flushes

- Support for on-chip memory (OCM) that can provide memory-access performance identical to a cache hit

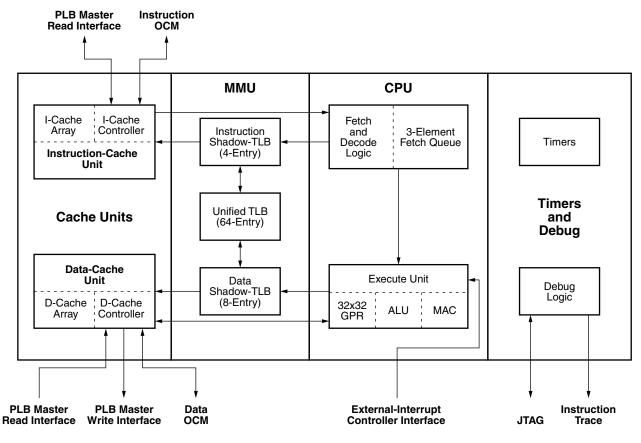

- Flexible memory management:

- Translation of the 4 GB logical-address space into the physical-address space

- Independent control over instruction translation and protection, and data translation and protection

- Page-level access control using the translation mechanism

- Software control over the page-replacement strategy

- Write-through, cacheability, user-defined 0, guarded, and endian (WIU0GE) storage-attribute control for each virtual-memory region

- WIU0GE storage-attribute control for thirty-two 128 MB regions in real mode

- Additional protection control using zones

- Enhanced debug support with logical operators:

- Four instruction-address compares

- Two data-address compares

- Two data-value compares

- JTAG instruction for writing into the instruction cache

- Forward and backward instruction tracing

- Advanced power management support

## **Privilege Modes**

Software running on the PPC405 can do so in one of two privilege modes: privileged and user. The privilege modes supported by the PPC405 are described in **Processor Operating Modes**, page 343.

### **Privileged Mode**

*Privileged mode* allows programs to access all registers and execute all instructions supported by the processor. Normally, the operating system and low-level device drivers operate in this mode.

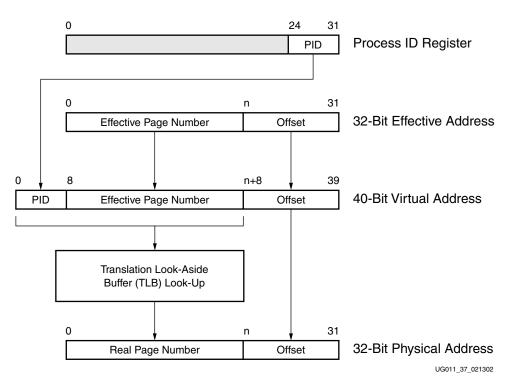

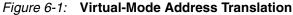

#### User Mode