# **SDA FIR Control Logic**

February 8, 1998

**Product Specification**

Xilinx Inc. 2100 Logic Drive San Jose, CA 95124 Phone: +1 408-559-7778 Fax: +1 408-559-7114 E-mail: dsp@xilinx.com URL: www.xilinx.com

X7556

### **Features**

- Drop-in modules for the XC4000E, EX, and XL families

- High performance and density guaranteed through Relational Placed Macro (RPM) mapping and placement technology

- Available in Xilinx CORE Generator

# **Functional Description**

This macro accepts a bit serial processing clock input, a data-sync (DSYNC), and a data-width signal (TC) on the input pins to control a Serial Distributed Arithmetic (SDA) process. The DSYNC input is used to start the bit serial process by signaling that a new data sample has arrived for processing. The internal control logic will start counting from 0 to a TC equal to N-2 for N-bit data to produce the outputs TSBTC, MSBTC, and HOLD. The DSYNC input is used to trigger the LSB of the SDA process. TSBTC resets the time-skew buffer and MSBTC disables the macros on the MSB of the SDA process until a new data sample is registered. The process is then repeated.

# Pinout

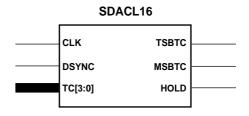

Signal names for the schematic symbol are shown in Figure 1 and described in Table 1.

Figure 1: Core Schematic Symbol

#### **Table 1: Core Signal Pinout**

| Signal | Signal<br>Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK    | Input               | BIT-PROCESSING CLOCK<br>– clocks the SDA bit serial<br>process. Must have a fre-<br>quency of N+1 times or<br>greater than the data clock<br>for N-bit data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DSYNC  | Input               | DATA SAMPLE READY IN-<br>PUT – DSYNC is used to re-<br>set the Control Logic to begin<br>processing the next data<br>sample. When DSYNC is as-<br>serted (HIGH), the input data<br>is registered on the next ris-<br>ing edge of the C (CLOCK).<br>This data is fed into the par-<br>allel-to-serial converter and<br>the DSYNC is propagated<br>through the data flow to trig-<br>ger the LSB input of each<br>cascaded stage of the SDA<br>process. The active duration<br>of DSYNC must be equal to<br>one period, from rising-edge<br>to rising-edge, of the bit pro-<br>cessing clock and remain in-<br>active for at least N clock<br>cycles of the bit processing<br>clock for N-bit data. |

| Table | 1: Co | ore Signa | l Pinout | (cont.) |

|-------|-------|-----------|----------|---------|

|-------|-------|-----------|----------|---------|

| Signal  | Signal<br>Direction | Description                                                                                                                                                                                                                                                                                |

|---------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLD    | Output              | WAIT UNTIL NEXT SAM-<br>PLE – Used to terminate the<br>SDA process. This signal is<br>propagated through the data<br>flow to disable each cascad-<br>ed stage of the SDA process,<br>as required to maintain data<br>integrity for each clock cycle<br>greater than N+1 for N-bit<br>data. |

| TC[3:0] | Input               | TERMINAL COUNT RESET<br>CONSTANT – Used to termi-<br>nate the incrementing of the<br>internal counter at TC equal<br>to N-2 for N-bit data.                                                                                                                                                |

| TSBTC   | Output              | TIME-SKEW-BUFFER TER-<br>MINAL COUNT RESET –<br>Used to reset the TSB<br>Counter at N-1 for N-bit data.                                                                                                                                                                                    |

| MSBTC   | Output              | MOST SIGNIFICANT BIT<br>TERMINAL COUNT – Used<br>to indicate the MSB of the<br>SDA process. This signal is<br>propagated through the data<br>flow to trigger the MSB Out-<br>put of each cascaded stage<br>of the SDA process.                                                             |

## **CORE Generator Parameters**

The CORE Generator dialog box for this macro is shown in Figure 2. The parameters are as follows:

- **Component Name**: Enter a name for the output files generated for this module.

- **Control Width**: Select a control width from the pulldown menu. The valid range is 2-5. The data width is 2 to this power.

| 📽 SDA FIR Control Logic 🛛 🛛 |  |  |  |

|-----------------------------|--|--|--|

| Component Name:             |  |  |  |

| Control Width: 5            |  |  |  |

| Generate Cancel             |  |  |  |

#### Figure 2: CORE Generator Dialog Box

### **Core Resource Utilization**

An RPM is not generated for this module, so the number of CLBs will vary with the Placer tool.

## **Ordering Information**

This macro comes free with the Xilinx CORE Generator. For additional information contact your local Xilinx sales representative, or e-mail requests to dsp@xilinx.com.