# DEVELOPMENT SYSTEM REFERENCE GUIDE VOLUME 3

TABLE OF CONTENTS

GO TO OTHER BOOKS

0401407

# Contents

# Chapter 1 The XDelay Timing Analysis Program

| Graphical Interface                        | 1-2  |

|--------------------------------------------|------|

| Starting XDelay from the Operating System  | 1-2  |

| Starting XDelay from within XACT           | 1-2  |

| Graphical Interface Commands               | 1-3  |

| The Design Menu                            | 1-3  |

| Directory                                  | 1-3  |

| Design                                     | 1-3  |

| Timing Menu                                | 1-3  |

| XDelay                                     | 1-4  |

| XDelay-TimeSpec                            | 1-4  |

| XDelay and XDelay-TimeSpec Command Options | 1-6  |

| Analyze                                    | 1-18 |

| Speed                                      | 1-19 |

| DeleteGroup                                | 1-19 |

| QueryGroup                                 | 1-19 |

| QuerySpec                                  | 1-19 |

| DeleteSpec                                 | 1-19 |

| QueryTemplate                              | 1-19 |

| ClearTemplate                              | 1-19 |

| SaveTemplate                               | 1-19 |

| ReadTemplate                               | 1-20 |

| SetMargins                                 | 1-20 |

| QueryMargins                               | 1-20 |

| ClearMargins                               | 1-21 |

| Savemargins                                | 1-21 |

| Readmargins                                | 1-21 |

| Flagblk                                    | 1-21 |

| QueryBlk                                   | 1-23 |

| QueryNet                                   | 1-23 |

| DRC                                        | 1-23 |

| The Misc Menu                              | 1-23 |

| Help                                       | 1-23 |

| Exit                                       | 1-24 |

|           | Print                                    | 1-24 |

|-----------|------------------------------------------|------|

|           | Printer                                  | 1-24 |

|           | DOS (For PC only)                        | 1-24 |

|           | Report                                   | 1-24 |

|           | Execute                                  | 1-24 |

|           | The Profile Menu                         | 1-25 |

|           | Settings                                 | 1-26 |

|           | Saveprofile                              | 1-26 |

|           | Readprofile                              | 1-26 |

|           | Palette                                  | 1-26 |

|           | Cursor                                   |      |

|           | Mouse                                    | 1-26 |

|           | Keydef                                   | 1-26 |

|           | Keycursor                                |      |

|           | Text Interface                           |      |

|           | Syntax                                   |      |

|           | Options                                  |      |

|           | Features and Capabilities                |      |

|           | TimeGroups                               |      |

|           | Breakloop Option for Combinatorial Logic |      |

|           | Path Delay Searches                      |      |

|           | Timing Margins                           |      |

|           | Environment Variables                    |      |

|           | Template File Format                     |      |

|           | The .xtm File Format                     | 1-32 |

| Chapter 2 | The LCA2XNF Program                      |      |

|           | Syntax                                   | 2-2  |

|           | Files                                    | 2-2  |

|           | Input Files                              | 2-2  |

|           | input.lca                                | 2-2  |

|           | Output Files                             | 2-2  |

|           | output.xnf                               | 2-2  |

|           | output.spc                               | 2-2  |

|           | Options                                  | 2-3  |

|           | Warnings and Error Messages              | 2-5  |

| Warnings                   |              | 2-5 |

|----------------------------|--------------|-----|

| Error Messages and Recover | y Techniques | 2-9 |

# Chapter 3 The XNFBA Program

|           | Files<br>Input Files<br>Output Files<br>post-route file root.mba<br>xnfba.rpt<br>Options<br>Warnings and Error Messages<br>Warnings<br>Error Messages and Recovery Techniques | 3-2<br>3-3<br>3-3<br>3-3<br>3-3<br>3-3<br>3-4<br>3-4 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Chapter 4 | The XACT Design Editor                                                                                                                                                        |                                                      |

|           | Syntax<br>XDE Executive Display                                                                                                                                               |                                                      |

|           | Options                                                                                                                                                                       |                                                      |

|           | Loading and Saving Design Files                                                                                                                                               |                                                      |

|           | Starting XACT Subprograms from XDE                                                                                                                                            |                                                      |

|           | Changing XDE Executive Settings                                                                                                                                               |                                                      |

|           | Leaving the XDE Program                                                                                                                                                       |                                                      |

|           | XDE Executive Commands                                                                                                                                                        |                                                      |

|           | Beep — Control Beep Sound                                                                                                                                                     |                                                      |

|           | ChangePackage — Change LCA Package Type<br>Convert — LCA Part Type Conversion Program                                                                                         |                                                      |

|           | Cursor — Set the Cursor Shape                                                                                                                                                 |                                                      |

|           | Design — Set the Current Design File                                                                                                                                          |                                                      |

|           | Directory — Set the Current Directory                                                                                                                                         |                                                      |

|           | DOS — Enter Temporary DOS Shell (PC only)                                                                                                                                     |                                                      |

|           | DRC — Start the Design Rules Checker                                                                                                                                          |                                                      |

|           | EditLCA — Start the Design Editor                                                                                                                                             | 4-11                                                 |

|           | Execute — Execute a File of Commands<br>Fastsave — Enable/Disable Fast Design File Read/Write                                                                                 | 4-12                                                 |

|           | Operations (PC only)                                                                                                                                                          | 4-12                                                 |

|           | File — Save the Current Design and Leave XDE                                                                                                                                  | 4-13                                                 |

|           | Help — Online Explanation of Editor Commands                                                                                                                                  |                                                      |

|           | Keycursor — Activate Cursor Keys for Pull-Down Menus                                                                                                                          |                                                      |

|           | Keydef — Define A Function Key                                                                                                                                                |                                                      |

|           | MakeBits — Start the Bitstream Generator Program                                                                                                                              |                                                      |

|           | MakePROM — Start the Prom File Formatter                                                                                                                                      |                                                      |

|           | Menucolors — Modify XDE Executive Screen Colors                                                                                                                               |                                                      |

|           | Mode — Set the Mode to Safe or Expert<br>Mouse — Set the Mouse Configuration                                                                                                  |                                                      |

| Namechange — Change the Current Design File Name | 4-18 |

|--------------------------------------------------|------|

| Palette — Select Available Color Palettes        | 4-18 |

| Part — Set the FPGA Part to be Configured        | 4-19 |

| Printer — Set the Printer Type                   | 4-19 |

| Printpic — Print a PIC File                      |      |

| Quit — Leave XDE                                 |      |

| Read — Load a Design File into Memory            | 4-21 |

| Readpalette — Read the palettes.xct File         |      |

| Readprofile — Load XDE Executive Option Settings |      |

| from xact.pro                                    | 4-21 |

| Save — Save Current State of the Design          | 4-22 |

| Saveprofile — Save XDE Executive Option Settings |      |

| in xact.pro                                      |      |

| Settings — Display XDE Executive Option Settings | 4-23 |

| Speed — Select Device Speed Grade                | 4-23 |

| XDE Printer Support                              | 4-23 |

| Unsupported Printers                             |      |

| Printcap.xct File                                |      |

| Printer Commands                                 |      |

| SL (Start of Line) Command                       |      |

| Examples                                         |      |

| Sample printcap.xct                              |      |

| FX80                                             |      |

| HPLASER                                          |      |

| POSTSCRIPT                                       |      |

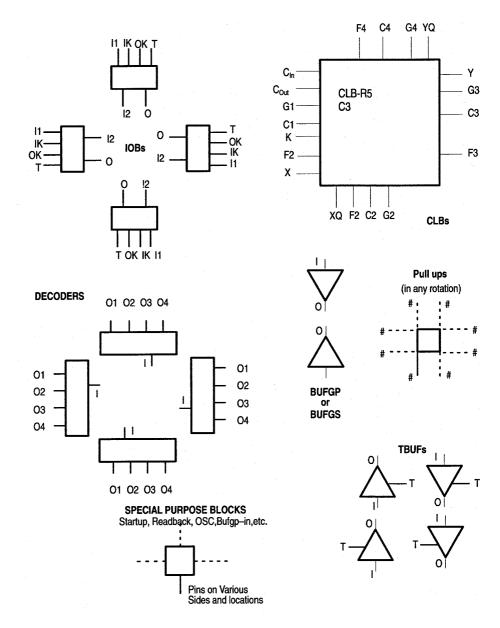

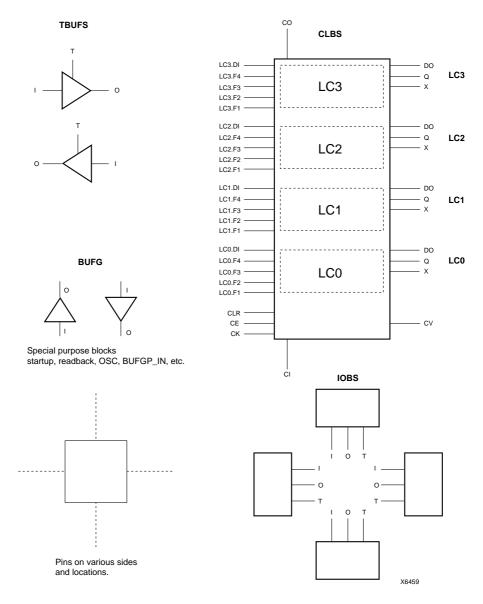

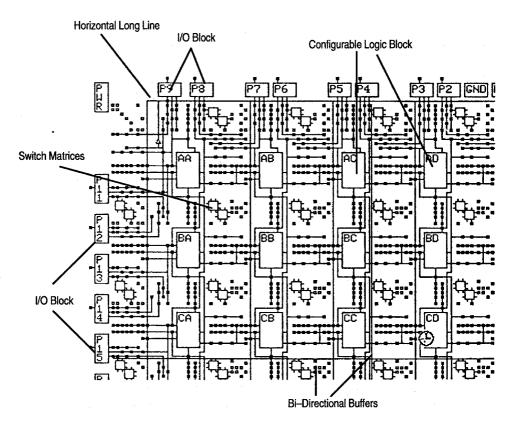

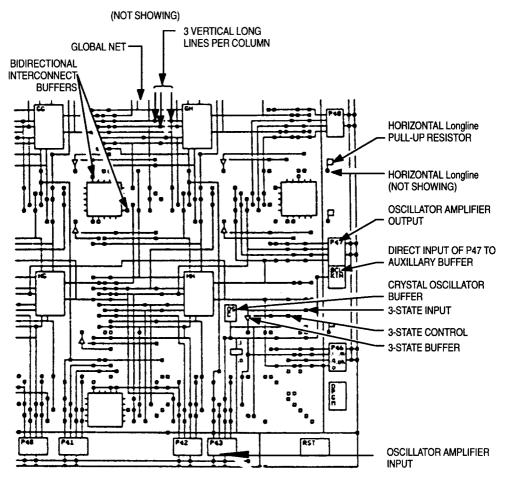

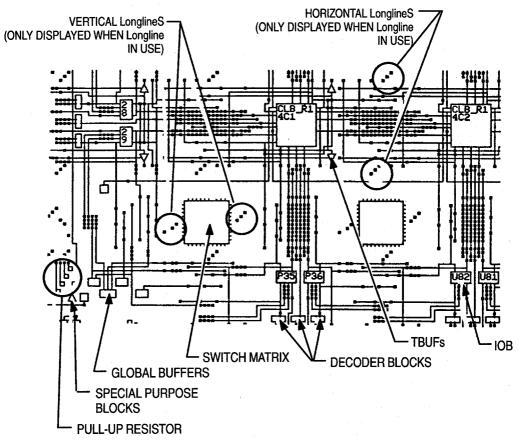

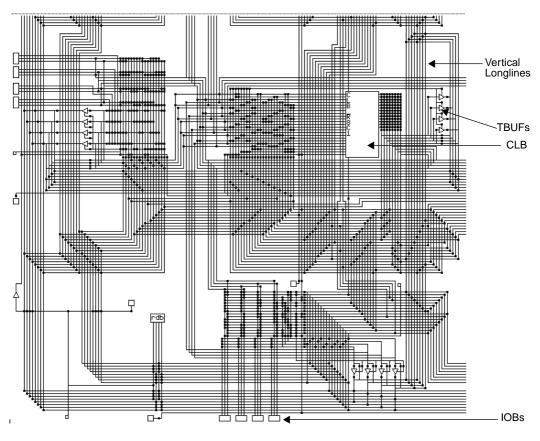

| Design Editor Display                            |      |

| Physical Interconnect Editor Display             |      |

| World View                                       |      |

| FPGA Layout                                      |      |

| Cursor                                           |      |

| Cursor-Status Line                               |      |

| Pull-Down Menus                                  |      |

| Message Line                                     |      |

| Command Line                                     |      |

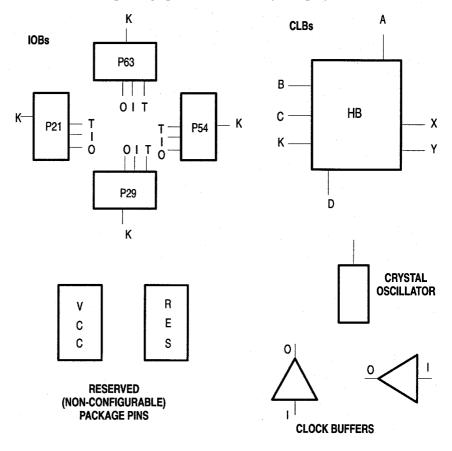

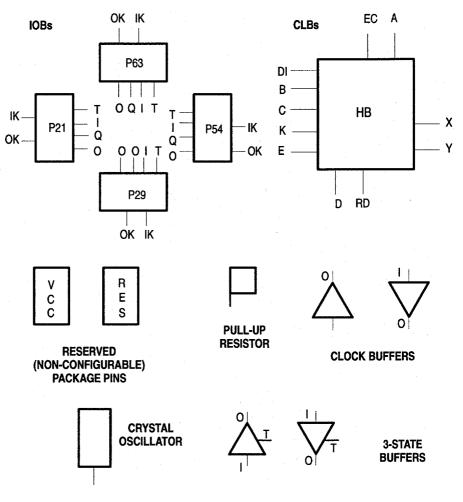

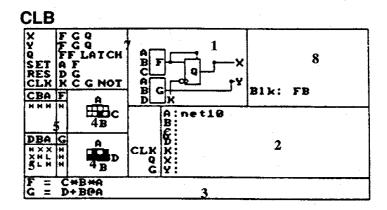

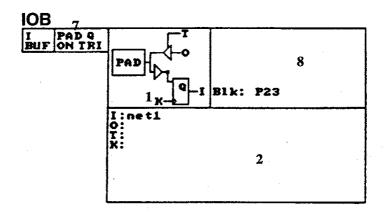

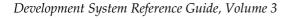

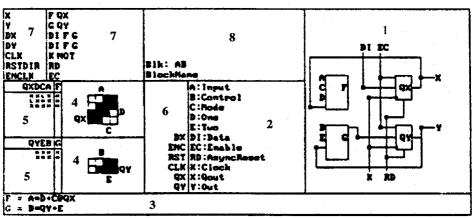

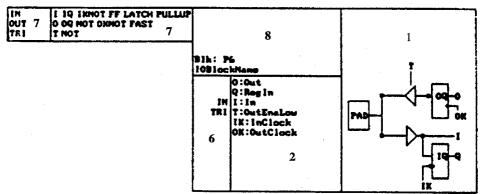

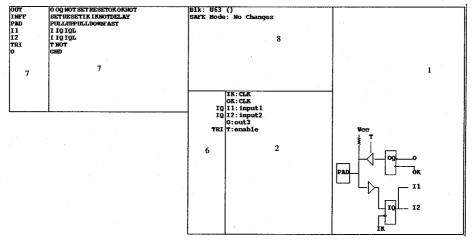

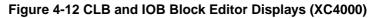

| Block Editor Display                             |      |

| TBUF                                             |      |

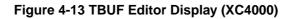

| CLB                                              |      |

| IOB                                              |      |

| Tags                                             |      |

| Command Entry Overview                           |      |

| Mouse Selection of a Command                     |      |

| Keyboard Entry of a Command                                | 4-48 |

|------------------------------------------------------------|------|

| Parameter Selection                                        |      |

| Default Values                                             | 4-48 |

| Pin Names                                                  | 4-48 |

| Block Names                                                | 4-49 |

| Abbreviations                                              | 4-49 |

| Wildcards                                                  | 4-49 |

| Editor Commands                                            | 4-51 |

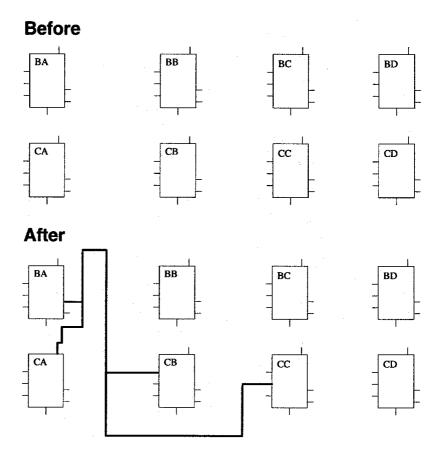

| Addnet — Create a Net                                      | 4-52 |

| Addpin — Add a Pin to a Net                                |      |

| Alignsig — Assign a Net to a Chosen Pin Within Blocks      | 4-54 |

| Assignprobe — Assign an Internal Net to a Predefined Probe | 4-54 |

| Autodrc — Turn Automatic DRC Checking On/Off               |      |

| During Editnet                                             | 4-55 |

| Autoroute — Turn Automatic Routing On or Off               | 4-55 |

| Autotime — Turn Automatic Timing On or Off                 | 4-56 |

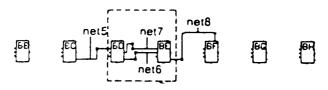

| Base — Change the Base Configuration                       | 4-56 |

| Blkcolors — Assign Colors to Block Editor Display          | 4-59 |

| BlkMenus — Display Scrolling Menus of Blocks               | 4-60 |

| Cdata — Display Configuration Information for a Block      |      |

| Clear — Deconfigure a Tag Setting or Equation              | 4-61 |

| Clearblk — Deconfigure a Block                             | 4-61 |

| Clearmargins — Clear Margin Delays Created by Setmargin    |      |

| ClearTemplate — Clear Defined XDelay Options               | 4-62 |

| Cmtblk — Tag a Block with Comment Text                     | 4-62 |

| Colorblk — Assign a Color to a Block                       | 4-62 |

| Colornet — Assign a Color to a Net                         | 4-63 |

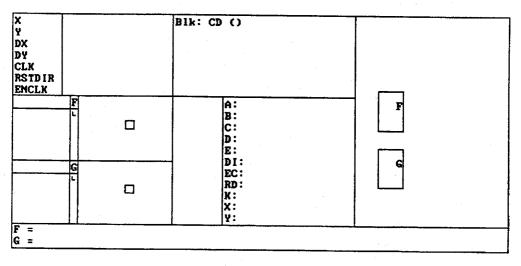

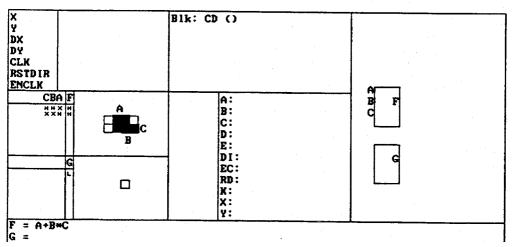

| Config — Configure a Block Logic and Connections           | 4-63 |

| CLB Tag Options (XC2000 Devices)                           | 4-68 |

| CLB Tag Options (XC3000 Devices)                           | 4-68 |

| CLB Tag Options (XC4000 Devices)                           |      |

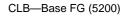

| CLB Tag Options (XC5200 Devices)                           |      |

| IOB Tag Options (XC2000 Devices)                           |      |

| IOB Tag Options (XC3000 Devices)                           |      |

| Clocking Restrictions                                      | 4-71 |

| IOB Tag Options (XC4000 Devices)                           | 4-72 |

| TBUF Tag Options (XC4000 Devices)                          | 4-73 |

| Configcarry — Configure a CLB Carry Logic                  |      |

| Function (XC4000 Only)                                     | 4-74 |

| Configure — Assign MakeBits Configuration Options          |      |

| Copyblk — Copy the Configuration of One Block to Another.  | 4-76 |

| Cursor — Change the Cursor Shape                             | 4-76  |

|--------------------------------------------------------------|-------|

| Cut — Save Part of a Configuration in a File for Moving      | 4-77  |

| Cutmacro — Save a Macro Configuration for Other Locations    | 4-78  |

| Cut Command                                                  |       |

| CUTMACRO Command                                             | 4-80  |

| Debugload — Create a Bitstream and Download to               |       |

| Download Cable                                               | 4-81  |

| Defineprobe — Assign Name to an IOB to Use as Test Point     | 4-81  |

| Delblk — Deconfigure a Block and Delete Pins From Nets       |       |

| Delnet — Delete a Net                                        | 4-84  |

| Delpin — Delete a Pin                                        | 4-84  |

| DOS — Exit XDE Temporarily and Enter DOS (PC only)           | 4-86  |

| Download — Download Bitstream in Memory to                   |       |

| Download Cable                                               |       |

| Draw — Create a Printable File of Design Information         |       |

| DRC — Start the Design Rules Checker                         |       |

| Editblk — Start the Block Editor                             |       |

| Editblkcmt — Edit the Comment Text for a Block               |       |

| Editeq — Edit Equation on Command Line in Block Editor       |       |

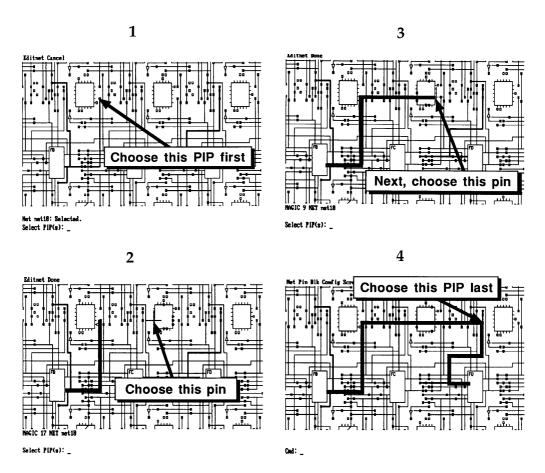

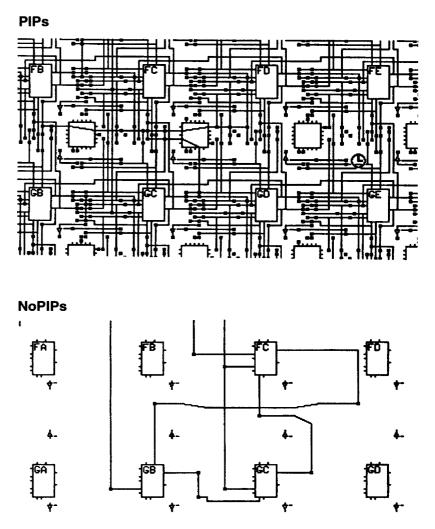

| Editnet — Alter the Routing of a Net                         | 4-90  |

| Toggle a PIP                                                 |       |

| Toggle a Switching Matrix Connection                         |       |

| Endblk — Deselect the Current Block                          |       |

| Endfile — Exit from a Command File                           |       |

| Enprtsc — Enable the Prtsc Key (PC only)                     | 4-94  |

| Eqnetnames — Display Editblock Equations User                |       |

| Net/CLB Pin Names                                            |       |

| Equate — Configure a CLB Logic Function                      |       |

| Execute — Perform Commands from a Command File               |       |

| Exit — Leave Design Editor and Do Not Save Design State      |       |

| File — Save Design State and Leave the Design Editor         |       |

| Find — Move the Cursor and Window to a Location              |       |

| Findblk — Move the Cursor and Window to a Block              |       |

| Findnet — Move the Cursor and Window to a Net                |       |

| Findpin — Move the Cursor and Window to a Pin                |       |

| Flagblk — Flag Blocks for Use with the Path Delay Calculator | 4-102 |

| IOB_Enable_O_I                                               |       |

| Trace Paths From the O Pin to the I Pin                      | 4-102 |

| IOB_Disable_O_I                                              |       |

| Disallow Paths from the O Pin to the I Pin                   | 4-103 |

| IOB_Enable_T_I                                                                          |         |

|-----------------------------------------------------------------------------------------|---------|

| Allow Paths from the T Pin to the I Pin                                                 | 4-103   |

| IOB_Disable_T_I                                                                         |         |

| Disallow Paths from the T Pin to the I Pin                                              | 4-103   |

| TBUF_Enable_I_O                                                                         |         |

| Allow Paths From the I Pin to the O Pin                                                 | 4-103   |

| TBUF_Disable_I_O                                                                        |         |

| Disallow Paths from the I Pin to the O Pin                                              | 4-103   |

| TBUF_Enable_T_O                                                                         |         |

| Allow Paths from the T Pin to the O Pin                                                 | 4-103   |

| TBUF_Disable_T_O                                                                        | 4 4 0 0 |

| Disallow Paths from the T Pin to the O Pin                                              | 4-103   |

| CLB_Enable_WE<br>Allow Paths through Write-Enabled Input of CLB RAM                     | 1-101   |

| CLB_Disable_WE                                                                          | 4-104   |

| Disallow Paths through Write-Enabled Input of CLB RAM                                   | 4-104   |

| CLB_Enable_DIN                                                                          | 1 101   |

| Allow Paths through Data Input(s) of CLB RAM                                            | 4-104   |

| CLB_Disable_DIN                                                                         |         |

| Disallow Paths through Data Input(s) of CLB RAM                                         | 4-104   |

| CLB_Enable_SR_Q                                                                         |         |

| Allow Paths from Async Set/Reset Input to the Q Output .                                | 4-104   |

| CLB_Disable_SR_Q                                                                        |         |

| Disallow Paths from Async Set/Reset Input to the                                        |         |

| Q Output                                                                                | 4-104   |

| FlagIOB — Flag an IO Block for Internal/External Use                                    | 4 4 9 5 |

| (XC2000 and XC3000 only)                                                                |         |

| Flagnet — Flag Specified Net with an Attribute<br>Help — Explain Design Editor Commands |         |

| Hilight — Draw Net Interconnects and Stubs in Color                                     |         |

| Hilightwide — Change the Width of the Highlight Lines                                   |         |

| Joinnet — Merge Nets Together and Deletes Secondary Net                                 |         |

| Keydef — Define a Function Key                                                          |         |

| Macro — Perform Commands from a Macro File                                              |         |

| MakeBits — Create a Bitstream of the LCA File in Memory                                 |         |

| Markblk — Set Constraint File Flag for a CLB or IOB                                     |         |

| (XC2000 and XC3000 only)                                                                | 4-112   |

| Marknet — Set Constraint File Flag for a Net (XC2000                                    |         |

| and XC3000 only)                                                                        | 4-112   |

| Markpin — Set Constraint File Flag for a Pin (XC2000                                    |         |

| and XC3000 only)                                                                        | 4-113   |

| Mouse — Change the Mouse Configuration                   | 4-113 |

|----------------------------------------------------------|-------|

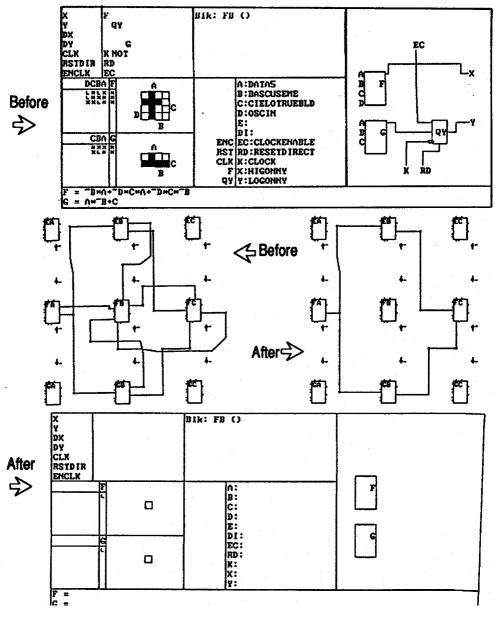

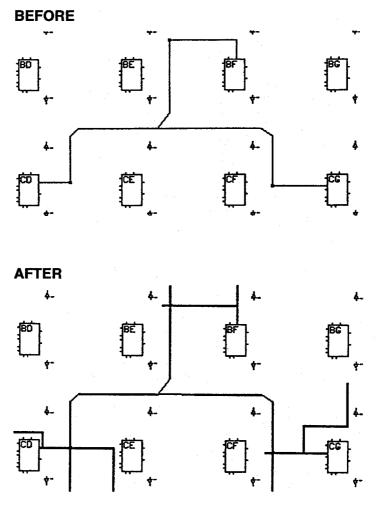

| Moveblk — Move Configuration and Net Connections         |       |

| Between Blocks                                           | 4-114 |

| Movepin — Move a Pin Net Connection to Another Pin       | 4-116 |

| Nameblk — Assign a Name to a Block                       |       |

| Block Name Restrictions                                  |       |

| Namenet — Rename a Net                                   | 4-119 |

| NetMenus — Display Scrolling Menus of Nets               | 4-119 |

| Order — Order CLB Logic Function Inputs                  |       |

| Paste — Perform Commands from a Cut File                 |       |

| Piecolors — Change Color of an Item in Editor Display    |       |

| Port — Select Port for Download Command (PC only)        | 4-123 |

| Print — Create a Printable File of Display Information   | 4-125 |

| Printer — Set the Printer Type for Print Command         | 4-126 |

| Queryblk — Request Data for Blocks                       |       |

| Querygrid — Display the Grid Information of a Location   | 4-131 |

| Querynet — Display Information for a Net                 |       |

| Querymargins — Report Delays for Paths Set by Setmargin. |       |

| Queryprobe — Print a List of Probes and Information      |       |

| Querysaveblk — Display Information about Saved Blocks    |       |

| QueryTemplate — Display List of Current XDelay Options   |       |

| Readbits — Read the Specified Bitstream File             | 4-137 |

| Readcst — Read Constraint File Information               |       |

| (XC2000 and XC3000 only)                                 |       |

| Readmargins — Read Margin Delays from an MRG File        |       |

| Readprobe — Read Set of Probes into the LCA File         | 4-138 |

| Readprofile — Set Editor Options to Settings in          |       |

| editlca.pro File                                         | 4-139 |

| Readscp — Read Schematic Constraint File Information     |       |

| (XC2000 and XC3000 only)                                 |       |

| ReadTemplate — Read XDelay Option File into Memory       |       |

| Redraw — Redraw the Display                              |       |

| Report — Save Block or Net Information in a Text File    |       |

| Restoreblk — Move Saved Information Back into a Block    |       |

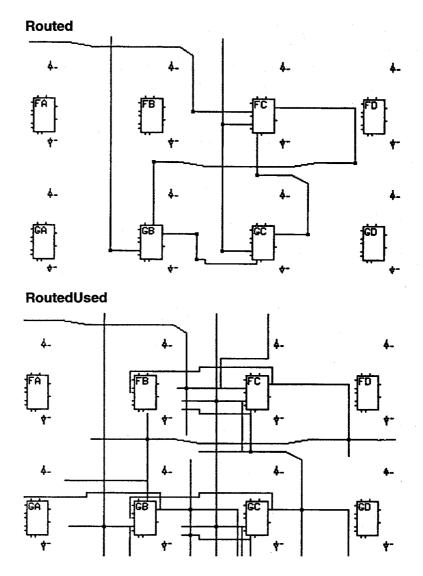

| Route — Configure Interconnect for a Net                 |       |

| Routeblk — Route All the Pins On a Block                 |       |

| Routepin — Configure Interconnect for a Pin              |       |

| Routepoint — Route from Point to Point                   | 4-143 |

| Router — Change Usage Cost Associated with Routing       |       |

| Resources                                                |       |

| Save — Save the Current Design State                     | 4-144 |

| Saveblk — Save a Block to a Scratch Area                                                                  | 4-145                                                                                                             |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Savemargins — Save Margin Delays Set by Setmargins                                                        |                                                                                                                   |

| to an MRG File                                                                                            | 4-145                                                                                                             |

| Saveprobe — Save Current Set of Probes into a PRB File<br>Saveprofile — Save Editor Option Settings in an | 4-146                                                                                                             |

| editlca.pro File                                                                                          | 4-146                                                                                                             |

| SaveTemplate — Save Defined XDelay Options to a File                                                      | 4-147                                                                                                             |

| Setmargins — Add Delay to Clock Paths that Start or                                                       |                                                                                                                   |

| End Off-Chip                                                                                              | 4-147                                                                                                             |

| Setmemory — Specify Power-On Values in ROM                                                                |                                                                                                                   |

| (XC4000 Only)                                                                                             |                                                                                                                   |

| Settings — Display Current Values of Editor Settings                                                      |                                                                                                                   |

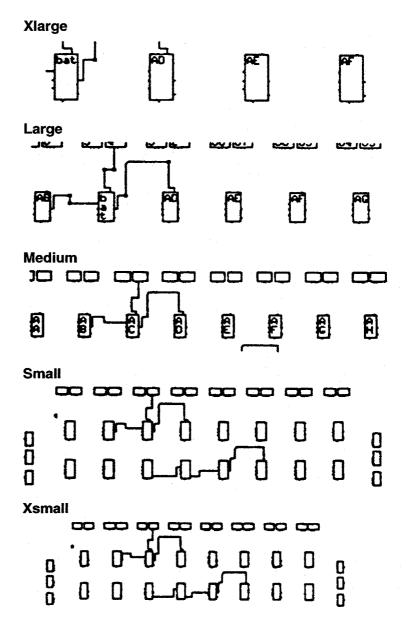

| Show — Change the Display Options                                                                         | 4-148                                                                                                             |

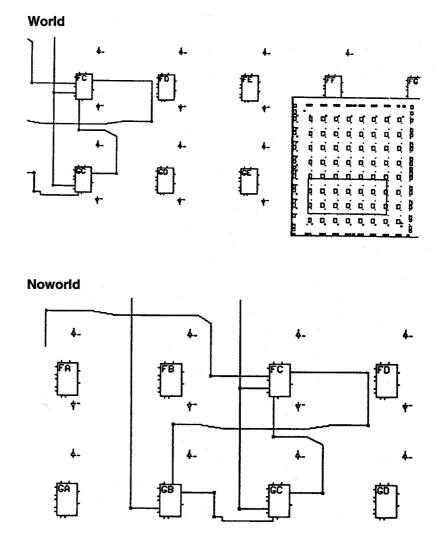

| ShowBlkConn — Highlight Block Connections in the                                                          |                                                                                                                   |

| World View                                                                                                |                                                                                                                   |

| ShowNetConn — Highlight Nets in the World View                                                            | 4-155                                                                                                             |

| Snap — Relocate Cursor to Nearest Pin or Pip when Parked                                                  |                                                                                                                   |

| Speed — Select Device Speed Grade                                                                         |                                                                                                                   |

| Splitnet — Split a Net into Two Distinct Nets                                                             | 4-156                                                                                                             |

| StatusLine — Select Status Line Format                                                                    | 4-156                                                                                                             |

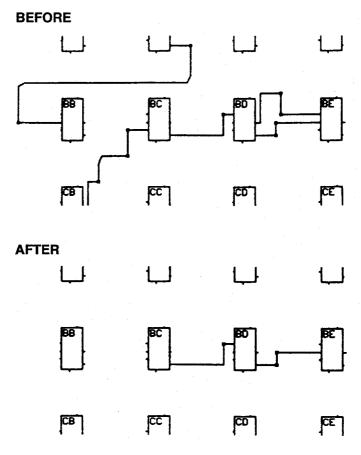

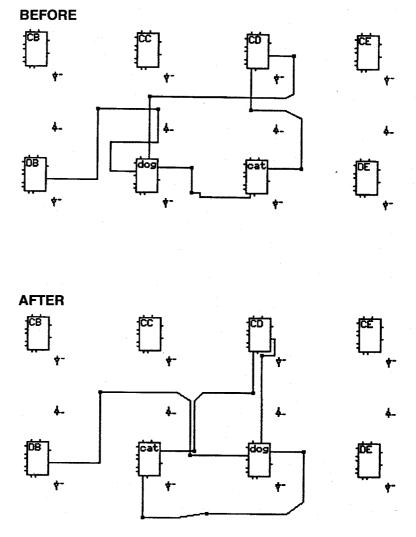

| Swapblk — Swap Configurations and Net Connections                                                         |                                                                                                                   |

| emap eeningulatione and not eenineetione                                                                  |                                                                                                                   |

| of Two Blocks                                                                                             | 4-157                                                                                                             |

|                                                                                                           |                                                                                                                   |

| of Two Blocks                                                                                             | 4-159                                                                                                             |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162                                                                                           |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162                                                                                  |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162                                                                         |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163                                                                |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163                                                       |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163                                              |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163                                              |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163<br>4-164                                     |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163<br>4-164                                     |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163<br>4-164<br>4-164                            |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163<br>4-164<br>4-164                            |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163<br>4-164<br>4-164                            |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163<br>4-164<br>4-164<br>4-165                   |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163<br>4-164<br>4-164<br>4-165<br>4-165          |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163<br>4-164<br>4-165<br>4-165<br>4-165          |

| of Two Blocks                                                                                             | 4-159<br>4-160<br>4-162<br>4-162<br>4-162<br>4-163<br>4-163<br>4-163<br>4-164<br>4-165<br>4-165<br>4-165<br>4-165 |

| Index | i |

|-------|---|

|       |   |

# **Trademark Information**

# Chapter 1

# The XDelay Timing Analysis Program

This program is compatible with the following families.

- XC2000

- XC2000L

- XC3000

- XC3000A

- XC3000L

- XC3100

- XC3100A

- XC4000

- XC4000A

- XC4000H

- XC5200

The XDelay program is a static timing analysis tool that reports the timing delays of a routed FPGA design. XDelay can create a detailed list of delay paths, and provide a design analysis, including estimates of system performance for each clock in the design.

XDelay has two modes: interactive and batch. The interactive mode is available within the XACT environment and the operating system prompt. The batch mode is only available from the operating system prompt. The graphical interface provides you with interactive menu access to the commands and options; the batch mode provides you with text–based command syntax interface.

# **Graphical Interface**

The graphical interface provides a menu–driven environment for you to use XDelay. This interface consists of pull–down menus that contain commands and options to specify design information used in timing analysis.

- You can start XDelay from the operating system prompt.

- You can use XDelay from the XACT environment by selecting XDE (XACT Design Editor), starting the EditLCA program, and selecting XDelay from the Timing menu.

# Starting XDelay from the Operating System

You can call XDelay by typing the program name only at the operating system prompt.

xdelay

**Note:** If you type any options after the command name, you start the XDelay program in batch mode. Details about this interface appear later in this chapter.

The "Graphical Interface" section describes the menus and commands that are available in the graphical user interface.

# Starting XDelay from within XACT

You can use XDelay from within the XACT environment by first starting XDM (XACT Design Manager). With the XDM screen open you then have two ways to select and run XDelay.

One way is start XDelay directly. To do this, place the mouse pointer on the Verify menu and select XDelay (Static Delay Analyzer). A list of XDelay command options appear on a pull-down menu from which you make selections. If you select any of these options, XDelay starts up in the batch (non-interactive) mode. For information about these options, refer to the "Text Interface" section, later in this chapter.

You can also run the XDelay command from within XDE. To do this, you must start XDM. When the XDM screen appears, select XDE from the PlaceRoute menu. When the XDE screen appears, select EditLCA from the Programs menu. EditLCA is the graphical editor for your

FPGA design. Once EditLCA has started, select XDelay options from the Timing menu.

# **Graphical Interface Commands**

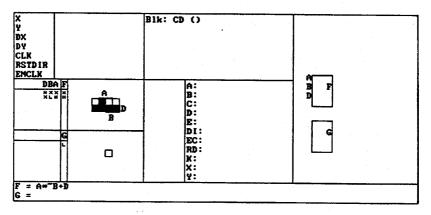

This section describes the commands available in the XDelay graphical interface. The XDelay executive manager graphical interface has four menus (Design, Timing, Misc, and Profile) and a command line (on PCs, at the bottom of the screen; on workstations, at the top of the screen).

You can use a menu selection or command-line entry to run XDelay commands. If a submenu appears, you can directly select from the submenu or type commands from the keyboard. Each menu item entry highlights the valid keyboard shortcut for entering the command or option on the command line either with a different color on color monitors, or capital letters.

# The Design Menu

The Design menu contains commands that allow you to specify your working directory, and select a design from your working directory.

#### Directory

The Directory command allows you to change the current working directory from a list of available directories. You choose a design to analyze from the current working directory.

# Design

The Design command allows you to select your design from the designs in the current directory. After you choose the design, XDelay loads it into memory.

# **Timing Menu**

The Timing menu contains commands that allow you to choose three different modes of reporting timing delay information. If you want detailed information about specific paths in the design, use the XDelay command. If you want to compare the implementation of the design against the original XACT-Performance TimeSpec constraints, use the XDelay-TimeSpec command. If you want a summary of the

overall performance of the design, use the Analyze command. In addition, the Speed command allows you to change the current speed grade for the design.

The Timing menu also contains several commands that allow you to:

- Create, delete, and list elements of specified TimeGroups

- Set, delete, and list currently defined Time Specifications

- Save, read, clear, and list current template files

- Set, clear, save, and read currently defined margin (timing delays)

- Enable or disable report information about special block delays

- Report information about nets in the current design

- Run DRC (Design Rules Checker) on the current design.

#### **XDelay**

XDelay reports detailed timing information about your design. The report contains the worst-case path delays for the set of selected paths.

You can specify a path in one of two ways.

- Select starting points and ending points (to and from)

- Specify a path type to follow

The starting point or path source can be any point where a timing path can begin, typically an input IOB, or the output of a flip–flop or latch. The ending point or path load (path destination) can be any point where a timing path ends, typically an output IOB, or the input of a flip-flop or latch.

For example, using starting and ending points, you can trace every input pad that eventually connects to a flip-flop. You can specify a certain path type by tracing all flip-flop outputs that connect to flipflop inputs.

#### XDelay-TimeSpec

XDelay-TimeSpec compares the implementation of the design with the original XACT-Performance TimeSpec constraints that were defined by the user. The report generated by this command summarizes the paths for each selected TimeSpec and indicates whether the paths passed or failed the timing specification limit.

The following table summarizes the commands available in the submenus for the XDelay and XDelay-TimeSpec Commands. These options are described in detail later in this document.

| XDelay Sub-Menu Options | XDelay-TimSpec Sub-Menu<br>Options |

|-------------------------|------------------------------------|

| -From                   | -SelectSpec                        |

| -FromIOB                | -FailedSpec                        |

| -FromFF                 | -Unspecified                       |

| -FromAll                | -TSMaxpaths                        |

| -То                     | -NoTimeGroups                      |

| -ToIOB                  |                                    |

| -ToFF                   |                                    |

| -ToAll                  |                                    |

| -PadToPad               |                                    |

| -PadToSetup             |                                    |

| -ClockToPad             |                                    |

| -ClockToSetup           |                                    |

| -ClockInput             |                                    |

| -SourceClock            |                                    |

| -NoSourceClock          |                                    |

| -DestClock              |                                    |

| -NoDestClock            |                                    |

| -BreakLoop              |                                    |

| -NoBreakLoop            |                                    |

Table 1-1 XDelay TimeSpec Commands

| Common Options in XDelay and XDelay-TimeSpec Sub-Menus |  |

|--------------------------------------------------------|--|

| -WorstCase                                             |  |

| -IgnoreNet                                             |  |

| -NoIgnoreNet                                           |  |

| -Netfilter                                             |  |

| -NoNetfilter                                           |  |

| -Delayless                                             |  |

| -Delaygreater                                          |  |

| -Widereport                                            |  |

| -Shortreport                                           |  |

| -Sort                                                  |  |

| -Maxpaths                                              |  |

| -ClearOptions                                          |  |

#### XDelay and XDelay-TimeSpec Command Options

The following list describes the options within the XDelay and XDelay-TimeSpec commands. You select an option by typing that option on the command line or selecting with the mouse from the menu.

• -From

-From allows you to specify starting points for the path-delay calculator. Starting points can be pins, blocks, nets, or a wildcard (\*) to represent all sources.

• -FromIOB

-FromIOB allows you to select IOBs as starting points for the path-delay calculator from a menu of valid IOBs. This option requires that the BlkMenus option be enabled if you have invoked XDelay from the XACT Design Editor.

-FromFF

-FromFF allows you to select flip–flop nets as starting points for the path–delay calculator from a menu of valid flip–flop nets. Flip–flop nets are named by their output net names. You can select the source net from this menu, or enter it from the keyboard. This option requires that the NetMenus option be enabled if you have invoked XDelay from the XACT Design Editor.

-FromAll

-FromAll allows you to select paths to begin at any path source.

• -To

-To allows you to select the ending points for the path-delay calculator. Ending points can be pins, blocks, nets, or a wild card (\*) to represent all destinations.

-ToIOB

-ToIOB allows you to select IOBs as path loads ending points for the path-delay calculator from a menu of valid IOBs. This option requires that the BlkMenus option be enabled if you have invoked XDelay from the XACT Design Editor.

-ToFF

-ToFF allows you to select flip–flop nets as ending points from a menu of valid flip–flop output nets.

-ToAll

-ToAll allows you to select paths to end at any path destination. This option is the default.

-SelectSpec

-SelectSpec allows you to select user-defined TimeSpecs (timing specifications) to analyze. This option causes the report to summarize the paths for each selected timespec and indicate whether the paths passed or failed the timing specification limit.

• -FailedSpec

-FailedSpec allows you to restrict XDelay to only print the paths that do not meet your timing specifications.

• -Unspecified

-Unspecified allows you to include paths that are not specified by any TimeSpec in the XDelay report. This option has no effect if all timing paths have a TimeSpec. -NoTimeGroups

-NoTimeGroups prevents XDelay from listing the members of each TimeGroup at the beginning of a report. Since this information can be lengthy, the -NoTimeGroups option is on by default.

-SourceClock

-SourceClock allows you to set the selected clock net to be the starting point for all path searches. You can select multiple clock nets at the same time. This starts the path searches only at the flipflops or latches that are clocked by the specified clock signal.

You must specify the active edge (rising, falling, or any) of the clock. Specifying the active edge limits the delay report to paths that start or end on rising, falling, or any clock edge.

-NoSourceClock

-NoSourceClock allows you to clear any previously defined source clocks.

-DestClock

-DestClock allows you to set the selected clock net to be the ending point for all path searches. You can select multiple clock nets at the same time. This option ends the path searches at all the flip-flops or latches that are clocked by the specified clock signal.

You must specify the active edge (rising, falling, or any) of the clock. Specifying the active edge limits the delay report to paths that start or end on rising, falling, or any clock edge.

-NoDestClock

-NoDestClock allows you to clear any previously defined destination clocks.

-Ignorenet

-Ignorenet allows you to specify which nets to ignore. You can use this option to specifically avoid tracking false paths through illegal–state reset logic.

-NoIgnorenet

-NoIgnorenet allows you to clear any previously defined Ignorenets.

• -Netfilter

-Netfilter allows you to restrict the path tracer only to paths passing through netfilter nets. Paths that do not contain any netfilter nets are not reported.

-NoNetfilter

-NoNetfilter allows you clear any previously defined Netfilter nets. When you select this option, XDelay reports all traced paths, not just paths with previously specified filter nets.

**Note:** The SourceClock, DestClock, IgnoreNet and Netfilter options present menus of all valid nets only when NetMenus is enabled if you have invoked XDelay from the XACT Design Editor.

-BreakLoop

-BreakLoop allows you to mark nets as synchronous sources. XDelay treats these nets similarly to flip–flops. Timing paths can begin and end at the specified BreakLoop but not go through them. This allows output of latches built from combinational logic to be treated as synchronous timing elements. For more information refer to the discussion of "BreakLoops" later in this chapter.

This is similar to the Flagblk -Synchronous option, except that -BreakLoop provides a more resolute way to specify synchronous outputs.

-NoBreakLoop

-NoBreakLoop allows you to remove all existing BreakLoops.

**Note:** -PadToPad, -PadToSetup, -ClockToSetup, -ClockToPad, and -ClockInput are complementary, not mutually exclusive. For example, if you select both -PadToPad and -PadToSetup, XDelay reports on both types of paths.

• -PadToPad

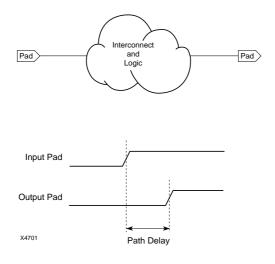

-PadToPad allows you to restrict the report to paths that start at input pads and end at output pads. See Figure 1-1.

#### Figure 1-1 Pad To Pad Path

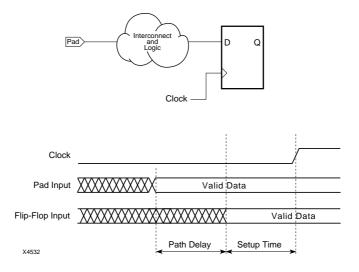

-PadToSetup

-PadToSetup allows you to restrict the report to paths that start at input pads and end at flip–flops or RAM. Figure 1-2 shows an example of a path from an input pad to a flip-flop data input.

#### Figure 1-2 Pad To Setup Path

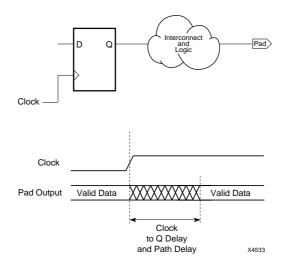

-ClockToPad

-ClockToPad allows you to restrict the report to paths that start at flip-flop outputs and end at output pads. See Figure 1-3.

#### Figure 1-3 Clock To Pad Path

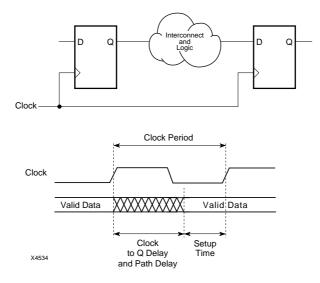

-ClockToSetup

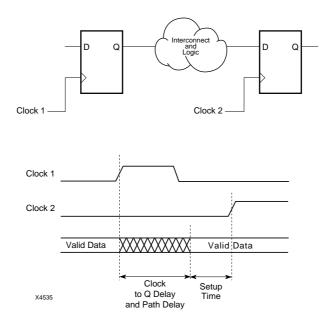

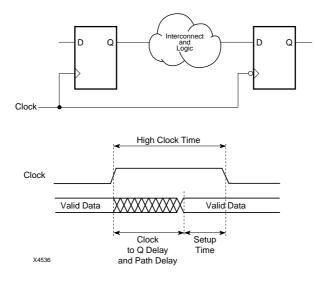

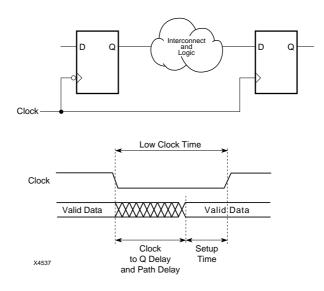

-ClockToSetup allows you to restrict the report to paths that start at flip-flop and RAM outputs and end at clocked inputs, such as flip-flop data inputs. Refer to Figure 1-4 through Figure 1-7.

#### Figure 1-4 Clock To Setup Path, Same Active Clock Edge

Figure 1-5 Clock To Setup Path, Different Clock Net

#### Figure 1-6 Clock To Setup Path, Rising Edge To Falling Edge

Figure 1-7 Clock To Setup Path, Falling Edge To Rising Edge

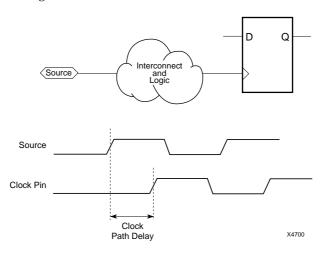

-ClockInput

-ClockInput allows you to restrict the report to option paths that end at flip–flop clock pins. These paths can start anywhere. See Figure 1-8.

#### Figure 1-8 Clock Input Path

-Delayless

-Delayless allows you to set a maximum path-delay in nanoseconds. Only paths with delay less than or equal to this value are reported.

-Delaygreater

-Delaygreater allows you to set a minimum path-delay in nanoseconds. Only paths with delay greater than or equal to this value are reported.

-TSMaxpaths

-TSMaxpaths allows you to limit the number of paths reported for each TimeSpec in the XDelay report to a number specified in *path count*.

-Maxpaths

-Maxpaths allows you to limit the number of paths reported. If you use this option while using TimeSpecs, you affect the total

number of paths in the system, not the total number for each TimeSpec. This option is also useful when the system memory is limited, since the *path count* also limits how many paths are stored in memory while tracing paths. If XDelay runs out of memory, assigning a Maxpaths *path count* value is the easiest fix.

-Widereport

-Widereport allows you to set the output format to 132 characters per line. This can prevent long block and net names from being truncated in a report.

-Shortreport

-Shortreport allows you to print one delay path per line. It only lists path sources and path loads, without further detailed path information.

-Sort

-Sort allows you to change the order that paths are reported. The default is to order paths from longest to shortest delay. The valid Sort options are listed below.

- *Delaylong* lists path delays in order from largest to smallest delay (default value).

- *Delayshort* lists path delays in order from smallest to largest delay.

- *Destblock* sorts path delays by the name of the destination block. This is useful when trying to group a set of path–delays that all end at one block. It makes it easy to find the worst-case path to each block.

- *Srcblock* sorts path delays by the name of the source block. This is useful when trying to determine the worst-case path from a given block.

- *Srcclocknet* sorts path delays by the name of the clock that sources the first element in the path. This is useful when you want to separate delay information for two or more clock nets in one design.

- *Destclocknet* path delays are sorted by the name of the clock that sources the last element in a path.

-WorstCase

-WorstCase allows you to restricts the display to the path with the longest delay if there is more than one path between a path source and a path destination.

-ClearOptions

-ClearOptions allows you to restore all XDelay options and restores them to their default values.

#### Analyze

Analyze allows you to get a best–case timing analysis of a design. XDelay computes a maximum toggle rate for each clock net in the system and reports some speed–limiting path information.

Since all on–chip hold times on Xilinx parts are 0, these hold times do not figure into the analysis.

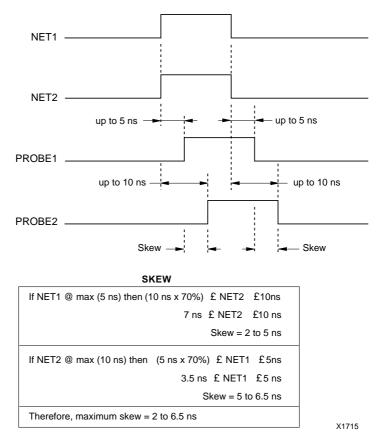

The XDelay timing analysis presents a chip-level view of system timing. There is no adjustment for off-chip delays, so you may want to add some timing margin to the off-chip connections to account for board-level skew and/or setup requirements of other devices. See the "SetMargins" section later in this chapter.

The following requirements apply:

- The clock period for PadToSetup paths and ClockToPad paths must be longer than the maximum path delay, plus any external input timing margin.

- The clock period for ClockToSetup paths (with the same active clock edge) must be longer than the maximum path-delay plus any clock skew between the flip-flops in the path.

- The clock period for ClockToSetup paths (with different clock nets) must be longer than the maximum path delay.

- The clock period for ClockToSetup paths (rising edge to falling edge) must be longer than the maximum path delays plus any clock skew.

- The low time of the clock signal for ClockToSetup paths (falling edge to rising edge) must be longer than the maximum path delay, plus any clock skew.

**Note:** The report produced with the Analyze option describes chip-level performance, not system–level performance.

#### Speed

The Speed command allows you to change the current speed grade of your design. You must re–run XDelay to see how changing the speed grade affects design performance.

#### DeleteGroup

DeleteGroup allows you to delete specified groups.

# QueryGroup

QueryGroup allows you to get a list of the elements of each specified delay group. If you do not specify any groups, it lists all defined groups.

# QuerySpec

QuerySpec allows you to list currently defined TimeSpec. If no TimeSpec is specified, QuerySpec reports all defined TimeSpecs.

#### DeleteSpec

DeleteSpec allows you to delete TimeSpecs.

# QueryTemplate

QueryTemplate allows you to print a list of the current XDelay settings. This is similar to the Settings command in XDM and XDE.

# ClearTemplate

ClearTemplate allows you to delete any previously defined XDelay options and restores them to their default.

# SaveTemplate

The SaveTemplate command allows you to save the currently defined XDelay options, margins, and Flagblk settings to the named template file. The file extension must be .xtm.

If an XTM file is read that has been created by means other than the SaveTemplate command, the SaveTemplate command might write a new template file that appears different than the original. The new template file is logically equivalent, but the sequence and content of the template file commands can be different. This happens because the contents of the template file are read and translated into an internal non-text form, and are re-translated from this internal form back into text the command. For information about the .xtm file format, refer to the "Template File Format" section later in this chapter.

# ReadTemplate

The ReadTemplate command allows you to get a list of XDelay settings from a template file (XTM).

These settings are added to the settings already in memory. If you want to use the file as the only settings, then you first run ClearTemplate. For information about the .xtm file format, refer to the "Template File Format" section later in this chapter.

# **SetMargins**

The SetMargins command allows you to add extra delay onto pad paths that come from, or go to, off–chip. See Figure 1-1 and Figure 1-2.

Adding this extra delay allows you to get a more realistic system clock speed, sine there is always some delay in the path, external to the Xilinx device. SetMargins allows you to add this sort of delay to those paths that travel off-chip.

SetMargins prompts for a path type, which can be either PadToSetup or ClockToPad. It then asks for a clock net to be used as the reference clock where these delays begin or end. Finally, it prompts for the delay margin to add to the internal path delay.

# QueryMargins

The QueryMargins command allows you to get all the currently defined Margins.

# ClearMargins

The ClearMargins command allows you to remove all defined margins.

# Savemargins

The Savemargins command appears on the menu, but is not functional. Use SaveTemplate to save timing margins.

#### Readmargins

The Readmargins command allows you to read the timing margins that SaveTemplate saved back into the FPGA.

# Flagblk

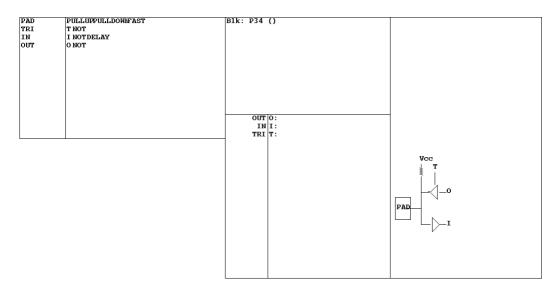

The Flagblk command allows you to mark certain blocks to enable or disable some special block delays, when Blkmenus is enabled.

These flags can help decrease the number of false paths in many cases. The following list describes the flags available with Flagblk.

IOB\_Enable\_O\_I

IOB\_Enable\_O\_I allows paths from the IOB O pin to the pad and back into the chip through the IOB I pin.

IOB\_Disable\_O\_I

IOB\_Disable\_O\_I disallows paths from the IOB O pin to the pad and back into the chip through the IOB I pin. This flag is the default.

**Note:** IOB\_Enable\_O\_I and IOB\_Disable\_O\_I only affect bidirectional IOBs with 3–state outputs.

IOB\_Enable\_T\_I

IOB\_Enable\_T\_I allows paths from the IOB T pin to the pad and back into the chip through the IOB I pin.

• IOB\_Disable\_T\_I

IOB\_Disable\_T\_I disallows paths from the IOB T pin to the pad and back into the chip through the IOB I pin. This flag is the default. • TBUF\_Enable\_I\_O

TBUF\_Enable\_I\_O allows paths that go through the TBUF I pin to the TBUF O pin. This flag is the default.

TBUF\_Disable\_I\_O

TBUF\_Disable\_I\_O disallows paths from a TBUF I pin to the TBUF O pin.

• TBUF\_Enable\_T\_O

TBUF\_Enable\_T\_O allows paths that go through a TBUF T pin to the TBUF O pin. This flag is the default.

• TBUF\_Disable\_T\_O

TBUF\_Disable\_T\_O disallows paths that go through a TBUF T pin to the TBUF O pin.

• CLB\_Enable\_WE

CLB\_Enable\_WE allows paths through the write–enable input of CLB RAM.

• CLB\_Disable\_WE

CLB\_Disable\_WE disallows paths through the write–enable input of CLB RAM. This flag is the default.

• CLB\_Enable\_DIN

CLB\_Enable\_DIN allows paths through DATA inputs of a CLB RAM.

CLB\_Disable\_DIN

CLB\_Disable\_DIN disallows paths through DATA inputs of a CLB RAM. This flag is the default.

• CLB\_Enable\_SR\_Q

CLB\_Enable\_SR\_Q allows paths through CLB flip-flop Asynchronous Set or Reset inputs. This flag is the default for Asynchronous Set/Reset paths.

• CLB\_Disable\_SR\_Q

CLB\_Enable\_SR\_Q disallows paths through CLB flip–flop Asynchronous Set or Reset inputs.

• Synchronous

Synchronous allows you to mark the output from all function generators in the selected blocks as synchronous outputs. XDelay treats these outputs like nets marked in XDelay -Breakloop.

This option, however, can flag logic as being synchronous when it is not because the outputs are not treated individually.

• Not\_Synchronous

Not\_Synchronous allows you to clear selected blocks as synchronous outputs.

#### QueryBlk

The QueryBlk command allows you to get information blocks in the current design. See "The XACT Design Editor" chapter in this reference guide for more information.

#### QueryNet

The QueryNet command allows you to get information about nets in the current design. See "The XACT Design Editor" chapter in this reference guide for more information.

#### DRC

The DRC command allows you to start the Design Rules Checker (DRC) for the current design. See "The XACT Design Editor" chapter in this reference guide for more information.

# The Misc Menu

This menu contains commands that allow you to use the online help facility, quit out of XDelay, select printer format, escape to the DOS shell (PC only) without quitting XDelay, create a report file, and run a batch file.

#### Help

The Help command allows you to bring up online help text on specific commands within the XDelay program.

Alternately, you can use the mouse to point at any command or option from the menu, and press the F1 key to bring up the associated help text. Pressing F1 again clears the help text.

# Exit

The Exit command allows you to quit from the XDelay program.

#### Print

The Print command allows you to print all or part of the XDelay display in a format you determine with the Printer command. Two options are available:

- Display prints the display, less the status line and any menus that might be present

- Screen prints the entire display including menus

#### Printer

The Printer command allows you to determine the format of file that Print creates.

You can change the initial value for the printer type in the xdelay.pro file; the normal initial value is IBMGRAPH. See Table 1-2 for a list of valid printer options.

# DOS (For PC only)

The DOS command allows you to temporarily suspend XDelay and open an MS–DOS shell. Type Exit at the shell prompt to return to the XDelay program.

# Report

The Report command allows you to redirect the screen output of the XDelay, QueryNet, DRC, or QueryBlk commands to a disk file.

# Execute

The Execute command allows you to perform a set of commands from a batch file. Use this command to reduce the number of commands entered redundantly, or to execute a special sequence of commands that are to be performed multiple times.

| Selection       | Printer                                  |

|-----------------|------------------------------------------|

| FX80            | Epson FX80                               |

| FX85            | Epson MX85                               |

| FX86            | Epson MX86                               |

| FX100           | Epson FX100                              |

| FX185           | Epson FX185                              |

| FX286           | Epson FX286                              |

| HPL300          | Hewlett Packard Laserjet Printer 300 dpi |

| HPLASER         | Hewlett Packard Laserjet Printer         |

| HPLASER-A4      | Hewlett Packard Laserjet Printer-A4      |

| HPLPLUS         | Hewlett Packard Laserjet Plus Printer    |

| HPLPLUS-A4      | Hewlett Packard Laserjet Plus Printer-A4 |

| HPLPLUSLEGAL    | Hewlett Packard Laserjet Plus            |

| HPLPLUSLEGAL-A4 | Hewlett Packard Laserjet Plus-A4         |

| IBMgraph        | IBM Graphics Printer                     |

| MX80            | Epson MX80                               |

| MX100           | Epson MX100                              |

| NEC             | Nippon Electric Corp.                    |

| NECBIG          | Nippon Electric Corp. (expanded)         |

| OKI92           | Okidata Microline 92                     |

| OKI93           | Okidata Microline 93                     |

| OKI292          | Okidata Microline 292                    |

| OKI293          | Okidata Microline 293                    |

| POSTSCRIPT      | Postscript Format Printer                |

| RX80            | Epson RX80                               |

#### Table 1-2 List of Printers and Print Formats

# The Profile Menu

The Profile menu contains commands that allow you to display your XDelay options, save and read your xdelay.pro file, change the menu colors on your color monitor, change your cursor shape, define your mouse buttons, and define your keyboard function keys.

### Settings

The Settings command allows you to display the currently defined options within the XDelay program, such as palette default, cursor type, printer type, mouse button configuration, keyboard definitions, etc.

## Saveprofile

The Saveprofile command allows you to save the current settings palette color, printer type, keyboard definitions within the program to the xdelay.pro file.

## Readprofile

The Readprofile command allows you to read the current settings palette color, cursor type, mouse button configuration into memory from the xdelay.pro file.

### Palette

The Palette command allows you to choose a palette from which you select the colors of the menu.

#### Cursor

The Cursor command allows you to control the shape of the cursor. You can choose an arrow, bug, cross, or gunsight.

### Mouse

The Mouse command allows you to define the mouse buttons as Select, Done, Menu or Switch.

## Keydef

The Keydef command allows you to define the keyboard function keys as XDelay commands.

## Keycursor

The Keycursor command allows the arrow keys to move the cursor through pull-down menus. It also executes the selected option when

you press  $\dashv$ . If Keycursor is off, you must enter commands using the mouse, or by typing the commands via the keyboard.

## **Text Interface**

You can start XDelay from the operating system prompt and use the text interface. The text interface allows you to specify XDelay options in command line syntax.

Using the text interface, you can run template files in batch mode to get delay information about your design.

## **Syntax**

The following command line syntax starts the program.

>xdelay [options] design

If you do not specify options when you start xdelay at the operating system prompt, you start the graphical interface, not the text interface. Further, if you run XDelay on a design without the -s or -x option, it will generate the analyze report. This report type is the default.

## Options

If you run XDelay with the design name, you get analysis mode. This is the default. The options available with the text interface are described below.

#### -help

-help allows you to display the command line help screen.

#### -d

-d allows you to exit out of XDelay without creating a timing report. Use with the -w option to rewrite the LCA file with net delays without producing a delay report.

#### -o output file

-o allows you to redirect the timing report to the specified output file.

#### -S

-s allows you to generate the timing report in the short report format.

#### -t template file

-t allows you to specify a template file that XDelay reads for path tracing options. You can create a template file in the graphical user interface, or use an editor to create a template file. See the SaveTemplate and ReadTemplate command descriptions for more information. The template file name must have a .xtm extension. For information about the .xtm file format, refer to the "Template File Format" section later in this chapter.

#### -timespec

-timespec directs XDelay to compare the implementation of the design with the original XACT-Performance TimeSpec constraints that were defined by the user. The report generated by this option summarizes the paths for each selected TimeSpec and indicated whether the paths passed or failed the timing specification limit.

#### -u speed

-u allows you to override the speed grade in the FPGA design. You can use this option with the -w or -x switches to generate timing reports for different speed grades.

#### -W

-w allows you to rewrite the FPGA design file after XDelay has retimed all nets in the design.

#### -X

-x allows you to generate the timing report in the long report format.

## **Features and Capabilities**

This section describes some important features of XDelay.

## TimeGroups

TimeGroups are groups of design elements, flip–flops, CLB RAM elements, IOBs, pins, or other TimeGroups. TimeGroups are used in conjunction with timing specification limits in support of XACT– Performance analysis.

You can use the XDelay -FailedSpec option to limit the timing report to just those paths that failed to meet the timing specifications. A simple example of the report format is shown below:

```

TimeSpec 'slow_clock' summary:

From TimeGroup 'slow_counter'

To TimeGroup 'blinkenlight'

TimeSpec limit is : 50.ns (Spec speed = 20.0 MHZ) Worst

path delay is : 26.2ns (Real speed = 38.1 MHZ)

TimSpec passes by : 23.8ns

List of delay paths:

There are no paths that fail the TimeSpec.

```

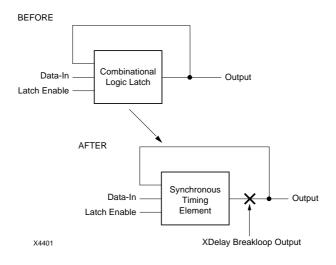

## **Breakloop Option for Combinatorial Logic**

You can use the Breakloop option for combinatorial logic, which can help XDelay generate meaningful delay information. This option forces XDelay to treat non–synchronous nets as synchronous. Breakloops mark combinatorial latches as a registered element in the design. XDelay considers only one feedback loop through the function generator in the time delay estimate. You remove the Breakloop using the -NoBreakloop option.

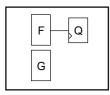

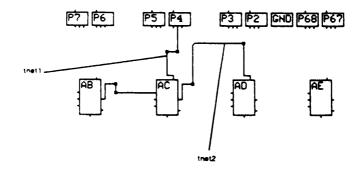

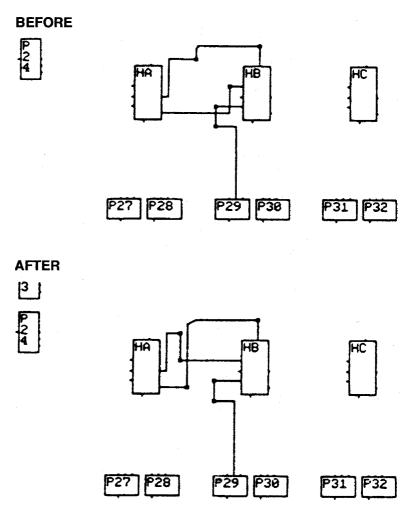

Figure 1-9 shows a simple circuit and how applying a Breakloop forces XDelay to trace the path. XDelay traces the path starting from the source of the Breakloop Net. The path stops when the Breakloop net is reached. With this option, paths do not travel through the Breakloop source as would normally happen for a combinatorial logic function.

Figure 1-9 -Breakloop Example

## **Path Delay Searches**

You can designate start and end points to narrowly focus the path delay search. XDelay has options that limit where XDelay searches on a specified path.

The -From option allows you to specify the starting limit of the path delay search starting at the named pins, blocks, and/or nets. The wildcard "\*" starts searches from all outputs.

The -To option allows you to specify the ending limit of the path delay search ending at the named pins, blocks, and/or nets. The "\*" ends searches at all inputs.

You can use the SourceClock and the DestClock options to limit the origins and destinations of delay path searches. These options work similar to the -From and -To options, except that XDelay selects objects by clock net instead of by pin, block, or net.

A clock net is any net that is used as a clock source for flip-flops or latches in a design. Most designs have only one clock net, usually from the global clock buffer. There are occasions where multiple clock nets are used, and you want a different set of data from the delay report about the paths clocked by the different clock nets. The ClockNet features provide some control over this type of search, and should make extracting useful delay information from XDelay easier.

## **Timing Margins**

The Margins commands allow you to specify external delays for paths entering or exiting the chip (PadToSetup and ClockToPad paths). Use these commands to provide XDelay with information about the external system. For example, if a signal enters the chip through an input, it might take 30 ns externally to get to that input. You could set the Margin to 30 ns on that pad so that XDelay includes the external margin in the path delay.

Briefly the Margins commands are:

- SetMargins sets additional external pad timing margins to PadToSetup or ClockToPad paths

- QueryMargins shows a list of all currently defined timing margins

- ClearMargins clears all currently defined margins

- Readmargins reads defined margins from an external file

For more details about these commands, refer to the Graphical Interface section.

## **Environment Variables**

If you are an experienced user of the XDelay program, you can customize your environment to control the XDelay output.

The environment variable XDELAY\_PRECISION controls how many digits of precision the XDelay output has. If this environment variable is not used, XDelay uses a single digit of precision.

**Note:** If you change the value of XDELAY\_PRECISION, Xilinx does not guarantee accuracy. This variable should only be used to verify floating–point rounding issues.

• To set this variable on Unix workstations, type:

#### setenv XDELAY\_PRECISION n

where *n* is an integer.

• To set this variable on PCs, type:

```

SET XDELAY_PRECISION n

```

where *n* is an integer.

The environment variable XDELAY\_MAX\_PATHS limits the number of paths XDelay traces before generating a report. If you reach this limit, you should try focusing the path search to keep XDelay from running out of memory-storing paths.

• To set this variable on Unix workstations, type:

```

setenv XDELAY_MAX_PATHS n

```

where n is the maximum number of paths XDelay should trace.

• To set this variable on PCs, type:

```

SET XDELAY_MAX_PATHS n

```

where n is the maximum number of paths XDelay should trace.

# **Template File Format**

## The .xtm File Format

A .xtm file may contain a sequence of the following commands.

- XDelay

- XDelay-TimeSpec

- Flagblk

- Speedsetmargins

- Report

The XDelay and XDelay-Timespec commands are used to record the various path filtering and reporting options for XDelay. For more information on these commands, refer to their individual entries in the "XDE" or "XDelay" chapters.

# **Chapter 2**

# The LCA2XNF Program

This program is compatible with the following families.

- XC2000

- XC2000L

- XC3000

- XC3000A

- XC3000L

- XC3100

- XC3100A

- XC4000

- XC4000A

- XC4000H

- XC5200

The LCA2XNF program converts an LCA file to an XNF file, which you can use for functional or timing simulation. If the LCA input file is placed and routed, the resulting XNF file contains all worst–case block and net delays for use in timing simulation. You can use the XNF file created by the LCA2XNF program to generate a simulation file for one or more of the Xilinx–supported third–party simulation products. You can also use the output file as a guide for logic partitioning with APR.

# **Syntax**

The following syntax creates an XNF file from your LCA file.

lca2xnf [options] input[.lca][output[.xnf]]

**Warning:** You should always specify a different output file name so that the original (unplaced, unrouted) XNF file is not overwritten.

# Files

LCA2XNF requires an LCA file as input and generates an XNF file and an SPC file (optionally).

## **Input Files**

#### input.lca

This is the LCA design input file created by APR, PPR, or the XACT Design Editor (XDE). The LCA input file can be completely routed, partially routed, or unrouted. The LCA extension is optional.

## **Output Files**