# DEVELOPMENT SYSTEM USER GUIDE

TABLE OF CONTENTS

INDEX

GO TO OTHER BOOKS

0401411

# Contents

#### Chapter 1 Introduction

| Xilinx FPGA Logic Devices                    |      |

|----------------------------------------------|------|

| Advantages of Xilinx FPGAs                   | 1-1  |

| Xilinx FPGA Families                         | 1-2  |

| FPGA Architecture                            |      |

| XC5200 CLB Structure                         | 1-3  |

| XC4000/XC4000A/XC4000H CLB Structure         | 1-4  |

| XC3000 CLB Structure                         | 1-6  |

| XC2000 CLB Structure                         | 1-6  |

| XC5200 IOBs                                  | 1-7  |

| XC4000/XC4000A IOBs                          |      |

| XC3000/XC3000A/XC3000L/XC3100/XC3100A IOBs   | 1-10 |

| XC2000/XC2000L IOBs                          | 1-11 |

| Global Resources                             | 1-12 |

| Routing Resources                            | 1-13 |

| Design Flow Overview                         |      |

| XACTstep Development System Documentation    |      |

| Development System User Guide                | 1-20 |

| Libraries Guide                              | 1-20 |

| Libraries Supplement Guide                   |      |

| X-BLOX Reference/User Guide                  |      |

| Xilinx ABEL User Guide                       | 1-20 |

| Development System Reference Guide, Volume 1 | 1-21 |

| Development System Reference Guide, Volume 2 | 1-21 |

| Development System Reference Guide, Volume 3 | 1-21 |

| Hardware & Peripherals User Guide            | 1-21 |

| CAE Interface User Guides                    | 1-21 |

#### Chapter 2 Design Entry

| 2-1 |

|-----|

| 2-1 |

| 2-1 |

| 2-2 |

| 2-2 |

|     |

|           | X-BLOX                                  | 2-2 |

|-----------|-----------------------------------------|-----|

|           | Text-Based Entry                        | 2-3 |

|           | Xilinx ABEL                             |     |

|           | XSI (Xilinx Synopsys Interface)         |     |

|           | Hierarchical Design                     |     |

|           | Hierarchical Names                      |     |

|           | Controlling Implementation              |     |

|           | Mapping                                 |     |

|           | Block Placement                         |     |

|           | Timing Specifications                   |     |

|           | Performing Functional Simulation        |     |

| Chapter 3 | Design Implementation                   |     |

|           | XNF Translation                         | 3-3 |

|           | Optimization                            |     |

|           | Binary Encoding                         |     |

|           | One-Hot Encoding                        |     |

|           | Standard Encoding                       |     |

|           | Merging                                 |     |

|           | Mapping                                 |     |

|           | Placement                               |     |

|           | Routing                                 |     |

|           | Generating a Bitstream                  |     |

|           | XACT Design Editor (XDE)                |     |

|           | Design Size and Performance             |     |

|           | Estimating Design Size                  |     |

|           | Synchronous Design                      |     |

|           | Global Clock Distribution               |     |

|           | Other Synchronous Design Considerations |     |

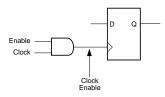

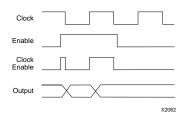

|           | Data Feedback and Clock Enable          |     |

|           | Counters                                |     |

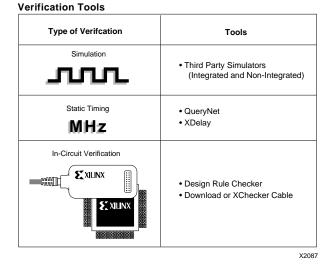

| Chapter 4 | Design Verification                     |     |

|           | Verification Design Flow                | 4-1 |

|           | Simulation                              |     |

|           | Functional Simulation                   | -   |

|           | Timing Simulation                       |     |

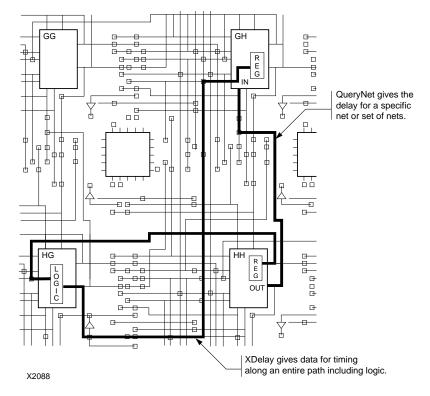

|           | Static Timing Analysis                  |     |

|           | XDelay                                  |     |

|           | QueryNet                                |     |

|           | In-Circuit Verification                 |     |

|           |                                         |     |

|           | Design Rule Checker<br>Xilinx Download and XChecker Cables<br>Probe                                                                                                                                                                                                         | 4-9                      |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Chapter 5 | FPGA Design Implementation Flows                                                                                                                                                                                                                                            |                          |

|           | <ul> <li>XC2000, XC2000L, XC3000, and XC3100 Families</li> <li>Logic Reduction and Partitioning</li> <li>Automatic Place and Route (APR)</li> <li>APRLoop</li> <li>XC3000A, XC3000L, and XC3100A Families</li> <li>XC4000, XC4000A, XC4000H, and XC5200 Families</li> </ul> | 5-2<br>5-3<br>5-3<br>5-3 |

| Chapter 6 | Configuration, Length Count, and Debugging                                                                                                                                                                                                                                  |                          |

|           | Configuration                                                                                                                                                                                                                                                               | 6-1                      |

|           | Data Generation                                                                                                                                                                                                                                                             | 6-1                      |

|           | MakeBits                                                                                                                                                                                                                                                                    | 6-2                      |

|           | MakePROM                                                                                                                                                                                                                                                                    | 6-3                      |

|           | Data Format                                                                                                                                                                                                                                                                 | 6-5                      |

|           | Creating Bitstreams                                                                                                                                                                                                                                                         | 6-5                      |

|           | Single Device Streams                                                                                                                                                                                                                                                       |                          |

|           | Daisy Chain Streams                                                                                                                                                                                                                                                         |                          |

|           | PROMs                                                                                                                                                                                                                                                                       |                          |

|           | Modes                                                                                                                                                                                                                                                                       |                          |

|           | Master versus Non-Master                                                                                                                                                                                                                                                    |                          |

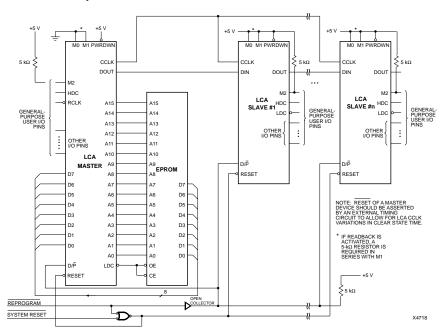

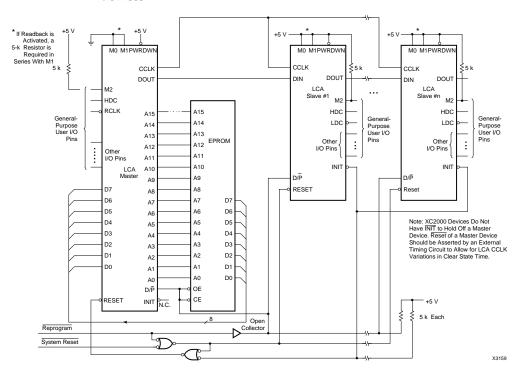

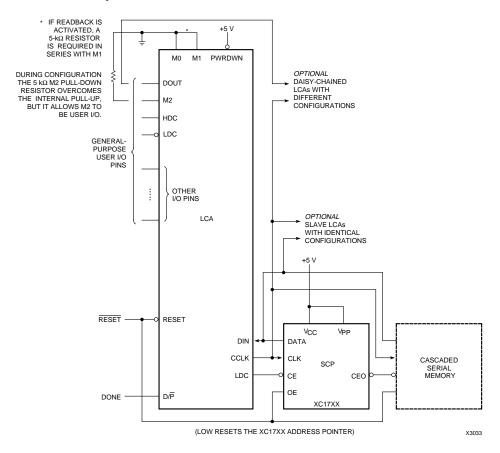

|           | XC2000/XC3000 Modes                                                                                                                                                                                                                                                         |                          |

|           | XC4000 and XC5200 Modes                                                                                                                                                                                                                                                     |                          |

|           | Loading and Framing Configuration Data                                                                                                                                                                                                                                      |                          |

|           | Serial Loading of Daisy Chains                                                                                                                                                                                                                                              |                          |

|           | Concurrent Loading of Multiple Devices<br>Loading Alternate Configurations                                                                                                                                                                                                  |                          |

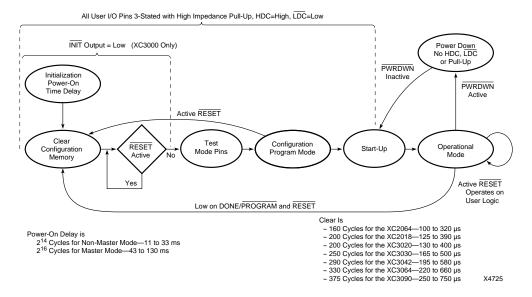

|           | States for XC2000/XC3000 Devices                                                                                                                                                                                                                                            |                          |

|           | Power-up and Initialization                                                                                                                                                                                                                                                 |                          |

|           | Clear                                                                                                                                                                                                                                                                       |                          |

|           | Configuration                                                                                                                                                                                                                                                               |                          |

|           | Start-up                                                                                                                                                                                                                                                                    |                          |

|           | Reprogramming                                                                                                                                                                                                                                                               |                          |

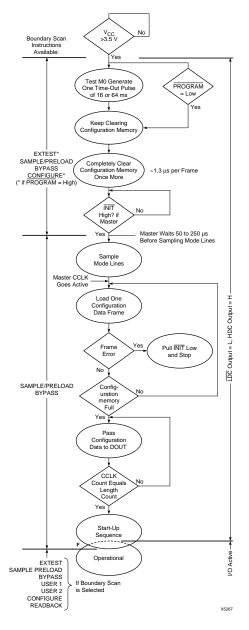

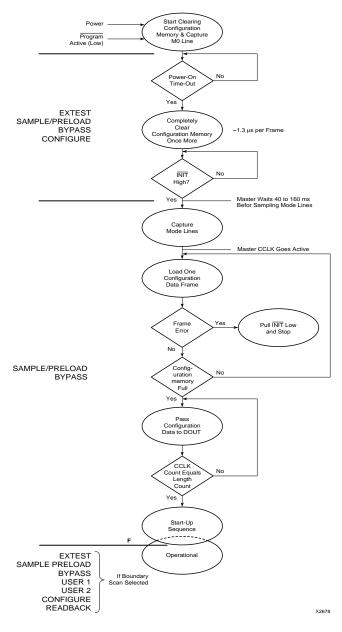

|           | States for XC4000 and XC5200 Devices                                                                                                                                                                                                                                        |                          |

|           | Power-up and Memory Clear                                                                                                                                                                                                                                                   |                          |

|           | Initialization                                                                                                                                                                                                                                                              |                          |

|           | Configuration                                                                                                                                                                                                                                                               |                          |

|           | Start-up                                                                                                                                                                                                                                                                    | 6-38                     |

|           |                                                                                                                                                                                                                                                                             |                          |

|           | Reprogramming                                                                                                                                                                                                                                                                                                                           | 6-42                                                                                      |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

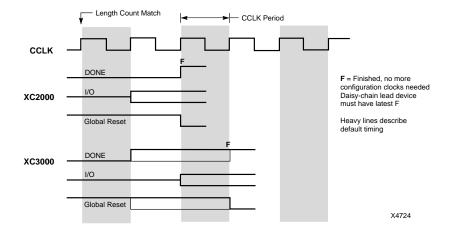

|           | Length Count                                                                                                                                                                                                                                                                                                                            | 6-42                                                                                      |

|           | DONE Alignment                                                                                                                                                                                                                                                                                                                          | 6-44                                                                                      |

|           | Length Count Alignment                                                                                                                                                                                                                                                                                                                  | 6-47                                                                                      |

|           | Debugging Hints                                                                                                                                                                                                                                                                                                                         |                                                                                           |

|           | General Debugging Hints                                                                                                                                                                                                                                                                                                                 | 6-48                                                                                      |

|           | All Families                                                                                                                                                                                                                                                                                                                            |                                                                                           |

|           | XC2000 and XC3000                                                                                                                                                                                                                                                                                                                       | 6-50                                                                                      |

|           | XC4000 and XC5200                                                                                                                                                                                                                                                                                                                       | 6-51                                                                                      |

|           | Master Parallel Up and Down Modes                                                                                                                                                                                                                                                                                                       | 6-52                                                                                      |

|           | Debugging Failed Configuration                                                                                                                                                                                                                                                                                                          | 6-52                                                                                      |

|           | Debugging Incorrect Configuration                                                                                                                                                                                                                                                                                                       | 6-52                                                                                      |

|           | Master Serial Mode                                                                                                                                                                                                                                                                                                                      | 6-53                                                                                      |

|           | Debugging Failed Configuration                                                                                                                                                                                                                                                                                                          | 6-53                                                                                      |

|           | Debugging Incorrect Configuration                                                                                                                                                                                                                                                                                                       | 6-54                                                                                      |

|           | Peripheral Mode                                                                                                                                                                                                                                                                                                                         | 6-55                                                                                      |

|           | Debugging Failed Configuration                                                                                                                                                                                                                                                                                                          | 6-55                                                                                      |

|           | Debugging Incorrect Configuration                                                                                                                                                                                                                                                                                                       | 6-56                                                                                      |

|           | Slave Mode                                                                                                                                                                                                                                                                                                                              | 6-57                                                                                      |

|           | Debugging Failed Configuration                                                                                                                                                                                                                                                                                                          | 6-57                                                                                      |

|           | Debugging Incorrect Configuration                                                                                                                                                                                                                                                                                                       |                                                                                           |

|           | Daisy Chain Debugging Hints                                                                                                                                                                                                                                                                                                             | 6-58                                                                                      |

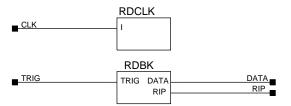

| Chapter 7 | The XC4000 and XC5200 Readback Capability                                                                                                                                                                                                                                                                                               |                                                                                           |

|           | When is Readback Necessary?                                                                                                                                                                                                                                                                                                             | 7-1                                                                                       |

|           | Readback Features                                                                                                                                                                                                                                                                                                                       |                                                                                           |

|           |                                                                                                                                                                                                                                                                                                                                         |                                                                                           |

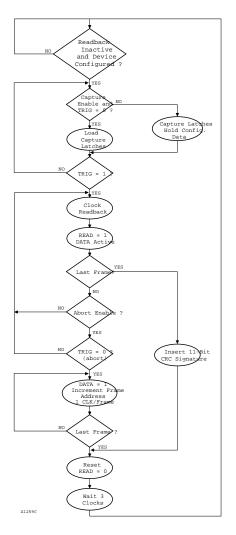

|           | Performing a Readback                                                                                                                                                                                                                                                                                                                   | 7-6                                                                                       |

|           | Performing a Readback<br>Readback State Diagram                                                                                                                                                                                                                                                                                         |                                                                                           |

|           | Readback State Diagram                                                                                                                                                                                                                                                                                                                  | 7-6                                                                                       |

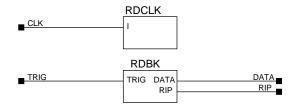

|           | Readback State Diagram<br>READBACK Primitive                                                                                                                                                                                                                                                                                            | 7-6<br>7-7                                                                                |

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization                                                                                                                                                                                                                                                                 | 7-6<br>7-7<br>7-9                                                                         |

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization<br>Using the Readback Primitive on the Schematic                                                                                                                                                                                                                | 7-6<br>7-7<br>7-9<br>7-9                                                                  |

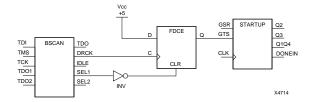

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization<br>Using the Readback Primitive on the Schematic<br>Performing a Readback during a Boundary Scan                                                                                                                                                                | 7-6<br>7-7<br>7-9<br>7-9<br>7-10                                                          |

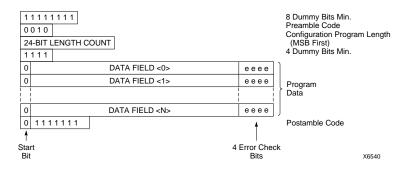

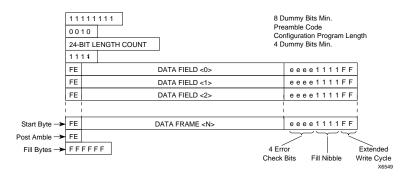

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization<br>Using the Readback Primitive on the Schematic<br>Performing a Readback during a Boundary Scan<br>Configuration and Readback Bitstreams                                                                                                                       | 7-6<br>7-7<br>7-9<br>7-9<br>7-10<br>7-10                                                  |

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization<br>Using the Readback Primitive on the Schematic<br>Performing a Readback during a Boundary Scan                                                                                                                                                                | 7-6<br>7-7<br>7-9<br>7-9<br>7-10<br>7-10<br>7-10                                          |

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization<br>Using the Readback Primitive on the Schematic<br>Performing a Readback during a Boundary Scan<br>Configuration and Readback Bitstreams<br>The Configuration Bitstream                                                                                        | 7-6<br>7-7<br>7-9<br>7-10<br>7-10<br>7-10<br>7-11                                         |

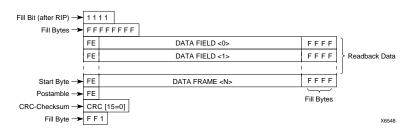

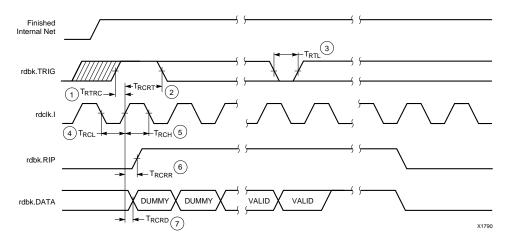

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization<br>Using the Readback Primitive on the Schematic<br>Performing a Readback during a Boundary Scan<br>Configuration and Readback Bitstreams<br>The Configuration Bitstream<br>The Readback Bitstream                                                              | 7-6<br>7-7<br>7-9<br>7-10<br>7-10<br>7-10<br>7-11<br>7-13                                 |

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization<br>Using the Readback Primitive on the Schematic<br>Performing a Readback during a Boundary Scan<br>Configuration and Readback Bitstreams<br>The Configuration Bitstream<br>The Readback Bitstream<br>Software Support for Readback                             | 7-6<br>7-7<br>7-9<br>7-10<br>7-10<br>7-10<br>7-11<br>7-13<br>7-13                         |

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization<br>Using the Readback Primitive on the Schematic<br>Performing a Readback during a Boundary Scan<br>Configuration and Readback Bitstreams<br>The Configuration Bitstream<br>The Readback Bitstream<br>Software Support for Readback<br>ReadCapture              | 7-6<br>7-7<br>7-9<br>7-10<br>7-10<br>7-10<br>7-10<br>7-11<br>7-13<br>7-13<br>7-13         |

|           | Readback State Diagram<br>READBACK Primitive<br>Readback Initialization<br>Using the Readback Primitive on the Schematic<br>Performing a Readback during a Boundary Scan<br>Configuration and Readback Bitstreams<br>The Configuration Bitstream<br>The Readback Bitstream<br>Software Support for Readback<br>ReadCapture<br>ReadAbort | 7-6<br>7-7<br>7-9<br>7-10<br>7-10<br>7-10<br>7-10<br>7-11<br>7-13<br>7-13<br>7-13<br>7-14 |

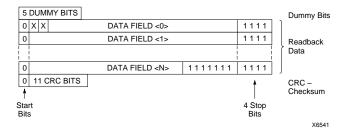

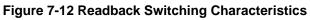

|           | Cyclic Redundancy Check<br>What is CRC?<br>CRC During FPGA Configuration<br>CRC During Readback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-17<br>7-17                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

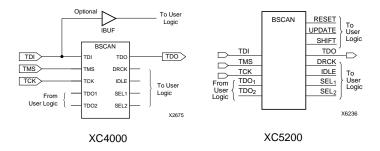

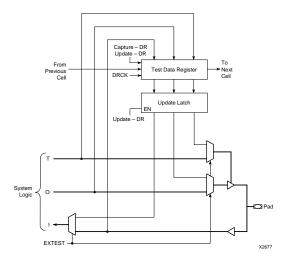

| Chapter 8 | Boundary Scan in XC4000 and XC5200 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                        |

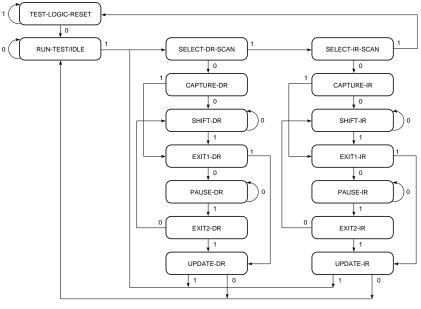

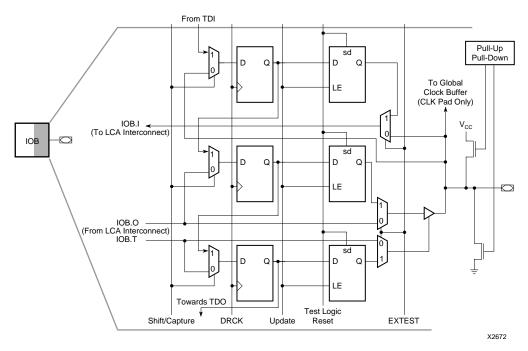

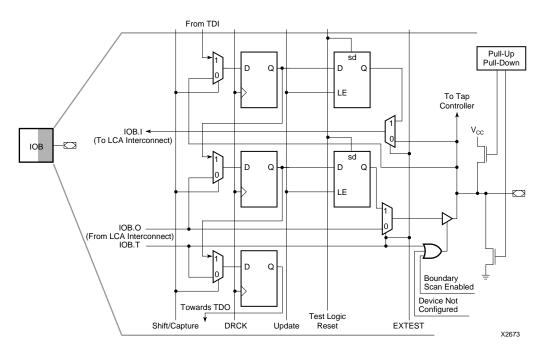

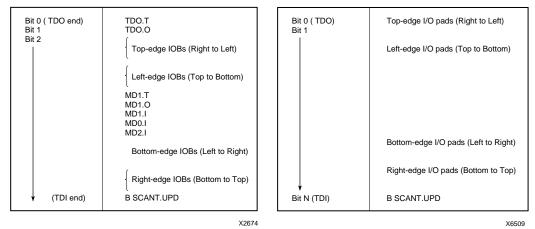

| Chapter 9 | Boundary-Scan Features         Deviations from the IEEE Standard         Boundary-Scan Hardware Description         Test Access Port         TAP Controller         Instruction Register         The Boundary-Scan Data Register         The Boundary-Scan Data Register         User Registers         Using Boundary Scan         Boundary Scan Availability         Post-Configuration Boundary-Scan Operation         XC4000 and XC5200 Boundary-Scan Instructions         Extest         Sample/Preload         Bypass         User1 and User2         Configure         Readback         Instruction Availability         Pre-Configuration         Inter-Configuration         Inter-Configuration         Instruction Load Failure         Boundary Scan Description Language Files         Boundary Scan Bibliography | 8-2<br>8-3<br>8-4<br>8-4<br>8-7<br>8-8<br>8-11<br>8-12<br>8-14<br>8-14<br>8-14<br>8-17<br>8-18<br>8-20<br>8-20<br>8-20<br>8-20<br>8-20<br>8-20<br>8-20<br>8-22<br>8-23<br>8-24<br>8-24<br>8-24<br>8-24 |

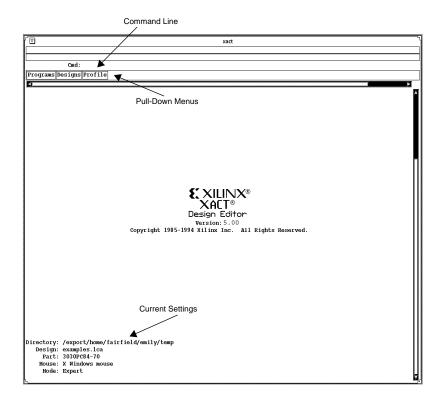

| Shapter 3 | Getting Started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9-2                                                                                                                                                                                                    |

|           | Setting the Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                        |

|           | Setting the Directory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                        |

|           | PCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                        |

|           | All Other Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9-4                                                                                                                                                                                                    |

|           | Choosing the Design File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9-4                                                                                                                                                                                                    |

|           | Loading the Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9-5                                                                                                                                                                                                    |

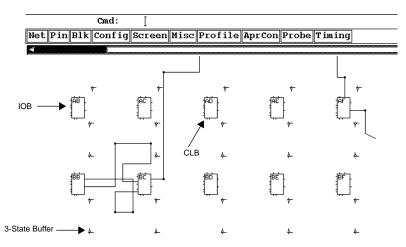

| Viewing the FPGA                        | 9-5  |

|-----------------------------------------|------|

| Definitions                             | 9-6  |

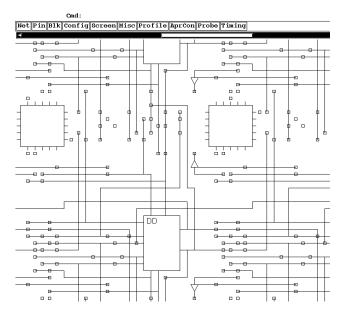

| The EditLCA Screen                      | 9-6  |

| Setting the Profile                     | 9-7  |

| Setting the Mouse Buttons               |      |

| Defining the Function Keys              |      |

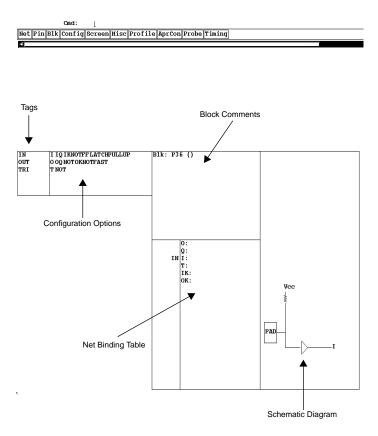

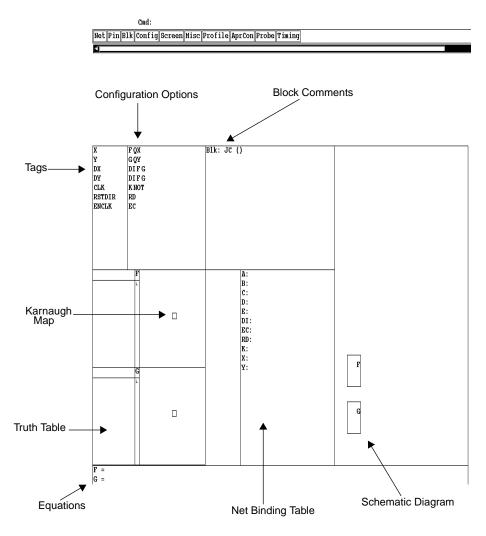

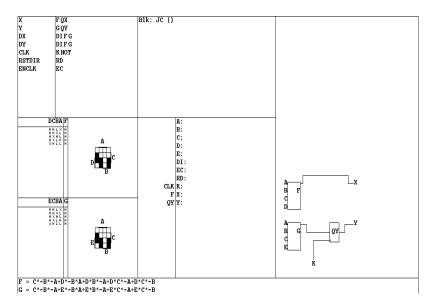

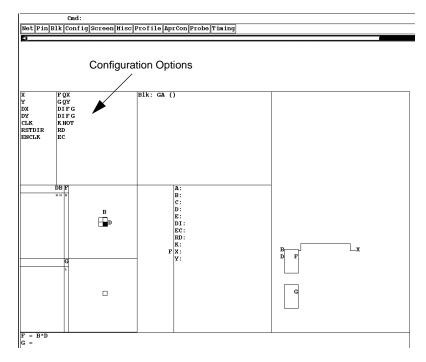

| Using the EditBlk Display               | 9-10 |

| High-level Editing                      |      |

| SwapSig                                 | 9-16 |

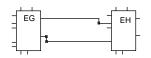

| SwapBlk                                 | 9-21 |

| Low-level Editing                       |      |

| Screen Options                          | 9-26 |

| Switch Matrices                         | 9-27 |

| Programmable Interconnection Points     | 9-28 |

| Routing Resources                       |      |

| Direct Interconnect                     | 9-30 |

| General Purpose Interconnect            | 9-32 |

| Longlines                               | 9-32 |

| Manual Routing                          | 9-34 |

| Disable Autoroute Option                | 9-35 |

| Route Nets Manually                     | 9-35 |

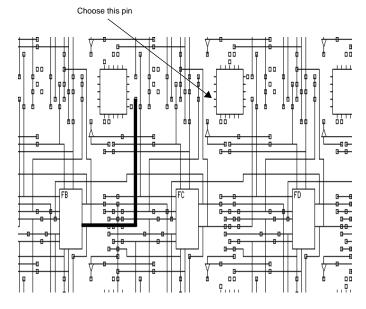

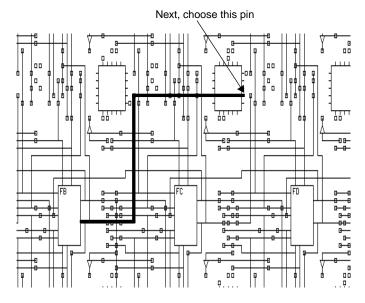

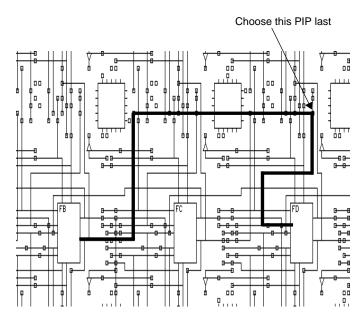

| Connect Source and Load Pins            | 9-36 |

| Route Through a Switch Matrix           | 9-36 |

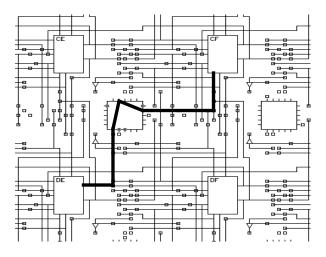

| Routing Through a Switch Matrix         | 9-40 |

| Routing Nets Using a Longline           | 9-42 |

| Swap the Blocks                         | 9-42 |

| Swap the Pins                           | 9-43 |

| Route the Net                           | 9-43 |

| Perform a QueryNet                      | 9-44 |

| Commands that Perform Similar Functions |      |

| Unroute and UnroutePin                  | 9-45 |

| Route and Routepin                      |      |

| Route, EditNet, and RoutePoint          |      |

| Hilight and ColorNet                    |      |

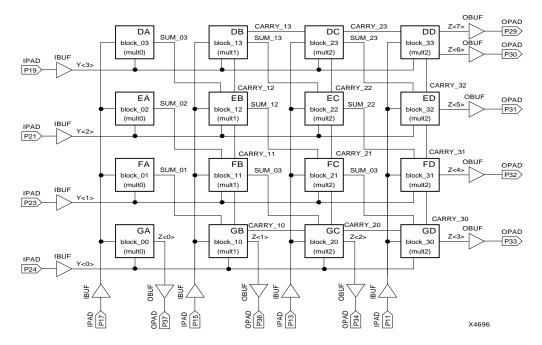

| Building a Four-Bit Multiplier          |      |

| Creating a New Design                   |      |

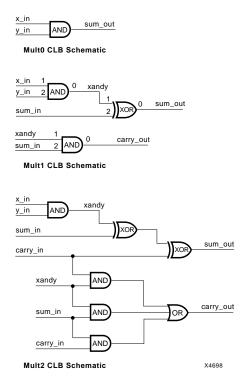

| Creating the mult0 CLB                  |      |

| Creating the mult1 CLB                  |      |

| Creating the mult2 CLB                  |      |

| Configuring an IOB as an Input Pin      |      |

| Configuring an IOB as an Output Pin     | 9-57 |

| Giving Blocks Logical Names<br>Adding Nets to the Design<br>Checking the Nets in Your Design<br>Routing the Nets<br>Using the XDelay Command<br>Improving the Routing<br>Downloading a Bitstream<br>Quitting XDE | 9-60<br>9-62<br>9-64<br>9-64<br>9-65<br>9-67 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Index                                                                                                                                                                                                            | i                                            |

#### **Trademark Information**

# **Chapter 1**

## Introduction

This manual describes the XACT*step* Development System, which enables you to enter, implement, and verify your designs in a matter of hours. Before actually starting with the design process, you should read the following introduction to the Xilinx Field Programmable Gate Array (FPGA) devices.

For information on EPLDs, refer to the *XEPLD Design Guide*, *XEPLD Reference Guide* and *XEPLD Schematic Design Guide*.

This chapter introduces Xilinx FPGA logic devices, provides an overview of the FPGA design process, and introduces the XACT*step* Development System documentation set.

## Xilinx FPGA Logic Devices

To integrate logic into smaller spaces, Xilinx has developed a type of FPGA called a Logic Cell Array (LCA). Several families can accommodate as many as 9,000 gates on a single device. The XC4000 family allows more than 20,000 gates on a single device. For more information about a specific Xilinx device, refer to *The Programmable Logic Data Book*.

#### **Advantages of Xilinx FPGAs**

The most significant advantage of using the Xilinx line of FPGA products is the ability to produce a prototype logic design on your desktop. You can create a logic design, implement it, and verify it in hours, while conventional gate array products can take months to develop and produce working silicon.

In addition, Xilinx logic products are in-circuit programmable, so even while an FPGA device is soldered to a board, you can reprogram the Xilinx part with a different FPGA design.

## Xilinx FPGA Families

Xilinx markets and supports many product lines — XC2000, XC2000L, XC3000, XC3000A, XC3000L, XC3100, XC3100A, XC4000, XC4000A, XC4000H, and XC5200. The primary difference between these products lies in the number of gates and the architectural features of the individual devices, as shown in Table 1-1.

| Product    | Logic Capacity<br>(Gate Equivalent) | Max.CLB<br>Count <sup>1</sup> | Max. IOB<br>Count |

|------------|-------------------------------------|-------------------------------|-------------------|

| XC2000/L   | 1,200 - 1,800                       | 100                           | 74                |

| XC3000/A/L | 1,300 - 9,000                       | 484                           | 176               |

| XC3100/A   | 1,300 - 9,000                       | 484                           | 176               |

| XC4000     | 2,000 - 20,000                      | 900                           | 240               |

| XC4000A    | 2,000 - 5,000                       | 196                           | 112               |

| XC4000H    | 2,000 - 5,000                       | 196                           | 192               |

| XC5200     | 2,000 - 15,000                      | 484                           | 244               |

#### Table 1-1 Maximum Logic Capacities

<sup>1</sup>Different architectures have different CLB structures, which affects logic implementation in a design.

## **FPGA** Architecture

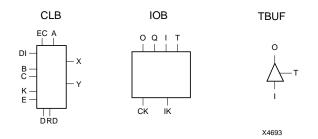

The FPGA architecture consists of three types of configurable elements — a perimeter of input/output blocks (IOBs), a core array of configurable logic blocks (CLBs), and resources for interconnection. The IOBs provide a programmable interface between the internal array of logic blocks (CLBs) and the device's external package pins. CLBs perform user-specified logic functions, and the interconnect resources carry signals among the blocks.

A configuration program stored in internal static memory cells determines the logic functions and the interconnect. The configuration data is loaded into the device during power-up or when you reprogram.

FPGA devices are customized by loading configuration data into internal memory cells (latches). The FPGA device can either actively

read its configuration data out of an external serial or byte-wide parallel PROM (master modes), or the configuration data can be written into the FPGA device (slave and peripheral modes).

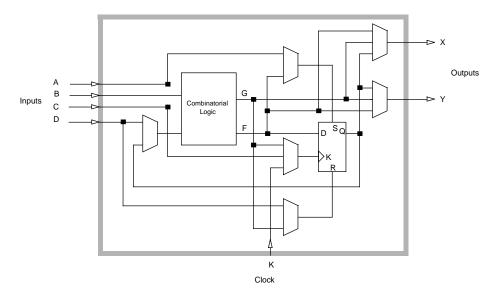

#### XC5200 CLB Structure

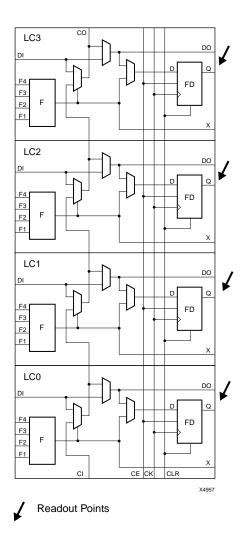

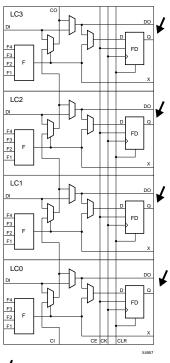

Each XC5200 CLB consists of four logic cells, the basic logic elements in each CLB. Each logic cell contains an independent 4-input function generator (F), a storage device (FD), and control logic. There are five independent inputs and three outputs to each logic cell.

The control logic provides direct access to the data input of the flipflop through the direct input pin (DI). The control logic also consists of high-speed carry logic for fast implementation of arithmetic and counting functions, which can also be used as a cascade chain allowing high-speed pattern decode and other wide-logic functions.

The storage device in each logic cell is configurable as either a D flipflop or a latch. The XC5200 CLB has 20 independent logical inputs, a clock, clock enable, and asynchronous clear. Each CLB also has 12 independent outputs that permit maximum utilization of the CLB resources.

Figure 1-1 shows the structure of the XC5200 CLB.

Figure 1-1 XC5200 CLB Structure

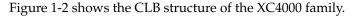

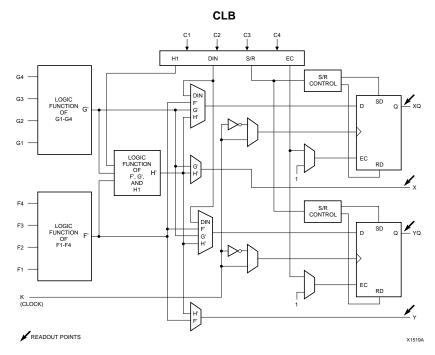

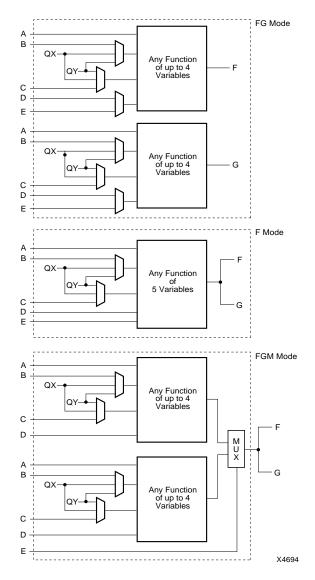

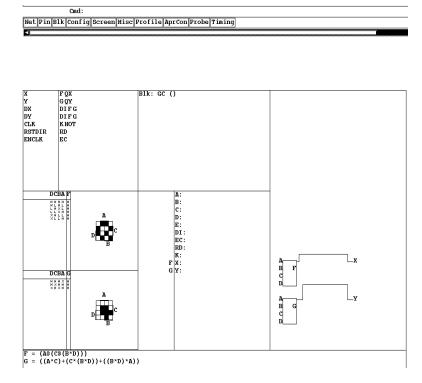

## XC4000/XC4000A/XC4000H CLB Structure

Each CLB includes two independent 4-input function generators (F and G) and two storage elements. A third function generator (H) can combine the outputs of F and G with a ninth input variable, thus

implementing some functions of up to nine variables. The function generators can also be configured as Read/Write memory or RAM.

The four control inputs, C1 through C4 each can generate any one of four logic signals used in the CLB. These control inputs can be used as direct inputs to the two flip-flops, the clock enable to the two flip-flops, and/or the asynchronous control (direct Set or direct Reset) of the two flip-flops.

Each XC4000 CLB also includes dedicated high-speed carry logic that can generate the arithmetic carry output for incoming operands, and can pass this extra output to the adjacent upper or lower CLB function generator. This connection is independent of normal routing resources. This feature improves the performance of the arithmetic and counting functions in the XC4000.

Figure 1-2 XC4000 CLB Structure

## XC3000 CLB Structure

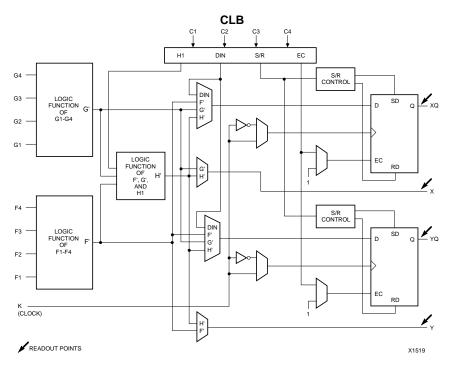

The CLBs in the XC3000/XC3000A/XC3000L/XC3100/XC3100A devices have two function generators, a combinatorial logic section, and an internal control section.

Each XC3000 CLB includes five logic inputs, a common clock input, an asynchronous direct reset input, a clock enable, and two outputs. A data-in input is also provided for direct input to the flip-flops within the CLB.

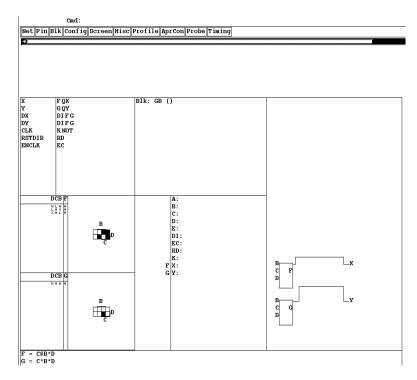

Figure 1-3 illustrates an XC3000 CLB structure.

Figure 1-3 XC3000 CLB Structure

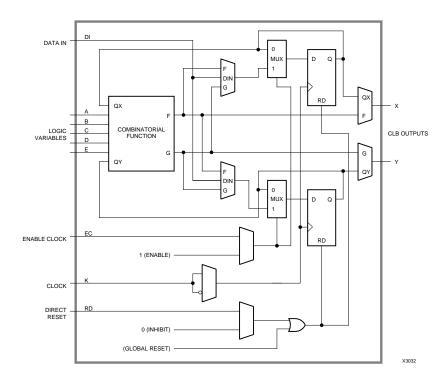

#### XC2000 CLB Structure

The CLBs in the XC2000/XC2000L devices have two function generators, a combinatorial logic section, a storage element, and an

Xilinx Development System

internal routing and control section. In addition, each CLB has four general-purpose inputs, a clock input, and two outputs. Figure 1-4 illustrates an XC2000 CLB structure.

Figure 1-4 XC2000 CLB Structure

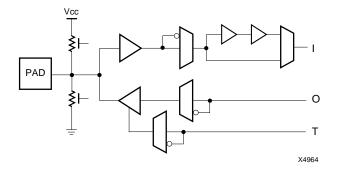

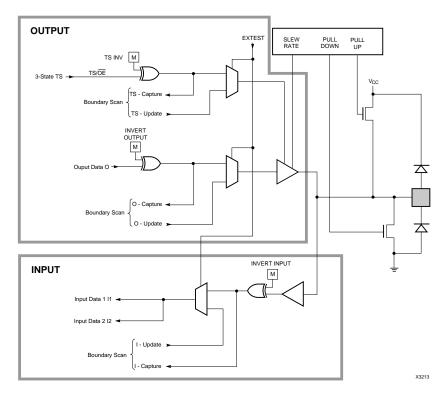

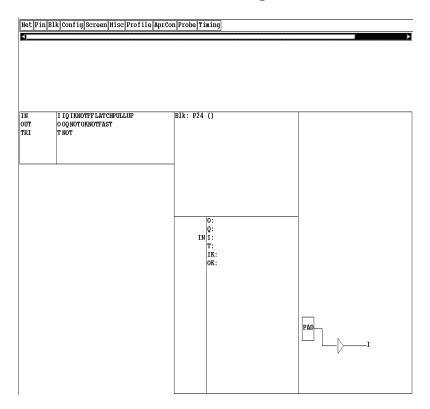

#### XC5200 IOBs

The XC5200 IOB includes a direct input and a tristatable output. Configuration options on the IOB include input inversion, output inversion, tristate control inversion, a controlled slew-rate output, and a programmable delay to eliminate the input hold time when the input buffer directly sources a flip-flop. A pull-up or pull-down resistor can be activated for either inputs or outputs.

Figure 1-5 shows the structure of the XC5200 Input/Output Block.

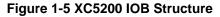

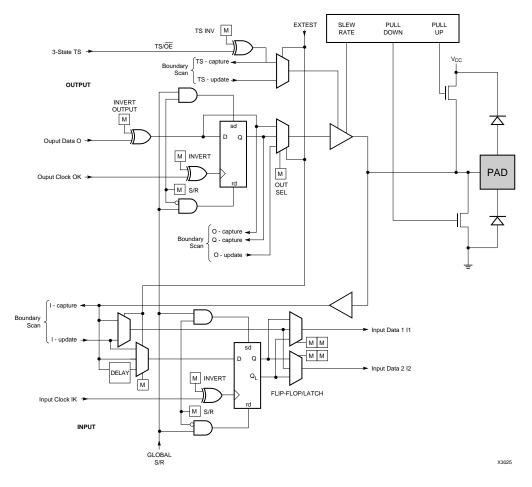

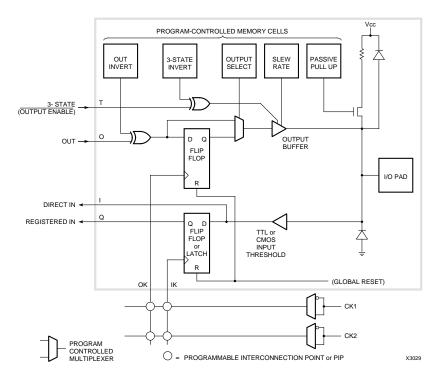

#### XC4000/XC4000A IOBs

The XC4000 IOB input includes both registered and direct input paths, and each output provides a tristate output buffer that can be driven by a registered or direct output signal. Configuration options on the IOB output include an inversion, a controlled slew-rate output, a tristate control inversion, a clock inversion, and programmable flipflop initialization states. Configuration options on the inputs include clock inversion and a programmable delay to eliminate input hold time.

A pull-up or pull-down resistor can be activated for either inputs or outputs. Input registers can be flip-flops or latches with programmable initialization states.

#### An XC4000 IOB structure is shown in Figure 1-6.

Figure 1-6 XC4000/XC4000A IOB Structure

The XC4000H family is identical to the XC4000 family, except for the input/output structure. The XC4000H family almost doubles the number of input/output pins. XC4000H devices, however, contain no input or output flips, as illustrated Figure 1-7.

Figure 1-7 XC4000H IOB Structure

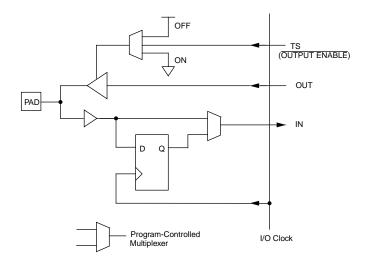

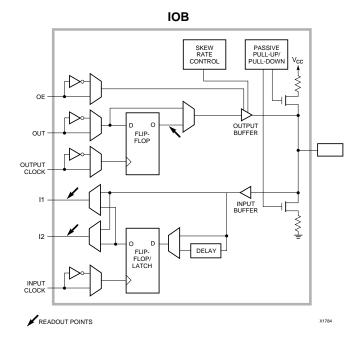

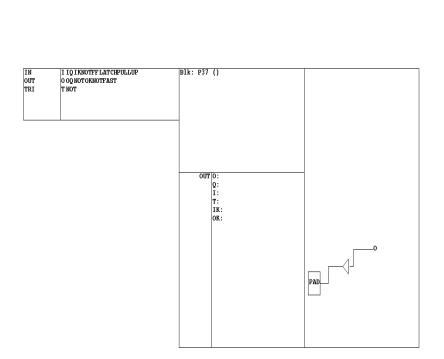

#### XC3000/XC3000A/XC3000L/XC3100/XC3100A IOBs

The XC3000 IOB input includes both registered and direct input paths, and each output provides a register, optional inversion, a controlled slew-rate output, and optional tristate control inversion.

IOB clocks for an entire edge can be inverted. Configuration options on the inputs include a pull-up resistor. An XC3000 IOB structure is shown in Figure 1-8.

Figure 1-8 XC3000 IOB Structure

#### XC2000/XC2000L IOBs

The XC2000 IOBs include a direct or registered input and a tristate output. Figure 1-9 illustrates an XC2000 IOB structure.

#### Figure 1-9 XC2000 IOB Structure

#### **Global Resources**

Each Xilinx FPGA device includes global resources, which distribute clock signals throughout the device with very low skew.

GCLK and ACLK primitives

The GCLK and ACLK primitives correspond to the global clock buffer and the alternate clock buffer in XC2000/L, XC3000/A/L, and XC3100/A devices. You can only use one GCLK and one ACLK in a single FPGA design.

• BUFGP and BUFGS primitives

BUFGP and BUFGS correspond to the primary and secondary global buffers, which distribute high-fanout clock or control signals throughout XC4000/A/H devices. You can use up to four BUFGP and BUFGS primitives in an XC4000/A/H design.

• BUFG

The BUFG primitive corresponds to the four global clock buffers that distribute high-fanout clock signals throughout the XC5200 device.

#### **Routing Resources**

The CLBs and IOBs, as mentioned in the preceding sections, are interconnected using the routing resources provided on the device. The Xilinx mapping, placement, and routing software chooses the best resource to use for a particular signal type. The different types of FPGA routing resources are described in this section. For more detailed information about routing resources for each Xilinx FPGA, refer to *The Programmable Logic Data Book*.

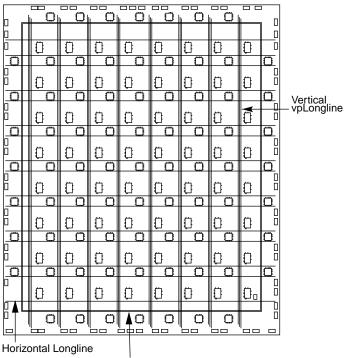

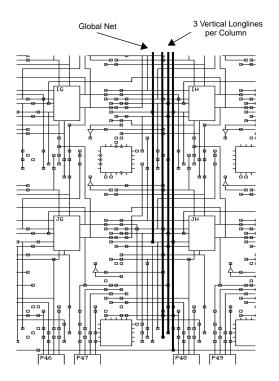

• Horizontal and Vertical longlines

In all devices other than XC2000/L, you can use horizontal longlines driven by tristate buffers for bidirectional data busses. Other longlines (vertical and non-TBUF-driven horizontal) are useful for high-fanout nets. Figure 1-10 illustrates horizontal and vertical longlines on an XC3000 device.

Four Outer Longlines are Connectable Half-Length Lines

#### Figure 1-10 Horizontal and Vertical Longlines (XC3000)

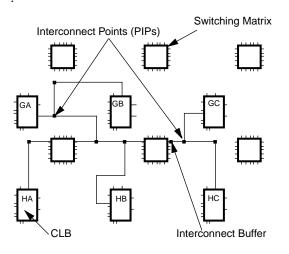

• Direct interconnect (XC2000, XC3000, and XC5200 only)

Direct interconnect are direct paths used to connect adjacent CLBs or to connect adjacent CLBs and IOBs. Each CLB output can be connected to the input of a CLB or IOB adjacent to it through a direct interconnect segment.

These resources are best used for high-speed signals between adjacent blocks as illustrated by Figure 1-11.

#### Figure 1-11 Example of CLBs with Direct Interconnect (XC3000)

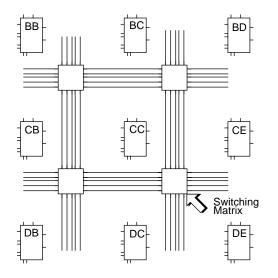

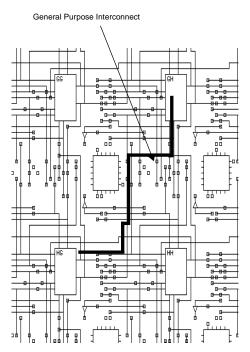

• General purpose interconnect

General purpose interconnect consists of an array of short adjacent metal segments oriented vertically and horizontally between the rows and columns of CLBs, as illustrated in Figure 1-12. Switch matrices connect the metal segments.

#### Figure 1-12 General Purpose Interconnects (GPIs)

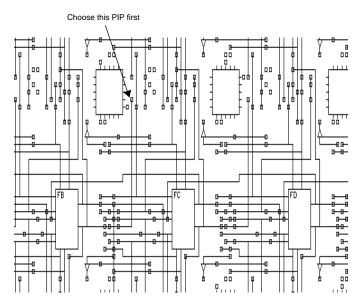

• Programmable interconnect points (PIPs)

PIPs are individual switches that enable the connection between intersecting routing segments, or from routing segments to CLB or IOB pins, as illustrated in Figure 1-13.

#### Figure 1-13 Programmable Interconnect Points (PIPs)

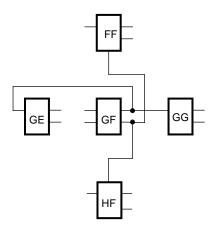

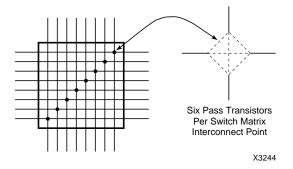

• Switch matrices

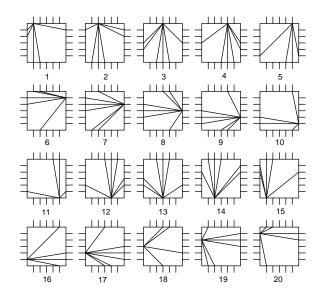

A matrix of switches is located at the intersections of the horizontal and vertical groups of general-purpose interconnect segments. These matrices are also referred to as magic boxes. Figure 1-14 shows the possible pin-to-pin connections for an XC3000 switching matrix.

Figure 1-14 Switching Matrix

#### **Design Flow Overview**

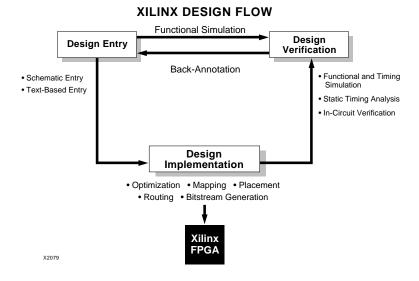

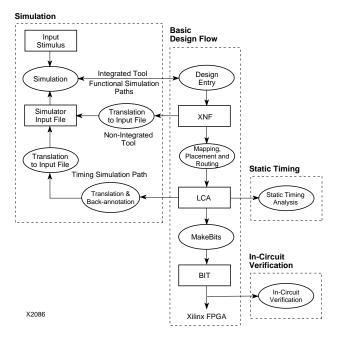

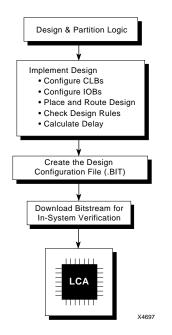

The FPGA design flow is a 3-step process that consists of the following stages.

- Design Entry In this stage of the design flow you create your design using a Xilinx-supported schematic editor or hardware description language (HDL).

- Design Implementation By partitioning, placing, and routing your design, you convert the design file created in the design entry stage into an LCA file format. Then you create a bitstream file from the LCA file and optionally program a PROM or EPROM for subsequent programming of your Xilinx device.

- Design Verification Using a simulator, the Xilinx XChecker™ cable, or the Xilinx Download cable, you ensure that your design meets your timing requirements and functions properly.

Overviews of design entry, design implementation, and design verification are discussed in the "Design Entry," "Design Implementation," and "Design Verification" chapters, respectively.

The full design flow is an iterative process of entering, implementing, and verifying your design until it is correct and complete. The XACT*step* Development System allows quick design iterations through the design flow cycle. Since FPGA devices permit unlimited reprogramming, you do not need to discard devices when debugging your design in-circuit. See the "Design Implementation Flow" chapter in this user guide for design flows for specific Xilinx devices.

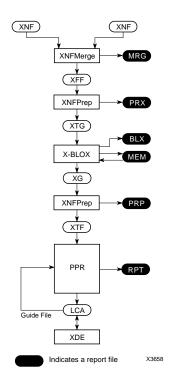

Figure 1-15 illustrates the Xilinx design flow.

#### Figure 1-15 Xilinx Design Flow

Table 1-2, defines the terms used in Figure 1-15.

| Term                    | Description                                                                                                                   |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Schematic entry         | Design entry using graphic symbols                                                                                            |

| Text-based entry        | Design entry using a design language                                                                                          |

| Optimization            | Converting device-independent or behavioral logic descriptions to a form that can be efficiently implemented in a Xilinx FPGA |

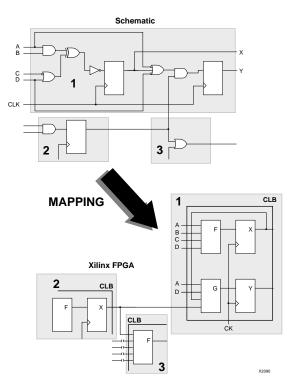

| Mapping                 | Dividing a design's logic into the resources of the Xilinx<br>FPGA                                                            |

| Placement               | Assigning design blocks created during mapping to specific locations in the FPGA                                              |

| Routing                 | Assigning the interconnect paths                                                                                              |

| Bitstream generation    | Converting a design into a bitstream that can be loaded into a Xilinx FPGA                                                    |

| Back-annotation         | Matching schematic and routed nets so that the same input<br>stimuli can be used for functional and timing simulation         |

| Simulation              | Software testing of the design logic and timing using input stimuli                                                           |

| Static timing analysis  | Analyzing the signal paths to ensure that the delays are acceptable                                                           |

| In-circuit verification | Testing of the design in a system after it is loaded into a Xilinx FPGA                                                       |

#### Table 1-2 Design Flow Terms

## XACT step Development System Documentation

The XACT*step* Development System documentation set consists of a series of books that help you use the XACT*step* Development System software in conjunction with your schematic entry tools. The documentation set includes the following manuals: *Development System User Guide, Libraries Guide, Libraries Supplement Guide, X-BLOX Reference/User Guide, Xilinx ABEL User Guide, Development System Reference Guide, Hardware & Peripherals User Guide, and your CAE-specific interface user guide.*

The following sections give a brief description of what information each manual contains.

#### **Development System User Guide**

This guide contains information you need during the FPGA development process. It contains an overview of design entry, design implementation, and design verification. This guide also covers how to perform a readback and boundary scan for XC4000 and XC5200 devices, as well as configuration and debugging hints.

#### Libraries Guide

The *Libraries Guide* presents information about the various Xilinxsupplied primitives and macros in your schematic editor. A crossreference assists you in determining which primitives and macros are designed for use with a particular Xilinx device family.

#### **Libraries Supplement Guide**

The *Libraries Supplement Guide* contains information about the XC4000E and XC5200 design elements. It also provides the CLB count and lists the RPMs (Relationally Placed Macros) for existing Xilinx FPGA architectures, as well as describing the constraints and attributes that are specific to the XC5200 devices.

#### X-BLOX Reference/User Guide

The *X*-BLOX Reference/User Guide describes the X-BLOX (blocks of logic optimized for Xilinx<sup>™</sup>) synthesis tool, which consists of a library of modules you can use to describe a system by means of high-level functions instead of gate-level primitives.

## Xilinx ABEL User Guide

The *Xilinx ABEL User Guide* describes the Xilinx ABEL program, which consists of a Xilinx-specific version of the ABEL design entry software and a series of translation programs. It allows you to create modules for Xilinx FPGA designs using state machines, Boolean equations, and truth tables. It also allows you to create full EPLD designs or modules for these designs.

#### **Development System Reference Guide, Volume 1**

The *Development System Reference Guide, Volume 1* provides detailed information on the various design entry programs in the XACT*step* Development System. The entry for each program includes the program's syntax, options, files, and error and warning messages. Information about program function and examples is also included.

#### **Development System Reference Guide, Volume 2**

The *Development System Reference Guide, Volume 2* guide provides detailed information on the various design implementation programs in the XACT*step* Development System. The entry for each program includes the program's syntax, options, files, and error and warning messages. Information about program function and examples is also included.

#### **Development System Reference Guide, Volume 3**

The *Development System Reference Guide, Volume 3* provides detailed information on the various design verification programs in the XACT*step* Development System. The entry for each program includes the program's syntax, options, files, and error and warning messages. Information about program function and examples is also included.

#### Hardware & Peripherals User Guide

The *Hardware & Peripherals User Guide* provides detailed information on the various hardware and peripherals in the XACT*step* Development System. This guide describes the FPGA demonstration board, which allow you to verify your design; the XPP Serial PROM Programmer; and the XChecker download cable and software.

#### **CAE Interface User Guides**

The Xilinx interface user guides include the following information:

• Design entry interface — This section gives detailed information on entering an LCA design using a Xilinx-supported schematic editor and then translating it into a Xilinx Netlist Format (XNF) file. Documentation for this section comes with a Xilinxsupported simulation package.

- Design verification interface This section gives detailed information on simulating a design using a Xilinx-supported simulator. Both timing and functional simulation are described. Documentation for this section comes with a Xilinx-supported simulation package.

- Tutorials These sections are platform-specific tutorials that walk you step by step through the major functions that your system performs, such as schematic capture and functional and timing simulation. The tutorials might also include information on design issues specific to your platform.

- Additional documentation Xilinx offers other documents including applications information and specifications that might be helpful. Check with your local sales office or field representative.

# **Chapter 2**

## **Design Entry**

This chapter introduces design entry using both schematic and textbased entry tools, highlights hierarchical design, and discusses ways to control design implementation during design entry.

Design entry takes the design from a concept to a netlist. You can enter a design with a schematic editor, a text-based tool, or both. These entry methods require Xilinx-supported third-party tools, which produce a design file in their own netlist formats.

The following sections describe each design entry method in detail.

#### Schematic Entry

Schematic tools provide a graphic interface for design entry. You can use these tools to connect symbols representing the logic components in your design. You can build your design with individual gates, or you can combine gates to create functional blocks. This section focuses on ways to enter functional blocks using library elements, the MemGen program, and the logic-design/synthesis tool X-BLOX.

#### **Library Elements**

The following sections discuss primitives, macros, and architectural resources.

#### **Primitives and Macros**

Xilinx FPGA libraries provide primitives as well as common highlevel macro functions. Primitives are basic circuit elements, such as AND and OR gates, with unique library names, symbols, and descriptions. Macros contain multiple library elements, which can include primitives and other macros. There are two types of macros you can use with Xilinx FPGAs. Soft macros, available for all FPGAs, have pre-defined functionality, but have flexible mapping, placement, and routing. Relationally placed macros (RPMs), available for XC4000/A/H and XC5200 devices only, have fixed mapping and relative placement.

#### **Architectural Resources**

Your choice of schematic symbol for a particular function is critical. For example, you can implement the standard AND4 symbol using the function generator of a CLB. If you need a D flip-flop with Asynchronous Clear and Clock Enable, you must specify a FDCE unified libraries primitive in your schematic.

The specific choice of schematic symbol also determines how registers are implemented. Registers are available in both CLBs and IOBs. If you want to ensure that a register is implemented using an IOB, you must use the corresponding I/O library primitive. See the *Libraries Guide* and *Libraries Supplement Guide* for more information.

#### MemGen for XC4000 Devices

The Xilinx memory generator, MemGen, is a convenient tool for creating RAMs and ROMs for XC4000/A/H FPGAs. MemGen creates an XNF file, a log file, and a schematic symbol, which can be used as part of the design.

You can create memories up to 32 bits wide and 256 words deep. Two 16x1 memories or a single 32x1 memory can fit in one XC4000 CLB. For more information on MemGen commands and capabilities, refer to "The MemGen Program" chapter in the *Development System Reference Guide*.

#### X-BLOX

The X-BLOX tool provides a library of variable-size MSI- and LSIlevel design building blocks such as adders, counters, decoders, and shift-registers. This library complements the XC3000A/L, XC3100A, XC4000/A/H, and XC5200 macro libraries, which contain simpler, fixed-size logic and gate functions. The X-BLOX tool also includes the X-BLOX software, which integrates X-BLOX library elements into your design. For further information on this software, see the *X-BLOX Reference/User Guide*.

## **Text-Based Entry**

Text-based entry is well suited for many designs, including state machines and decoders. You can use several hardware description languages (HDLs) to design Xilinx FPGAs, including ABEL-HDL, VHSIC HDL (VHDL), Verilog HDL, PALASM, MINC, and CUPL. This section highlights Xilinx ABEL, VHDL, and Verilog HDL.

## Xilinx ABEL

You can enter Boolean equations, state machine descriptions, and truth tables in ABEL-HDL using Xilinx ABEL. Xilinx ABEL is best used for creating designs that are functional blocks within designs entered with a schematic editor. XMake merges functional blocks containing logic described in ABEL-HDL with the rest of your design during design entry. For a more detailed description of Xilinx ABEL, refer to the *Xilinx ABEL User Guide*.

#### XSI (Xilinx Synopsys Interface)

The XSI design tool kit enables you to implement FPGA designs using the Synopsys High-Level Design Automation (HLDA) synthesis software. Synopsys HLDA synthesis software creates and optimizes circuit designs from hardware description languages such as VHDL and Verilog HDL.

Both the Synopsys Design Compiler and the FPGA Compiler support the XC3000/A/L, XC4000/A/H and XC5200 libraries.

## **Hierarchical Design**

Schematics usually contain hierarchy, which is important because it:

- Helps you conceptualize your design.

- Adds structure to your design.

- Makes it easier to debug your design.

- Makes it easier to combine different design entry methods (schematic and text) for different parts of your design.

- Makes it easier to design incrementally. Incremental design consists of designing, implementing, and verifying individual sub-blocks that build a design in stages.

- Facilitates concurrent design. Concurrent design is the process of dividing a design among a number of people who develop different parts of the design in parallel.

#### **Hierarchical Names**

A specific hierarchical name indicates each library element, unique block, and instance you create. For example, the last three terms in the name

```

/Acc/alu_1/mult_4/8count_3/4bit_0/mux_1/or2

```

might refer to the 2-input OR gate in the first instance of a multiplexer in a 4-bit counter.

**Note:** Xilinx strongly recommends that you name the components and nets in your design. In schematic editors, component names and net names are preserved and used by the XACT Design Editor. The component names and net names are also used for back-annotation and appear in the debug and analysis tools. If you do not name your components and nets, the schematic editor automatically generates the names. For example, the software might name the previous example the following:

/\$1a123/\$1b942/\$1c23/\$1d235/\$1e121/\$1g123/\$1h57

Consequently, it can be very difficult to analyze circuits with automatically generated names, since they have significance only to the Xilinx software.

## **Controlling Implementation**

If your application requires that you constrain your design, you can specify mapping and block placement during design entry.

#### Mapping

You can specify how a particular block of logic is mapped into CLBs using a CLBMAP for XC2000, XC3000, XC3000A/L, and XC3100/A FPGAs; an FMAP or HMAP for XC4000/A/H FPGAs; or, an FMAP

or F5MAP for XC5200 FPGAs. These mapping symbols can be used in your schematic. However, if you overuse these specifications, it might be harder to route your design.

#### **Block Placement**

Block placement can be constrained to a specific location, an area on the device, or along a longline. All three can be specified in a constraints (CST) file. Location and area constraints can be specified directly from the schematic. Poor block placement can adversely affect both the placement and the routing. Typically, block placement defines IOB placement.

#### **Timing Specifications**

You can specify timing requirements for paths in your design directly from your schematic for the following devices: XC3000A/L, XC3100A, XC4000/A/H, and XC5200. PPR uses these timing specifications to achieve optimum performance when placing and routing your design. See the "XACT-Performance Utility" chapter in the *Development System Reference Guide* for detailed instructions on using this feature.

## **Performing Functional Simulation**

After you have entered your design, you can either simulate or implement your design. Functional simulation tests the logic in your design to determine if it works properly. You can save a lot of time during subsequent design steps if you perform functional simulation early in the design flow. Details on functional simulation can be found in the CAE-specific interface user guide provided with your Xilinx interface.

# **Chapter 3**

# **Design Implementation**

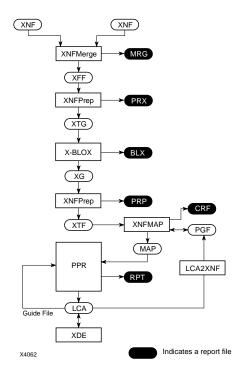

Design implementation, performed by the XMake program, generates a bitstream for a Xilinx FPGA from the design netlist. Design implementation includes the following steps: translation from the design netlist to the Xilinx Netlist Format (XNF), design optimization, merging, mapping, placement, routing, and bitstream generation. The XMake program automatically carries out all these steps.

Design flows for each family are discussed in the "Design Implementation Flows" chapter in this user guide.

Table 3-1 outlines the design implementation programs. Although XMake automatically runs many of these programs, the following table enables you to examine the role each program plays in design implementation.

| Program  | Function                                                                              | Input                                               | Output                                       | Families                                                                                   |

|----------|---------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------|

| XMake    | Automatic design implementation                                                       | Schematic output or XNF file                        | BIT file and LCA file                        | All                                                                                        |

| XNFMerge | Merges multiple<br>XNF files                                                          | XNF files                                           | Single flattened<br>XFF file                 | All                                                                                        |

| XNFPrep  | Performs a design<br>rule check (DRC)<br>and removes<br>unused and<br>redundant logic | XFF file (or XG file<br>after X-BLOX<br>processing) | XTF file (or XTG<br>file if using<br>X-BLOX) | XC2000<br>XC2000L<br>XC3000<br>XC3000A<br>XC3000L<br>XC3100<br>XC3100A<br>XC4000<br>XC5200 |