# HARDWARE DEBUGGER **REFERENCE/USER** GUIDE

**TABLE OF CONTENTS**

INDEX

GO TO OTHER BOOKS

0401313

# Contents

# Chapter 1 Introduction

| Features of the Hardware Debugger       | 1-1 |

|-----------------------------------------|-----|

| Design and Hardware Considerations      | 1-2 |

| Design Entry and Bitstream Generation   | 1-4 |

| Hardware Considerations                 | 1-4 |

| Configuration Mode                      | 1-4 |

| Target Board Selection                  | 1-4 |

| Single or Multiple Device Configuration | 1-5 |

| Cable Connections                       | 1-5 |

| Downloading                             | 1-5 |

| Verification                            | 1-5 |

| Debugging                               | 1-5 |

|                                         |     |

# Chapter 2 Getting Started

| Starting and Exiting the Hardware Debugger | 2-1 |

|--------------------------------------------|-----|

| Using the Hardware Debugger Interface      | 2-2 |

| Main Window                                | 2-2 |

| Title Bar                                  | 2-2 |

| Menu Bar                                   | 2-2 |

| Toolbar                                    | 2-3 |

| Control Panel                              | 2-3 |

| Status Bar                                 | 2-4 |

| Commands and Dialog Boxes                  | 2-4 |

| File Open/File Save Dialog Boxes           | 2-4 |

| Filter Dialog Boxes                        | 2-5 |

| Selection Dialog Boxes                     | 2-6 |

| Selecting Commands and Dialog Box Options  | 2-7 |

| Using the Mouse                            | 2-7 |

| Using the Keyboard                         | 2-8 |

| Using the Online Help and Tutorial         | 2-8 |

| Online Help                                |     |

| Help on Dialog Boxes                       | 2-8 |

| Help for Menu Items                        | 2-9 |

| Object-Click Help                          | 2-9 |

|                                            |     |

|           | Online Tutorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-9                                                                                                                                                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 3 | Design Preparation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                               |

|           | Creating a Design for Use with the Hardware Debugger<br>Preparing a Downloadable Design<br>Preparing a Design for Verification and Debugging<br>XC2000/XC3000 Designs<br>XC4000/XC5200 Designs<br>Generating Configuration Data Files<br>Creating Files for a Single XC2000 or XC3000 Device<br>Creating Files for a Single XC2000 or XC3000 Device<br>Creating Downloadable Files<br>Creating Files for Verification and Debugging<br>Creating Files for a Single XC4000 or XC5200 Device<br>Creating Files for a Single XC4000 or XC5200 Device<br>Creating Files for Verification and Debugging<br>Creating Files for Verification and Debugging<br>Creating Files for Verification and Debugging | 3-1<br>3-1<br>3-2<br>3-3<br>3-4<br>3-4<br>3-4<br>3-7<br>3-8<br>3-8<br>3-8<br>3-11                                                                             |

| Chapter 4 | Connecting Your Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                               |

|           | Cable Descriptions<br>Serial Cable<br>Parallel Cable<br>XChecker Cable<br>Connecting the Cable to Your Host System<br>Parallel Cables<br>Serial and XChecker Cables<br>Setting Up the Hardware<br>Connecting the Cable to Your Target System<br>Serial and Parallel Cables<br>XChecker Cable Connectors<br>XChecker Cable Connectors<br>XChecker Cable Pins<br>Connecting for Download<br>Connecting for Verification<br>Connecting RT and RD<br>Connecting for Synchronous Debugging<br>Connecting the XChecker Clock<br>Connecting an External Trigger<br>Connecting RT and RD<br>Connecting for Asynchronous Debugging<br>Setting the Cable Options<br>Cable Type<br>Baud Rate                    | $\begin{array}{c} 4-2\\ 4-2\\ 4-3\\ 4-3\\ 4-3\\ 4-4\\ 4-4\\ 4-4\\ 4-4\\ 4-5\\ 4-9\\ 4-9\\ 4-9\\ 4-9\\ 4-9\\ 4-9\\ 4-9\\ 4-10\\ 4-10\\ 4-11\\ 4-11\end{array}$ |

|           | Port<br>Resetting the Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 5 | Programming a Device or a Daisy Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                       |

| -         | Preparing for Download and Verification<br>Checking the Cable<br>Opening a Design File<br>Downloading a Design to a Target Board<br>Verifying Design Logic<br>Configuring Multiple Devices<br>Configuration<br>Verification                                                                                                                                                                                                                                                                                                                                                                                       | 5-1<br>5-2<br>5-4<br>5-5<br>5-6<br>5-6                                                                                                                                                                                                                                                |

| Chapter 6 | Debugging a Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                       |

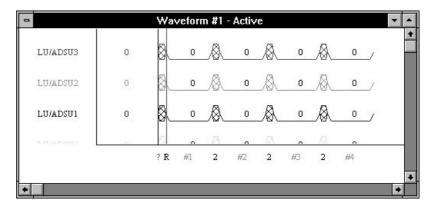

|           | Debugging a Configured FPGA<br>Debugging Overview<br>Debugging a Previously Debugged Design<br>Synchronous Mode Debugging<br>Pin Assignments<br>Debugging in the Synchronous Mode<br>Cycling the Device<br>Resetting the FPGA<br>Viewing Additional Signals<br>Viewing the Waveform in Text Mode<br>Asynchronous Mode Debugging<br>Pin Assignments<br>Debugging in the Asynchronous Mode<br>Creating a Signal Group<br>Modifying a Group from the Display List<br>Generating a Signal List<br>Creating a List of Signals to Display<br>Saving and Loading Readback Data<br>Viewing Previously Saved Readback Data | $\begin{array}{c} 6\text{-2} \\ 6\text{-2} \\ 6\text{-3} \\ 6\text{-4} \\ 6\text{-9} \\ 6\text{-10} \\ 6\text{-10} \\ 6\text{-10} \\ 6\text{-10} \\ 6\text{-10} \\ 6\text{-11} \\ 6\text{-13} \\ 6\text{-15} \\ 6\text{-15} \\ 6\text{-16} \\ 6\text{-18} \\ 6\text{-18} \end{array}$ |

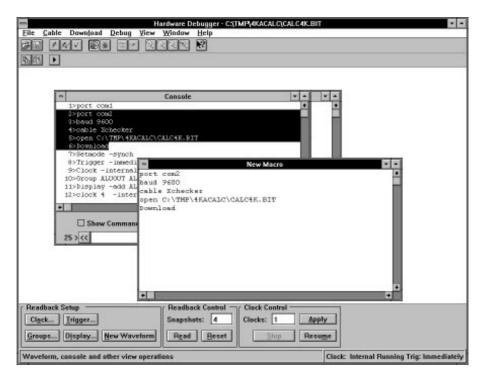

| Chapter 7 | Customizing the Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                       |

|           | Using Macros<br>Creating a Macro<br>Editing an Existing Macro<br>Running a Macro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-1<br>7-4                                                                                                                                                                                                                                                                            |

| Saving the Console Log to a File              | 7-4  |

|-----------------------------------------------|------|

| Controlling the Waveform Display Parameters   | 7-5  |

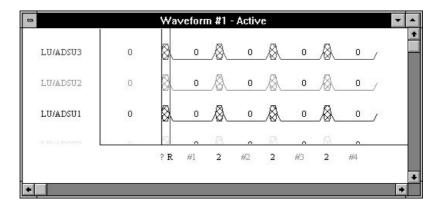

| Description of the Text Window                | 7-5  |

| Signals and Signal Groups                     | 7-6  |

| Vertical Axis                                 |      |

| Signals and Signal Groups                     |      |

| Vertical Axis                                 |      |

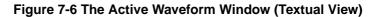

| Description of the Graphical Window           |      |

| Signals and Signal Groups                     |      |

| Vertical Axes                                 |      |

| Horizontal Axis                               |      |

| Grid                                          | 7-8  |

| Changing the Size of the Waveform             |      |

| Controlling the Position of the Windows       |      |

| Changing the Radix of Displayed Signal Groups |      |

| Changing the Color of the Waveform Window     |      |

| Moving a Signal                               |      |

| Resetting the Color to Its Default            | 7-12 |

|                                               |      |

# Chapter 8 Menu Command Reference

| Menus                               | 8-1 |

|-------------------------------------|-----|

| File Menu                           | 8-1 |

| Cable Menu                          | 8-2 |

| Download Menu                       | 8-2 |

| Debug Menu                          | 8-3 |

| View Menu                           | 8-3 |

| Window Menu                         |     |

| Help Menu                           | 8-5 |

| Alphabetical Listing of Commands    | 8-5 |

| 1, 2, 3, 4 (File Menu)              |     |

| 1, 2, 3, (Window Menu)              |     |

| About Hardware Debugger (Help Menu) |     |

| Apply Clock[s] (Debug Menu)         | 8-6 |

| Arrange Icons (Window Menu)         |     |

| Asynchronous Mode (Debug Menu)      | 8-6 |

| Axes (View Menu)                    |     |

| Background (View Menu)              |     |

| Cascade (Window Menu)               |     |

| Change Color (View Menu)            | 8-8 |

| Change Radix (View Menu)            |     |

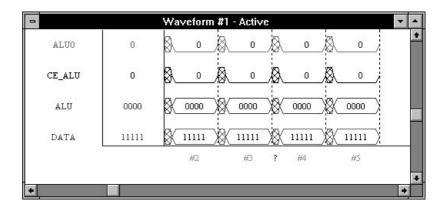

| Clock (Debug Menu)                  |     |

|                                     |     |

| Close (File Menu)                        |      |

|------------------------------------------|------|

| Communications (Cable Menu)              | 8-12 |

| Console (View Menu)                      | 8-13 |

| Contents (Help Menu)                     | 8-15 |

| Control Panel (View Menu)                |      |

| Control Panel for Synchronous Mode       | 8-15 |

| Control Panel for Asynchronous Mode      |      |

| Display Signals (Debug Menu)             | 8-18 |

| Download Design (Download Menu)          | 8-19 |

| Download and Verify (Download Menu)      | 8-20 |

| Exit (File Menu)                         | 8-21 |

| Full (View Menu)                         | 8-21 |

| Grid (View Menu)                         |      |

| Logic Level of Header Pins (Cable Menu)  | 8-22 |

| Move Signal (View Menu)                  |      |

| New Macro (File Menu)                    | 8-23 |

| Display Area                             |      |

| Macro Toolbar Buttons                    |      |

| New Waveform (Debug Menu)                | 8-24 |

| Number of Clocks to Apply (Debug Menu)   | 8-25 |

| Number of Snapshots to Read (Debug Menu) |      |

| Open Bitstream (File Menu)               | 8-26 |

| Open Macro (File Menu)                   |      |

| Open Readback Data (File Menu)           | 8-30 |

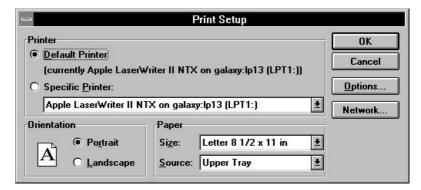

| Print (File Menu)                        | 8-32 |

| Print Setup (File Menu)                  |      |

| Read FPGA (Debug Menu)                   | 8-33 |

| Refresh (View Menu)                      |      |

| Reset Color to Default (View Menu)       | 8-34 |

| Reset (Cable Menu)                       |      |

| Reset FPGA (Debug Menu)                  | 8-34 |

| Resume Clock (Debug Menu)                | 8-34 |

| Run Macro (File Menu)                    | 8-35 |

| Save Macro/Save Macro As (File Menu)     | 8-35 |

| Save Readback (File Menu)                | 8-37 |

| Search for Help on (Help Menu)           | 8-39 |

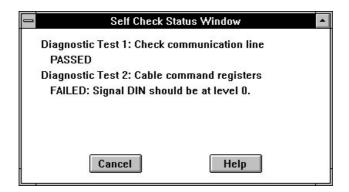

| Self-Check (Cable Menu)                  | 8-40 |

| Self-Check Diagnostics                   | 8-41 |

| Troubleshooting                          | 8-42 |

| Settings (Debug Menu)                    |      |

| Signals (View Menu)                      | 8-43 |

| Signal Groups (Debug Menu)       | 8-43 |

|----------------------------------|------|

| Status Bar (View Menu)           | 8-45 |

| Stop Clock (Debug Menu)          | 8-46 |

| Synchronous Mode (Debug Menu)    | 8-46 |

| Text Data (View Menu)            | 8-46 |

| Tile (Window Menu)               | 8-47 |

| Toolbar (View Menu)              | 8-48 |

| Trigger — Async (Debug Menu)     | 8-51 |

| Trigger — Sync (Debug Menu)      | 8-52 |

| Tutorial (Help Menu)             | 8-54 |

| Verify Bitstream (Download Menu) | 8-54 |

| Vertical Grid (View Menu)        | 8-55 |

| Waveform (View Menu)             | 8-55 |

| Zoom In (View Menu)              | 8-57 |

| Zoom Out (View Menu)             | 8-57 |

| Zoom to Region (View Menu)       | 8-58 |

|                                  |      |

# Chapter 9 Glossary of Terms

| Definitions            | 9-1 |

|------------------------|-----|

| aliases                | 9-1 |

| asynchronous debugging | 9-1 |

| BIT file               | 9-1 |

| bitstream (BIT file)   |     |

| CCLK pin.              | 9-2 |

| CLKI pin               | 9-2 |

| CLKO pin               |     |

| console log            |     |

| control panel          | 9-2 |

| debugging              |     |

| DIN pin                |     |

| D/P pin (XC3000)       | 9-3 |

| DONE pin (XC4000)      |     |

| downloading            |     |

| external clock         |     |

| GND pin                | 9-3 |

| group                  | 9-4 |

| INIT pin               |     |

| internal clock         |     |

| (.II) file             |     |

| main screen            |     |

| menu bar               |     |

| number of clock cycles | 9-5 |

|------------------------|-----|

| probing                | 9-5 |

| PROG pin               | 9-5 |

| PROM file              | 9-5 |

| RBT file               | 9-5 |

| readback               | 9-5 |

| RD pin                 | 9-6 |

| RST pin                |     |

| RT pin                 |     |

| snapshot               |     |

| states                 |     |

| status bar             |     |

| synchronous debug      |     |

| TCK pin                |     |

| TDI pin                |     |

| TMS pin                |     |

| toolbar                |     |

| TRIG pin               |     |

| trigger                |     |

| VCC pin                |     |

| verification           |     |

| waveform               |     |

|                        | 50  |

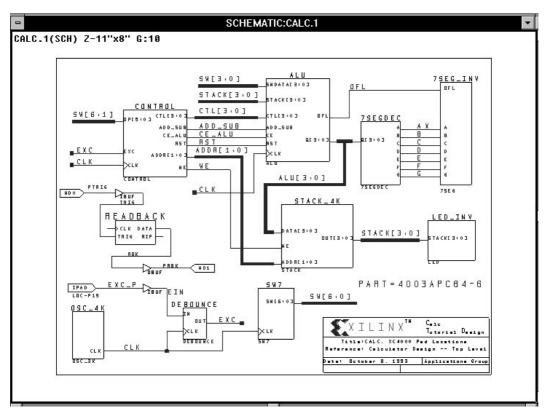

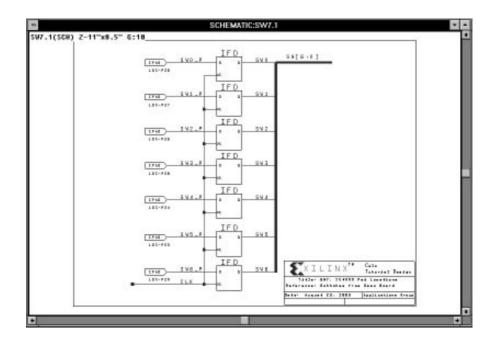

# Chapter 10 CALC Tutorial

| Testing the Design Using a Demonstration Board | 10-2  |

|------------------------------------------------|-------|

|                                                |       |

| Preparing the Design for Readback              |       |

| Generating a Bitstream                         | 10-3  |

| Connecting the Cable                           | 10-7  |

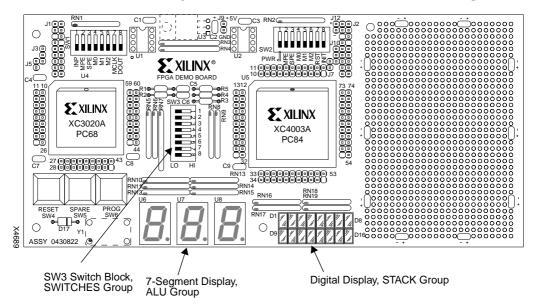

| XC3000 Demonstration Board                     | 10-9  |

| XC4000 Demonstration Board                     | 10-10 |

| FPGA (XC3000A/XC4000A) Demonstration Board     | 10-10 |

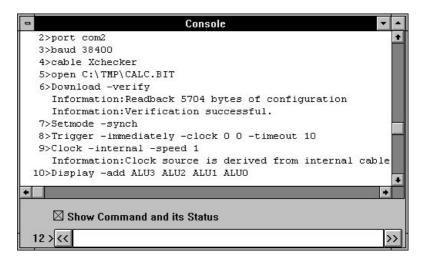

| Downloading and Verifying the Bitstream        | 10-12 |

| Testing the Design                             | 10-14 |

| Understanding Opcodes                          | 10-17 |

| Operating the Board 7-Segment Display          |       |

| Opcode Examples                                | 10-17 |

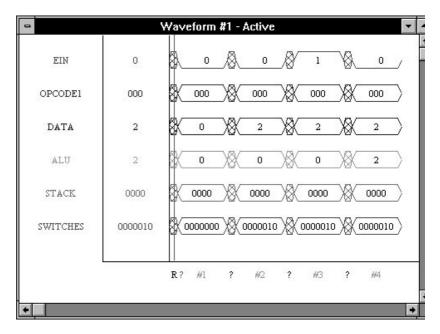

| Debugging the Device                           | 10-19 |

| Setting the Debugging Mode                     | 10-19 |

| Specifying Signal Groups                       |       |

| Adding Signal Groups to Your Display List      | 10-21 |

| Adding the EIN Signal to the Display List      |       |

|                                                | 10 22 |

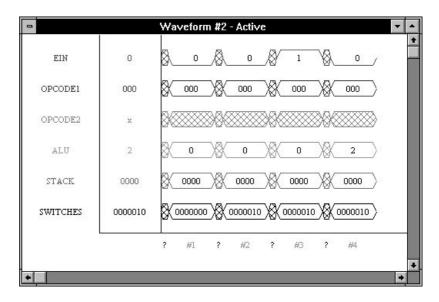

| Reading the Device States                     | 10-23 |

|-----------------------------------------------|-------|

| Changing the Signals Groups Radix             | 10-23 |

| Debugging Example                             | 10-24 |

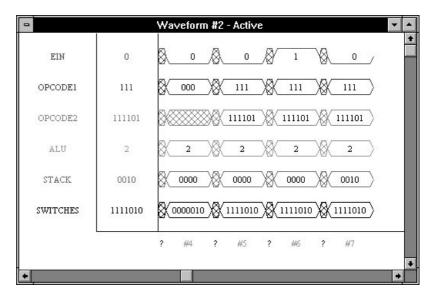

| Capturing the Add Operation                   | 10-25 |

| Adding and Removing Signal Groups             | 10-27 |

| Adding a Signal Group to the Display List     | 10-28 |

| Removing a Signal Group from the Display List | 10-28 |

| Updating the Waveform                         | 10-28 |

| Capturing the Push Operation                  | 10-29 |

# Appendix A Diagnostics and Board Compatibility

| Testing the XChecker Cable      | A-1 |

|---------------------------------|-----|

| Completing a Cable Self-Check   | A-1 |

| Using the 3 V Adapter           |     |

| Connecting the 3 V Adapter      |     |

| Verifying 3 V Adapter Operation |     |

#### **Appendix B Console Commands**

| Conventions                      |     |

|----------------------------------|-----|

| Alphabetical Listing of Commands | B-2 |

| Baud                             | B-3 |

| Cable                            | B-3 |

| Clock                            | B-4 |

| Display                          | B-6 |

| Download                         |     |

| Exit                             | B-7 |

| Force                            |     |

| Group                            |     |

| Open                             |     |

| Port                             |     |

| Quit                             |     |

| Readfpga                         |     |

| Reset                            |     |

| Run                              |     |

| Setmode                          |     |

| Trigger                          |     |

| Verify                           |     |

| ,                                | -   |

|                                  |     |

#### Index ...... i

# **Trademark Information**

# **Chapter 1**

# Introduction

The Hardware Debugger is a graphical user interface that allows you to download a design to a device, verify the downloaded configuration, and display the internal states of the programmed device. Use the program to do the following tasks:

Download a BIT file to an FPGA, or a PROM file to a daisy chain.

- Verify the configuration data of a single device using an XChecker cable.

- Debug the internal logic states of a configured device using an XChecker cable.

The Hardware Debugger replaces the XChecker program.

Refer to the "Programming a Device or a Daisy Chain" chapter for information on how to open, download, and verify your design. Refer to the "Debugging a Device" chapter for information on how to read back and debug your configured device.

**Note:** Before invoking the Hardware Debugger, you must connect the configuration cable to your PC and target board; you must also be aware of the design and hardware issues described in the section, "Design and Hardware Considerations" in this chapter.

# Features of the Hardware Debugger

After creating and implementing a design, you can use the Hardware Debugger to download, verify, and debug.

Downloading refers to the process of programming or configuring a device.

Verification consists of reading the configuration data that was sent to the device and comparing it to the original design to ensure that the design was received by the device.

Debugging consists of reading internal device states to verify that the design is functioning correctly. When using the XChecker cable, the Hardware Debugger can interrogate and display the internal nodes of an FPGA device that are listed in Figure 1-1.

#### Table 1-1 Probe Points in FPGA Devices

| XC4000          | XC2000/XC3000/XC5000 |

|-----------------|----------------------|

| CLB ouputs      | CLB ouputs           |

| IOB outputs     | IOB outputs          |

| RAM/ROM outputs | —                    |

The following is a summary of the Hardware Debugger features:

- Configuration of one or more devices.

- Verification of configuration data for single devices.

- Debugging a single device in synchronous mode or asynchronous mode.

- Generation of multiple graphical and textual waveforms for specific signals and specific device states.

- Specification of signal groups for debugging.

- Saving of waveforms for later use.

- Reuse of debugging settings from one session to another.

- Support for commands from the Console window command bar.

- Creation of macros, that is command scripts, by copying commands from the Console window into a macro window and saving them into macro files.

# **Design and Hardware Considerations**

Before using the Hardware Debugger, you must be aware of the requirements summarized in the following table as early as the

design entry phase. These requirements are dealt with in detail in the chapters "Design Preparation" and "Connecting Your Cable."

|                                                                     | Downloading                                                                             | Verification                                                                                                                                                                                                                                                                                             | n    | Debugging                                                                                     |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------|

| File Types                                                          | BIT, RBT, PROM                                                                          | BIT, LL                                                                                                                                                                                                                                                                                                  |      |                                                                                               |

| Design symbols<br>for XC4000/<br>XC5200 devices                     | none                                                                                    | READBACK<br>STARTUP *                                                                                                                                                                                                                                                                                    |      |                                                                                               |

| Configuration/<br>readback options<br>for XC2000/<br>XC3000 devices | Enable pull-up resistor<br>on DONE/PGM pin                                              | Enable Readback Never Once X On Command X Enable pull-up resistor on D/P pin                                                                                                                                                                                                                             |      |                                                                                               |

| Configuration/<br>readback options<br>for XC4000/<br>XC5200 devices | Enable pull-up on<br>DONE pin                                                           | Readback Control         X       Readback Clock:         X       CCLK (for XChecker)         User Clock       User Clock         X       Capture CLB and IOB Outputs When TRIG Goes Active         X       Abort Readback When TRIG Goes Inactive         X       Abort Readback When TRIG Goes Inactive |      | DB Outputs When                                                                               |

| Cable Type                                                          | Any                                                                                     |                                                                                                                                                                                                                                                                                                          | XChe | ecker                                                                                         |

| Pins Used                                                           | VCC<br>GND<br>CCLK<br>D/P (DONE)<br>DIN<br>PROG (XC4000)<br>INIT (XC3000/XC4000)<br>RST | VCC<br>GND<br>CCLK<br>RT<br>RD                                                                                                                                                                                                                                                                           |      | VCC<br>GND<br>CCLK<br>RT<br>RD<br>TRIG <sup>*</sup><br>CLKI <sup>*</sup><br>CLKO <sup>*</sup> |

| Configuration<br>Mode                                               | Slave                                                                                   | N/A                                                                                                                                                                                                                                                                                                      |      | N/A                                                                                           |

#### Table 1-2 Requirements for Hardware Debugger Operations

\*Optional.

# **Design Entry and Bitstream Generation**

You will need access to certain signals depending on whether you generate a design for downloading only or for debugging too.

• For downloading only, use any of the three configuration data file types (BIT, RBT, or PROM) and any download cable. You do not need any special symbols or translation options to generate the configuration data.

**Note:** To create a PROM file using multiple device configuration data files, use the PROM File Formatter. For more information on how to use the PROM File Formatter, see the *PROM File Formatter Reference/ User Guide*.

• For single device verification or debugging, use a BIT file generated with readcapture enabled from a design that includes the READBACK symbol for XC4000/XC5200 devices only, and optionally, the STARTUP symbol. In addition, you need an XChecker cable.

# **Hardware Considerations**

Before using the Hardware Debugger, you need to make some decisions about the hardware you will be using.

# **Configuration Mode**

When using the download cables to configure a device or daisy chain, you must set the configuration mode of the devices being configured to slave serial. Refer to the *Development System User Guide* for information on how to set the mode pins.

# **Target Board Selection**

Your target board can be either a Xilinx FPGA demonstration board or your own PC board. The demonstration boards can be used to test most designs.

• If you will be using an FPGA demonstration board, set up the board as explained in the "Calc Tutorial" chapter in this guide or in the *Hardware & Peripherals User Guide*.

You must set the board switches and connect the appropriate cable.

• If you will be using a PC board, you must configure the board and connect the appropriate cable. Refer to the "Connecting Your Cable" chapter for information.

# Single or Multiple Device Configuration

You may configure one device or a daisy chain:

- To configure a single device, connect the pins as specified for that particular device type. See Table 4-1 in the "Connecting Your Cable" chapter for information on pin connections.

- For a daisy chain of devices, connect the pins of the lead device for downloading as specified in Table 4-1 in the "Connecting Your Cable" chapter. Connect the pins of the slave devices to the lead device as described in the *The Programmable Logic Data Book*.

# **Cable Connections**

You can perform three main operations using the Hardware Debugger. Each operation requires a specific setup and, in the case of verification and debugging, a particular download cable. Refer to Table 4-1 in the "Connecting Your Cable" chapter for cable connections information for each operation.

# Downloading

Connect the cable header connector to your cable assembly and to the configuration pins of your target board. If you have an XChecker cable, connect a cable header connector to the outermost slot of the XChecker cable assembly.

# Verification

For this operation, you must use an XChecker cable. Connect both header connectors.

# Debugging

Determine which debugging mode, synchronous or asynchronous, you will use and attach the XChecker header connectors accordingly.

# **Chapter 2**

# **Getting Started**

This chapter explains how to invoke the Hardware Debugger. It describes the main screen and the three major tasks you can complete: download a design, verify configuration data, and debug the states of a configured device. In addition, it outlines the design and hardware requirements for using the Hardware Debugger.

# Starting and Exiting the Hardware Debugger

The Hardware Debugger is a Windows application and can be invoked several ways.

If the Hardware Debugger has been installed as a stand-alone application, the Hardware Debugger icon is present in the XACT*step* program group in the Program Manager. To invoke the Hardware Debugger, double-click on the Hardware Debugger icon in the XACT*step* program group. After invoking the program, use the Open command from the File menu to open the desired configuration file.

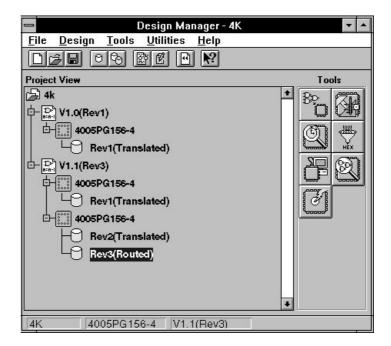

You can also invoke the Hardware Debugger from within the Design Manager. To invoke the Hardware Debugger on a specific design, select the desired revision in the Project View, then click on the Hardware Debugger button in the Tools panel. The configuration file is loaded into the Hardware Debugger automatically.

Figure 2-1 Hardware Debugger Icon

**Note:** Before invoking the Hardware Debugger, you must connect the configuration cable to your PC and target board; you must also be aware of the design and hardware issues described in the section, "Design and Hardware Considerations" in the "Introduction" chapter.

To exit the Hardware Debugger, select the Exit command from the File menu. If you have an open waveform window, you are asked whether you want to save the data before quitting the application.

# Using the Hardware Debugger Interface

The Hardware Debugger interface consists of the elements described in this section.

# **Main Window**

The main window, shown in Figure 2-2, is the background against which all windows are displayed. By default, the main window displays a title bar, a menu bar, a toolbar, and a status bar. A control panel appears once you select a debugging mode. You can hide the toolbar, status bar, and Control panel by selecting the Toolbar, Status Bar, or Control panel commands from the View menu.

#### Title Bar

The title bar displays the program name followed by the path of the currently loaded design.

# Menu Bar

The menu bar, located at the top of the Hardware Debugger window, includes the File, Cable, Download, Debug, View, Window, and Help menus. You can also select menu commands by typing the letter underlined in the menu name while holding down the Alt key. Refer to the chapter titled "Command Reference" for information on the menu commands.

| ourronn acongri paul                                                                           | Hardware Debugger- CSTMP46ACALGCALC4KBT<br>File Cable Download Debug View Window Help<br>Synchronous Debug                                                                                                                                                                     | v =                                       |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Tool Tips,<br>displays the name of<br>the button if the cursor<br>is parked on that<br>button. |                                                                                                                                                                                                                                                                                |                                           |

| Control Panel, displayed when                                                                  |                                                                                                                                                                                                                                                                                |                                           |

| a debug mode is selected.                                                                      | Readback Setup         Readback Control         Clock Control           Clock         Trigger         Snapshots:         4         Clocks:         1         Appl           Groups         Display         New Waveform         Rgad         Beset         Stop         Person | y                                         |

| describes selected function.                                                                   | Synchronous Debug                                                                                                                                                                                                                                                              | Clock: Internal Running Trig: Immediately |

Figure 2-2 Hardware Debugger Main Window

# Toolbar

The toolbar is located below the menu bar. It displays several buttons, which you can use to specify commands directly. The toolbar offers an alternative to the menu commands. To get a short description of a toolbar button, park the mouse pointer over the button. After about 2 seconds, a small pop-up text box appears giving more information about that button. This feature is called Tool Tips. The Tool Tips feature displays the name of the button function while the status bar provides similar information.

#### **Control Panel**

The Control panel, which is displayed once you select a debugging mode, consists of buttons and fields that you can use to control the active debugging session.

#### Status Bar

The status bar, located at the bottom of the Hardware Debugger window, provides command and processing information.

# **Commands and Dialog Boxes**

You communicate with the Hardware Debugger by selecting commands from the menu, the toolbar, or the Control panel. Alternatively, you can enter commands from the Console window command bar. Most commands display dialog boxes on which you specify information and options.

All dialog boxes have an OK button and a Cancel button. Moreover, most dialog boxes also have a Help button, a Network button, or both.

- Click on the **OK** button to exit the dialog box and process the information defined on the dialog box.

- Click on the **Cancel** button to exit the dialog box without processing the information defined on the dialog box.

- Click on the **Help** button to get context-sensitive help for the current dialog box.

- Click on the **Network** button to access your network drives. This button is available on Windows for Workgroups installations and is active only for certain PC networks such as Novell.

There are three types of command dialog boxes: file open/file save dialog boxes, filter dialog boxes, and selection dialog boxes.

# File Open/File Save Dialog Boxes

The standard file open and file save dialog boxes allow you to load a configuration data file, a saved waveform, or a saved macro; and to save a waveform or a macro. This type of dialog box includes a drive, directory, and file browser as shown in Figure 2-3.

| 3                                           | Save Macro As:                                                                     |          |

|---------------------------------------------|------------------------------------------------------------------------------------|----------|

| File <u>N</u> ame:<br>*.mac                 | <u>D</u> irectories:<br>c:\tmp\4kacalc                                             | OK       |

| log.mac<br>session.mac<br>temp.mac          | * C:\<br>Comp<br>Markacalc<br>Composition<br>* * * * * * * * * * * * * * * * * * * | * Cancel |

| Save File as <u>T</u> ype:<br>Files (*.mac) | ♦ Drives: ± © c: ms-dos 6                                                          | *        |

Figure 2-3 Standard File Open/File Save Dialog Box

#### **Filter Dialog Boxes**

Filter dialog boxes allow you to specify criteria to select signals and groups for debugging. An example of filter dialog box is shown in Figure 2-4.

| -                         | Signal Groups              |              |

|---------------------------|----------------------------|--------------|

| Groups<br>New Delet       | ALUOUT *                   | OK<br>Cancel |

| Filter For Signals        | Apply Clear                | Help         |

| Available Signals         | Grouped Signals            |              |

| SVCC_211<br>SVCC_210<br>A | * > ALU3_1<br>ALU2<br>ALU1 | *            |

| ADD_SUB                   | ALU0                       |              |

| ADDR0<br>ALU/\$1N305      |                            |              |

| ALU/ADSU3<br>ALU/ADSU2    |                            |              |

| #                         | •                          |              |

| Selected 0 of 349         | Selected 0 of 4            |              |

Figure 2-4 Standard Filter Dialog Box

To use the Filter dialog boxes, follow these steps.

1. Specify the pattern of the signal names to include in your display list by typing the characters in the text box located in the Filter for Signals group.

The characters can be alphanumerical or blank characters.

2. Include one or more wildcard characters (\*) to do a global search on the specified string.

Precede the character string with a wildcard to retrieve all signal names that end the string of specified characters.

Append the wildcard to the character string to retrieve all signal names that start with the specified character string.

3. Click on the **Apply** button after specifying the Filter criteria.

The available signals list displays only the signals that match the selection criteria.

4. To clear the filter, click on the **Clear** button or backspace over the information specified in the filter text box.

# **Selection Dialog Boxes**

Selection dialog boxes allow you to specify specific values and selections. An example of selection dialog box is shown in Figure 2-5.

| 💳 Synchronous Trigger Settings                             |                              |  |  |  |

|------------------------------------------------------------|------------------------------|--|--|--|

| Trigger On :                                               | Immediately 🛨                |  |  |  |

| No. of Clock Cycles                                        |                              |  |  |  |

| Before First Snapshot                                      | 0                            |  |  |  |

| Between Snapshots                                          | 2                            |  |  |  |

| I Timeout After 10<br>I Reset Before Readback<br>OK Cancel | Seconds<br>k<br><u>H</u> elp |  |  |  |

Figure 2-5 Standard Selection Dialog Box

# **Selecting Commands and Dialog Box Options**

To choose a menu item, a toolbar button, or a dialog box option, you can use the mouse or the keyboard.

# **Using the Mouse**

1. Move the mouse cursor over the object you want to select: a toolbar button, a menu option, or a dialog box option; then, click on the left mouse button to select the object.

If you clicked on a toolbar button, a list box or a dialog box appears. If you clicked on a menu, menu options are displayed and you must select a menu option.

- 2. To exit a dialog box without selecting anything, select the Cancel button or double-click on the close box in the upper left corner of the dialog box.

- 3. To get help, click on the Help button on the dialog box.

# Using the Keyboard

You can use the keyboard to select objects on your screen, such as a dialog box button or a menu option.

1. To select a dialog box option, use the **Tab** key to position the cursor on that object and highlight it. Press the **Enter** key to process the selection.

To exit a dialog box without selecting anything, press the **Escape**. key.

- To choose a menu and display its options, press the Alt key and the appropriate underlined letter key corresponding to the menu you want. For example press Alt-F to select the File menu.

- 3. Use the arrow keys to scroll down the list of options in a menu or list box. Press Enter when the option you want to use is highlighted or, in the case of a menu item, press the underlined letter corresponding to the menu option you want. For example, press the N key to select the New command of the File menu.

- 4. To get help, press the Alt key down and type the letter H.

# Using the Online Help and Tutorial

The Hardware Debugger includes an online help tool that you can invoke from the menu bar, the toolbar, and the dialog boxes. It also includes an online tutorial that demonstrates the program features.

# **Online Help**

You can access the online help Table of Contents by selecting Contents from the Help menu.

Context-sensitive help refers to the online help available from a dialog box that you are currently using, the help available for a menu command, or the help available for a screen object.

# Help on Dialog Boxes

To get context-sensitive help for the current dialog box, either click on the dialog box Help button or press down the Alt key while typing the letter H on your keyboard.

# Help for Menu Items

To get context-sensitive help for a menu item, press the F1 function key on your keyboard while selecting the menu item.

# **Object-Click Help**

To get help on a screen object, namely a window, a part of the screen, a toolbar or control panel button, follow these instructions.

1. Click on the Help toolbar button, shown in Figure 2-6.

#### Figure 2-6 Help Toolbar Button

The help cursor is displayed and the help button is in the buttondown mode.

- 2. Move the help cursor to the object for which you need help.

- 3. After positioning the help cursor on the appropriate object, press the left mouse button.

The help tool displays the corresponding Help page and the Help button returns to the button-up state.

# **Online Tutorial**

To access the online tutorial, select Tutorial from the Help menu. The tutorial page is displayed. Follow the instructions on your screen to view definitions, procedures, and demonstrations of the procedures.

# **Chapter 3**

# **Design Preparation**

This chapter discusses how to prepare a design for use with the Hardware Debugger and how to generate the proper configuration files. The first section, "Creating a Design for Use with the Hardware Debugger," covers the special components needed to perform some of the Hardware Debugger operations. The second section, "Generating Configuration Data Files," discusses the various file types used by the Hardware Debugger and the options that must be specified to create them correctly.

# Creating a Design for Use with the Hardware Debugger

To create a design that you can use with the Hardware Debugger, follow the design generation instructions for the type of operation you want to complete for your specific device.

# Preparing a Downloadable Design

When using the Hardware Debugger to download a design only, you do not need any special components in the design.

# Preparing a Design for Verification and Debugging

Follow the steps outlined in the section for the device family you are targeting XC2000/XC3000 or XC4000/XC5200.

#### XC2000/XC3000 Designs

You achieve both configuration verification and design debugging by probing the device's internal states. This process is known as readback. For XC2000 and XC3000 devices, a readback is initiated

when a Low to High transition is applied to the M0/RTRIG pin. Once the readback has begun, the serial readback data is presented on the M1(RDATA) pin. Because the readback pins are dedicated pins, you do not need any special components in the design.

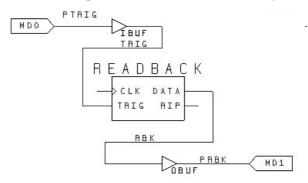

# XC4000/XC5200 Designs

To provide more flexibility, the XC4000/XC5200 readback signals (RTRIG and RDATA) can be assigned to any of the user programmable device pins as well as the M0 and M1 pins. Because the readback signals are user programmable, you must use the READBACK component in the design when using the Hardware Debugger to verify or debug an XC4000 or an XC5200 device.

To prepare the design for verifying or debugging, use the following steps:

- 1. Include the READBACK macro in the design schematic.

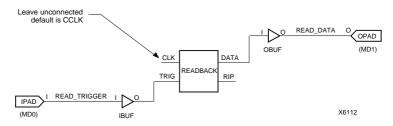

- Connect IPAD, OPAD, IBUF, and OBUF primitives to the TRIG and DATA pins of the READBACK macro as shown in Figure 3-1. You can then lock the IPAD and OPAD components to any of the user-programmable I/O locations.

**Note:** If you want TRIG and DATA to correspond to the mode pins M0 and M1, replace the IPAD and OPAD primitives with the special primitives MD0 and MD1.

#### Figure 3-1 READBACK Symbol

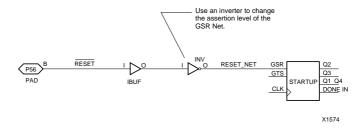

3. If you plan on having the Hardware Debugger reset the flip-flops in the design, include the STARTUP symbol and connect the GSR (XC4000) or GR (XC5200) input pin to an unused input of the target device. You will later connect the input to the XChecker cable.

#### Figure 3-2 XC4000 STARTUP Symbol

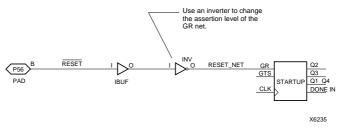

**Note:** Because the XC4000/XC5200 Reset is active High and the Hardware Debugger assumes active Low, the signal sent from the Hardware Debugger through XChecker must be inverted as shown in Figure 3-2 and Figure 3-3.

#### Figure 3-3 XC5200 STARTUP Symbol

The inverter preceding the STARTUP symbol implements the Active-Low Reset asserted by the Hardware Debugger.

# **Generating Configuration Data Files**

Once you have translated the design, you must generate the configuration data files. The Hardware Debugger can download to a chain of multiple devices, known as daisy chain, as well as individual devices. In addition, for single devices, the Hardware Debugger can verify the downloaded configuration and probe the internal states of the device. This process of probing a configured device is also known as readback.

To generate a bitstream, open the implemented design from the Design Manager. If you do not have a project for your design, use the

Design Manager to create a project for that design. If you have a project for your design but the design is not implemented, run the Translate command from the Design menu to read in the changes made in the schematic and to create a new version reflecting the updated schematic, then implement the design as explained in the *Design Manager/Flow Engine Reference/User Guide*.

# Creating Files for a Single XC2000 or XC3000 Device

To configure an XC2000 or XC3000 device, you need a bitstream, which can be either a BIT file, an RBT file, or a PROM file. To verify and/or debug a design, you must use a BIT file and have a logic allocation file in your design directory. Use the Design Manager to generate the necessary configuration files.

# **Creating Downloadable Files**

Follow these steps to prepare your XC2000 and XC3000 designs for downloading:

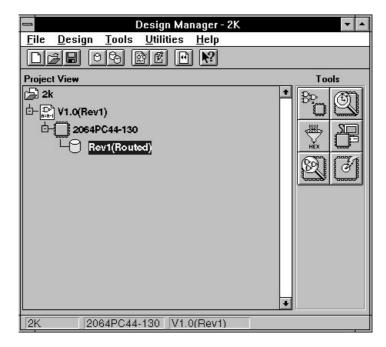

From the Design Manager, click the left mouse button on the routed design icon, as shown in Figure 3-4. Then select the Implement command from the Design menu.

#### Figure 3-4 Routed XC2000 Design in the Design Manager

The Design Manager Implementation Options dialog box is displayed, as shown in Figure 3-5.

| XC2000 Design Implementation Options |                   |                     |           |              |

|--------------------------------------|-------------------|---------------------|-----------|--------------|

| Control Files<br>Guide Design:       | None              | Ŧ                   |           |              |

| Constraints File:                    | -                 |                     |           | Browse       |

| Program Option T                     | emplates          |                     |           |              |

| Implementation:                      | User1             | Edit Tem            | plate     |              |

| Configuration:                       | User1             | . <u>+</u> Edit Tem | plate     |              |

| Optional Targets                     |                   |                     |           | 1            |

| -                                    | g Simulation Data | Produce Timi        | ng Report |              |

| <b>Produce Config</b>                | juration Data     |                     |           |              |

| ОК                                   | Cancel            |                     |           | <u>H</u> elp |

#### Figure 3-5 Design Manager Implementation Dialog Box (XC2000)

- 2. Set Configuration Data as the target by clicking in the check box next to **Produce Configuration Data** in the Optional Targets group box.

- 3. Click on the Edit Template button corresponding to the **Configuration Program Options** template. The bitstream Configuration dialog box is displayed, as shown in Figure 3-6.

| Inputs          | C 771 C 91199           | OK           |

|-----------------|-------------------------|--------------|

| Threshold:      | ● TTL O CMOS            | Cancel       |

| Configuration F | Pin Pullups             | Default      |

| Done/Program    | : O Float 💿 Pullup      | <u>H</u> elp |

| Readback        |                         | 1            |

| Mode: O Ne      | ver 🔿 Once 🖲 On Command |              |

Figure 3-6 Design Manager Configuration Dialog Box (XC2000)

- 4. Click on **Pull-Up** next to the **Done/Program** pin in the Configuration Pin Pull-Ups group box to enable a pull-up resistor on the D/P pin.

- 5. Click on **OK** to return to the Implementation dialog box or if you want to enable the readback options, continue with the next section "Creating Files for Verification and Debugging."

- 6. Select **Run** from the Implementation dialog box to compile the design and produce the configuration data.

# **Creating Files for Verification and Debugging**

Follow these steps to implement XC2000 and XC3000 designs for verification and debugging:

- 1. Follow steps 1 through 4 in the preceding section "Creating Downloadable Files" to enable a pull-up resistor for the D/P pin for device configuration.

- 2. Enable the readback capability by specifying the **Readback** option as **On Command** on the Configuration dialog box, as shown in Figure 3-6.

The software generates a logic allocation file (*design*.ll). The *design*.ll file provides bit locations for the values of I/O, latches, and flip-flops.

**Note:** For the XC3000 device, select the **Startup/Readback** tab of the dialog box to display the readback options, then set the readback mode as **On Command**, as shown in Figure 3-7.

| -               | XC3000 Con                                             | figuration Template: User1 |                   |

|-----------------|--------------------------------------------------------|----------------------------|-------------------|

|                 | Configuration                                          | Startup/Readback           | ОК                |

| Readba<br>Mode: | ack<br>O Never O Once                                  | • On Command               | Cancel<br>Default |

| Done:           | Events<br>O Before I/Os Active<br>O Before I/Os Active |                            | <u>H</u> elp      |

#### Figure 3-7 Design Manager Configuration Template (XC3000)

- 3. Click on **OK** to return to the Implementation dialog box.

- 4. Select **Run** to compile the design and produce the configuration data.

# Creating Files for a Single XC4000 or XC5200 Device

To configure an XC4000 or XC5200 device, you need a bitstream, which can be either a BIT file, an RBT file, or a PROM file. To verify and/or debug a design, you must use a BIT file and have a logic allocation file in your design directory. Use the Design Manager to generate the necessary configuration files.

#### **Creating Downloadable Files**

Follow these steps to prepare your XC4000 and XC5200 designs for downloading:

From the Design Manager, click the left mouse button on the routed design icon, as shown in Figure 3-8. Then select the Implement command from the Design menu.

#### Figure 3-8 Routed XC4000 Design in the Design Manager

The XC4000 Design Implementation Options Dialog Box is displayed, as shown in Figure 3-9.

|                                                       | XC4000 Design                      | mplementation Options |              |

|-------------------------------------------------------|------------------------------------|-----------------------|--------------|

| - Control Files<br>Guide Design:<br>Constraints File: | None                               | Ŀ                     | Browse       |

| Program Option T<br>Implementation:<br>Configuration: | emplates<br>User1<br>User1         | Edit Template         | ]            |

| Optional Targets                                      | g Simulation Data<br>guration Data | Produce Timing Repo   | rt           |

| Run                                                   | Cancel                             | [                     | <u>H</u> elp |

#### Figure 3-9 Design Manager Implementation Dialog Box (XC4000)

- 2. Set Configuration Data as the target by clicking in the check box next to **Produce Configuration Data** in the Optional Targets group box.

- 3. Click on the Edit Template button corresponding to the **Configuration Program Options** template.

The Configuration Template dialog box is displayed as shown in Figure 3-10.

- 4. Click on **Pull-Up** next to the DONE pin in the Configuration Pins box to enable a pull-up resistor for the DONE pin.

- 5. Select **Perform CRC During Configuration** to perform a CRC check of your bitstream during configuration.

- 6. Select **Produce ASCII Configuration File** to create a raw bits text (RBT) file, which is an ASCII representation of your configuration bitstream.

| XC4000 Configuration Template: User1                                  |         |          |                   |

|-----------------------------------------------------------------------|---------|----------|-------------------|

| Configuration                                                         | Startup | Readback | ОК                |

| Configuration Rate: O Fast O Slow                                     |         |          | Cancel<br>Default |

| TDO: • Float O Pull Up O Pull Down                                    |         |          |                   |

| M1: • Float<br>Done: • Float                                          |         | Down     |                   |

| Perform CRC During Configuration     Produce ASCII Configuration File |         |          |                   |

#### Figure 3-10 Design Manager Configuration Template

- Click on OK to return to the Implementation dialog box or if you want to enable the readback options, continue with the next section "Creating Files for Verification and Debugging."

- 8. Select **Run** to compile the design and produce the configuration data.

#### **Creating Files for Verification and Debugging**

Follow these steps to implement XC4000 and XC5200 designs for verification and debugging.

- 1. Follow steps 1 through 4 in the preceding section "Creating Downloadable Files" to enable a pull-up resistor for the D/P pin for device configuration.

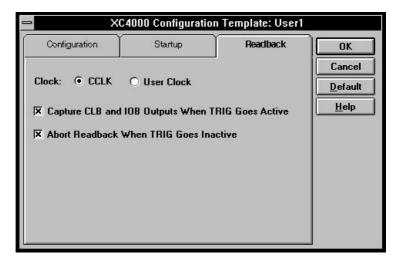

- 2. Select the **Readback** tab to access the Readback panel.

The Readback panel of the Configuration Template is displayed as shown in Figure 3-11.

3. Select **Capture CLB and IOB Outputs TRIG Goes Active** on the Readback panel. This option generates the logic allocation file (*design.ll*). For more information about configuration options,

read the Configuration chapter in the *Design Manager/Flow Engine Reference/User Guide*.

| X                 | C4000 Configuration  | n Template: User1 |                   |

|-------------------|----------------------|-------------------|-------------------|

| Configuration     | Startup              | Readback          | OK                |

| Clock: • CCLK     | O User Clock         |                   | Cancel<br>Default |

| 🗵 Capture CLB and | I IOB Outputs When T | RIG Goes Active   | <u>H</u> elp      |

| 🗵 Abort Readback  | When TRIG Goes Ina   | ctive             |                   |

|                   |                      |                   |                   |

|                   |                      |                   |                   |

|                   |                      |                   |                   |

|                   |                      |                   |                   |

|                   |                      |                   |                   |

#### Figure 3-11 Design Manager Readback Data Screen

- 4. Select **Abort Readback When TRIG Goes Inactive** on the Readback panel. This feature allows you to abort a readback in progress.

- 5. Click on **OK** to return to the Implementation dialog box.

- 6. Select **Run** to compile the design and produce the configuration data.

### **Creating Files for Multiple Devices (Daisy Chains)**

To configure a daisy chain of devices, you need a PROM file.

- 1. Produce the configuration data (BIT files) for each device, referring to the appropriate single device section

- 2. Concatenate the device BIT files using the PROM File Formatter. For more information, refer to the *PROM File Formatter Reference/ User Guide*. Ensure that the PROM file contains the bitstreams in the same order as the devices on the target board.

# **Chapter 4**

# **Connecting Your Cable**

The Hardware Debugger communicates with your device via a cable. The cable can be a serial, parallel, or XChecker cable. You can use any one of the three cables to download configuration data to a device or daisy chain of devices, but you can only use the XChecker cable to verify and debug.

This chapter describes the various download cables and the operations you can perform with each cable. It also explains how to connect your cable to your PC and target board, and how to set the target board's configuration mode. Additionally, it explains which connections are needed to perform the various Hardware Debugger tasks: download, verify, and debug.

Perform the following steps when connecting your cable:

- Determine the most suitable cable to use based on the tasks you wish to perform.

- Connect the cable to your host system.

- Configure the target board to accept the needed cable connections.

- Connect the cable to your target system.

- Power up the target board.

- Invoke the Hardware Debugger.

- Set the cable options from the Cable menu.

## **Cable Descriptions**

There are three different types of cables: serial, parallel, and XChecker.

## **Serial Cable**

You can use a serial cable only to download configuration data. The serial cable, consists of a cable with a 5-lead header connector with the following connections:  $V_{CC}$ , GND, CCLK, D/P, and DIN. It also includes a female RS-232 serial connector.

## **Parallel Cable**

You can use a parallel cable only to download configuration data. The Xilinx parallel cable consists of a 5-lead flying header connector with the following connections:  $V_{CC}$ , GND, CCLK, D/P, and DIN. It also includes a 25-pin male connector.

## **XChecker Cable**

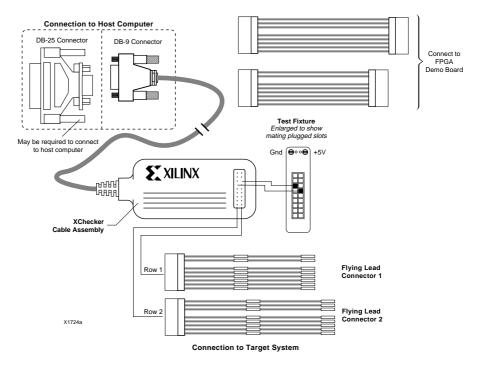

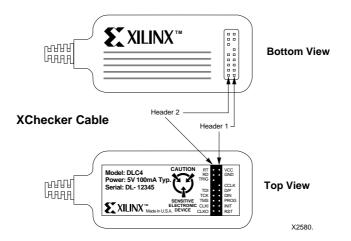

You can use the XChecker cable to download, verify, and debug. The XChecker cable assembly houses internal circuitry consisting of a Xilinx FPGA, which functions as an interface between the XChecker software and the target FPGA; a static RAM, which stores the configuration data for download and readback; and an oscillator circuit, which provides a system clock to facilitate download and readback of configuration data.

Using XChecker requires a standard DB-9 or DB-25 RS-232 serial port and may require a DB9/DB25 adapter.

The XChecker cable has 14 signal connections, plus  $V_{CC}$  and GND. It comes with two header connectors and two flying lead connectors. See Figure 4-1.

## **Connecting the Cable to Your Host System**

To install the cable, you must first connect it to the host system.

### **Parallel Cables**

If you have a parallel cable, connect it to the parallel port.

### Serial and XChecker Cables

Connect your serial or XChecker cable to your system's RS-232 serial port. A DB-9/DB-25 adapter may be required to connect the cable to your serial port. If you have a different serial port connection, you need to provide an appropriate adapter.

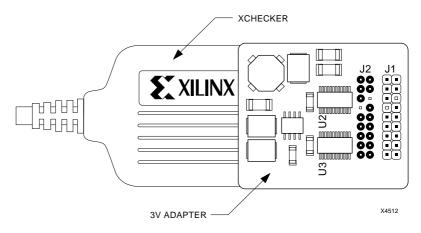

**Note:** If you are using an XChecker cable with a 3 V adapter, refer to the section "XChecker 3 V Adapter," in Appendix A, for information on how to connect and verify the operation of the 3 V adapter.

## Setting Up the Hardware

When using the serial, parallel, or XChecker cables, you must set up the configuration mode of the devices being configured as slave serial. Refer to the *Development System User Guide* or to the *The Programmable Logic Data Book* for information on how to set the mode pins.

## **Connecting the Cable to Your Target System**

This section covers cable connection to the target device. You need appropriate pins on the target system for connecting the target system board to the header connectors on the cable.

**Warning:** The cable draws its power from the target system through  $V_{CC}$  and GND. Therefore, power to the cable, as well as to the target FPGA, must be stable. Do not connect any signals before connecting  $V_{CC}$  and GND. The input/output pins of the internal XChecker FPGA should always be at a potential that is lower or equal to their respective rail voltage in order to avoid internal damage.

### **Serial and Parallel Cables**

Connect all the pins of your serial or parallel cable for downloading using the guidelines in Table 4-1 and Table 4-2.

### XChecker Cable Connectors

The XChecker cable supports two types of connectors. You can connect to the pins of your target FPGA with a flying lead connector and to the FPGA demonstration boards with a header connector.

- *Flying lead header connectors* have eight standard individual female connectors on one end that fit onto 0.025" square male pins. Each lead is labeled to identify the pin.

- *Header connectors* are standard 9-pin (8 signals, 1 key) header connectors that fit 0.025" square male pins. The pin layout is

shown in Figure 4-2. The header connectors are keyed to ensure that they are properly inserted into the cable assembly.

For each type of connector, there are two different connectors. One is keyed for the downloading signals; the second is keyed for readback signals. Header 1 is the download connector and fits on the outermost connector socket. Header 2 is the readback connector and fits on the inner connector socket. See Figure 4-2.

Figure 4-2 XChecker Cable Pins

#### **XChecker Cable Pins**

Refer to the tables in this section for information on how to connect the signal pins for specific applications. Table 4-1 shows the necessary connections for each application type, and Table 4-2 describes the pins and how to connect them.

Note: Not all of the signal pins are required for each function.

| Cable<br>Header | Pin Name                     | Download | Verification | Synchronous<br>Logic Probe | Asynchronous<br>Logic Probe |

|-----------------|------------------------------|----------|--------------|----------------------------|-----------------------------|

| 1               | V <sub>CC</sub>              | X        | Х            | Х                          | X                           |

|                 | GND                          | X        | Х            | Х                          | X                           |

|                 | CCLK                         | X        | Х            | Х                          | X                           |

|                 | D/P                          | X        |              |                            |                             |

|                 | DIN                          | X        |              |                            |                             |

|                 | PROG<br>(XC4000 only)        | X        |              |                            |                             |

|                 | INIT<br>(XC3000/XC4000 only) | X        |              |                            |                             |

|                 | RST                          | Opt      | Opt          | Opt                        | Opt                         |

| 2               | RT                           |          | Х            | Х                          | X                           |

|                 | RD                           |          | Х            | Х                          | X                           |

|                 | TRIG                         |          |              | Opt                        | Opt                         |

|                 | TDI                          |          |              |                            |                             |

|                 | ТСК                          |          |              |                            |                             |

|                 | TMS                          |          |              |                            |                             |

|                 | CLKI                         |          |              | Opt                        |                             |

|                 | CLKO                         |          |              | Х                          |                             |

| Table 4-1 | XChecker | Operation | Mode | Connections |

|-----------|----------|-----------|------|-------------|

|-----------|----------|-----------|------|-------------|

X = Connect as specified in Table 4-2 Opt = Optional.

Refer to Table 4-2 for pin descriptions and connections.

**Note:** You can connect the system trigger directly to the target FPGA RTRIG pin to latch the state of the device instead of waiting for the XChecker software to initiate the readback.

| Signal<br>Name            | Function                                                                                                                                                                                                                                               | XC2000                                                                                                                                                                                 | XC3000                                                                      | XC4000                                                                                        |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| V <sub>CC</sub>           | <i>Power</i> — Supplies V <sub>cc</sub> to the cable (5 V, 100 mA, typically)                                                                                                                                                                          | Connect to the target system $V_{CC}$                                                                                                                                                  |                                                                             | t system V <sub>CC</sub>                                                                      |

| GND                       | <i>Ground</i> — Supplies ground reference to the cable.                                                                                                                                                                                                | Connect t<br>Ground.                                                                                                                                                                   | o the targe                                                                 | t system                                                                                      |