## **Registered Subtracter**

July 17, 1998

**Product Specification**

Xilinx Inc. 2100 Logic Drive San Jose, CA 95124 Phone: +1 408-559-7778 Fax: +1 408-559-7114 E-mail: coregen@xilinx.com URL: www.xilinx.com

## Features

- Drop-in modules for the XC4000E, EX, XL, XV and Spartan families

- Two data bus inputs: 2 to 32 bits wide

- Supports both 2's complement signed and unsigned data

- Registered output

- Clock Enable for output register

- Asynchronous Clear for output register

- Uses Fast Carry logic for high speed

- High performance and density guaranteed through Relational Placed Macro (RPM) mapping and placement technology

- Available in Xilinx CORE Generator

# **Functional Description**

The Registered Subtracter module accepts two input buses, **A** and **B**, and a borrow input (**CI**), subtracts **B** and **CI** from **A**, and registers the result, **S**. The input data buses can be in either 2's complement signed or unsigned numbers. The borrow input is active low, but is otherwise interpreted as a 1-bit binary value.

The output bus width is automatically set to the input bus width plus 1 to accommodate any borrow that may be produced when subtracting the MSB's of the input operands.

### **Pinout**

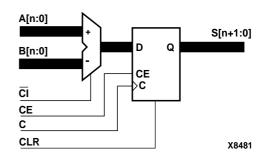

Port names for the schematic symbol are shown in Figure 1 and described in Table 1.

Figure 1: Core Schematic Symbol

### **Table 1: Core Signal Pinout**

| Signal   | Signal<br>Direction | Description                                                                                                                                                                                       |

|----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[n:0]   | Input               | A data input.                                                                                                                                                                                     |

| B[n:0]   | Input               | B data input – value is sub-<br>tracted from A data.                                                                                                                                              |

| CI       | Input               | CARRY IN – active low.<br>Treated as a 1-bit binary val-<br>ue and subtracted from A.                                                                                                             |

| CE       | Input               | CLOCK ENABLE – active<br>high signal used to enable<br>the transfer of data from the<br>subtractor to the output reg-<br>ister.                                                                   |

| С        | Input               | CLOCK – With the exception<br>of asynchronous control in-<br>puts (where applicable), con-<br>trol and data inputs are<br>captured, and new output<br>data formed on rising clock<br>transitions. |

| S[n+1:0] | Output              | DATA OUTPUT – the regis-<br>tered output of the subtract-<br>er.                                                                                                                                  |

| CLR      | Input               | ASYNCHRONOUS CLEAR -<br>Resets the output register.<br>Overrides Clock and Clock<br>Enable. Level sensitive.                                                                                      |

### **CORE Generator Parameters**

The CORE Generator parameterization window for this macro is shown in Figure 2. The parameters are as follows:

- **Component Name**: Enter a name for the output files generated for this module.

- **Input Width**: Select an input bit width from the pulldown menu. The valid range is 2-32. The same data width is applied to both the A and B inputs. The output size is automatically set to the input width plus one.

- Signed: Select Signed or Unsigned.

### Figure 2: Parameterization Window

### **Core Resource Utilization**

Table 2 shows the number of CLBs required for each available bit width.

# **Ordering Information**

This macro comes free with the Xilinx CORE Generator. For additional information contact your local Xilinx sales representative, or e-mail requests to coregen@xilinx.com.

### Table 2: Bit Width versus CLB Count

| Bit Width | CLB Count |  |  |

|-----------|-----------|--|--|

| 2         | 2         |  |  |

| 3         | 2         |  |  |

| 4         | 3         |  |  |

| 5         | 3         |  |  |

| 6         | 4         |  |  |

| 7         | 4         |  |  |

| 8         | 5         |  |  |

| 9         | 5         |  |  |

| 10        | 6         |  |  |

| 11        | 6         |  |  |

| 12        | 7         |  |  |

| 13        | 7         |  |  |

| 14        | 8         |  |  |

| 15        | 8         |  |  |

| 16        | 9         |  |  |

| 17        | 9         |  |  |

| 18        | 10        |  |  |

| 19        | 10        |  |  |

| 20        | 11        |  |  |

| 21        | 11        |  |  |

| 22        | 12        |  |  |

| 23        | 12        |  |  |

| 24        | 13        |  |  |

| 25        | 13        |  |  |

| 26        | 14        |  |  |

| 27        | 14        |  |  |

| 28        | 15        |  |  |

| 29        | 15        |  |  |

| 30        | 16        |  |  |

| 31        | 16        |  |  |

| 32        | 17        |  |  |

#### **Parameter File Information**

| Parameter Name | Туре    | Notes      |

|----------------|---------|------------|

| Component_Name | String  |            |

| Input_Width    | Integer | 2 - 32     |

| Signed         | Boolean | True/False |