# Chapter 10

# **Mentor Schematic Design Tutorial**

This chapter contains the following sections:

- "Introduction"

- "Required Background Knowledge"

- "Design Flow"

- "Software Installation"

- "Starting the Design Manager"

- "Copying the Tutorial Files"

- "Starting Design Architect"

- "Targeting the Design for the XC9000 or XCR Family"

- "Completing the Calc Design"

- "Controlling FPGA/CPLD Layout from the Schematic"

- "Modifying the Design for Non-XC4000E/EX Devices"

- "Using LogiBLOX"

- "Other Special Components"

- "Using a Constraints File"

- "Performing Functional Simulation"

- "Using Pld\_men2edif"

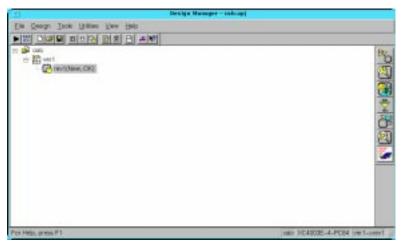

- "Using the Xilinx Design Manager"

- "Performing Timing Simulation"

- "Examining Routed Designs with FPGA Editor"

- "Verifying the Design Using a Demonstration Board"

- "Making Incremental Design Changes"

- "Command Summaries"

- "Further Reading"

## Introduction

This chapter guides you through a typical field-programmable gate array (FPGA) and complex programmable logic device (CPLD) design procedure from schematic entry to completion of a functioning device. It uses a design called Calc, a 4-bit processor with a stack. In the first part of the tutorial, you use the Design Architect, the Mentor Graphics design entry tool, to create the schematics and symbols for the Calc design. Next you use pld\_quicksim, the Mentor Graphics simulator, to perform a functional simulation on it. In the third step, you use the Xilinx Design Manager to implement the design. Finally, you verify the design's timing by again using pld\_quicksim. The simple design example used in this tutorial demonstrates many system features that you can apply to more complex FPGA and CPLD designs.

**Note:** Although this tutorial describes creating and processing FPGA designs, you can apply most of the steps to CPLD designs.

This tutorial includes instructions on the following:

- Installing the tutorial files

- Using Mentor Graphics Design Manager

- Targeting the tutorial design (Calc) for an XC4000E or an XC9000 device

- Using Design Architect

- Completing the ALU block in the Calc design

- Adding the STARTUP block to tie signals to the global reset

- Adding device information in the Calc design

- Exploring Xilinx library elements

- Exploring the XC4000E oscillator

- Controlling device layout from the schematic

- Editing the Calc design for a non-XC4000E/EX device

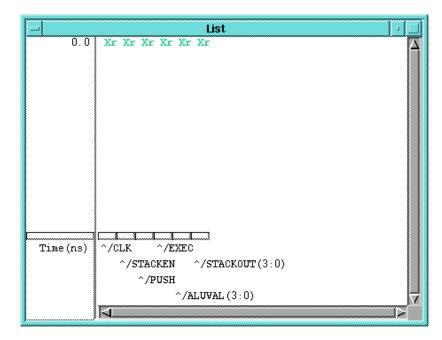

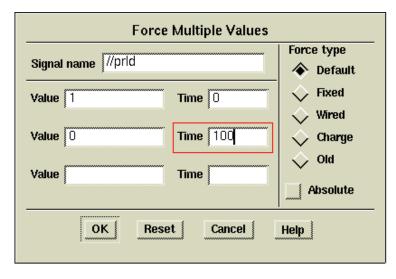

- Performing functional simulation on the Calc design in pld\_quicksim

- Converting the design to an EDIF file using pld\_men2edif

- Implementing the design using pld\_dsgnmgr

- Configuring the Xilinx Design Manager/Flow Engine

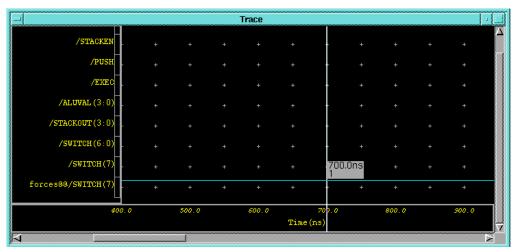

- Performing timing simulation on the routed Calc design in pld\_quicksim

- Examining routed designs with the Editor for Programmable ICs (FPGA Editor)

- Verifying the Calc design on a demonstration board

- Making incremental design changes

- Command summaries

## **Required Background Knowledge**

This tutorial assumes that you have a basic understanding of the following:

- UNIX operating system

- Motif Windows. Mentor Graphics applications conform to the Motif window style.

**Note:** When you are instructed to close a window, it is important that you exit from the window rather than iconize it.

## **Design Flow**

See the "Design Flows" section of the "Introduction" chapter for the design flow involved in using the Mentor Graphics interface. That chapter also describes the general steps for creating a design using the Mentor interface.

This tutorial describes an incremental design methodology. In incremental design, you process the design, make a small change to the design, and process the design again. You use place and route information from the previous design processing cycle to constrain subsequent cycles of the same design. When you use this method, timing information in a design remains relatively stable through many processing cycles. Also, place and route time is considerably reduced since much of the processing is done in previous cycles.

You can target the tutorial design for an XC4000E or XC9000 device. You can use a Xilinx demonstration board to test the functionality of your design. Make sure your demonstration board and software support your selected device. To determine compatibility, refer to the release notes that came with your software package.

This tutorial uses the following conventions to refer to the various device families:

- XC3000 family—includes XC3000, XC3000A, XC3000L, XC3100, and XC3100A devices

- XC4000 family—includes XC4000, XC4000E, XC4000EX, XC4000L, and XC4000XL devices

- XC5200 family—includes XC5200 devices

- XC9000 family—includes XC9500 and XC9500F devices

# **Software Installation**

## **Required Software**

The following versions of software are required to perform this tutorial:

- Mentor Graphics Version C.2 or later, including Mentor Design Manager, Design Architect, QuickSim, QuickPath, as well as the programs needed to read and write EDIF netlists (ENRead and ENWrite), which require special licensing

- Xilinx/Mentor Graphics Interface Version 2.1i

- Xilinx Development System Version 2.1i

## **Before Beginning the Tutorial**

Before beginning the tutorial, set-up your workstation to use Mentor Graphics and XIlinx Development System software as follows:

1. Verify that your system is properly configured. Consult the release notes that came with your software package for more information.

- 2. Install the following sets of software:

- Xilinx Development System Version 2.1i

- Xilinx/Mentor Graphics Interface Version 2.1i

- Mentor Graphics Version C.2 or later, including Mentor Design Manger, Design Architect, QuickSim, QuickPath, as well as the programs needed to read and write EDIF netlists (ENRead and ENWrite), which require special licensing

- 3. Verify the installation, using the "Configuring Your System" section of the "Getting Started" chapter of the Mentor Graphics Interface Guide, as a guide.

- 4. Add a reference to \$XILINX\_TUTORIAL to your MGC\_LOCATION\_MAP file.

Every symbol and schematic in your design contains references which indicate where design objects reside on your disk or network. The tutorial designs use variables in their reference definitions so they can be easily relocated. All of the tutorial designs use the variable \$XILINX\_TUTORIAL in their path references. \$XILINX\_TUTORIAL must be defined in the file pointed to by \$MGC\_LOCATION\_MAP. For example, the design object seg7dec in the \$XILINX\_TUTORIAL/calc\_sch directory uses the path reference \$XILINX\_TUTORIAL/calc\_sch/seg7dec to define where it is located in the directory structure. If the tutorial directories were copied to the path /home/bclinton/mentor/ xtutorial, the following two lines must be added to the file pointed to by \$MGC\_LOCATION\_MAP:

\$XILINX\_TUTORIAL

/home/bclinton/mentor/xtutorial

If you make a query to determine where the design object "\$XILINX\_TUTORIAL/calc\_sch/stack" is located, the Mentor Graphics tools use this definition to determine that stack is at / home/bclinton/mentor/xtutorial/calc\_sch/stack.

With this definition added to the location map as defined in the "Getting Started" chapter of the Mentor Graphics Interface Guide.Tthe complete location-map file should, at a minimum, look like:

MGC\_LOCATION\_MAP\_1 (empty line)

\$MGC\_GENLIB

(empty line)

\$LCA

(empty line)

\$SIMPRIMS

(empty line)

\$XILINX\_TUTORIAL

/home/bclinton/mentor/xtutorial

Refer to the Mentor Graphics documentation for more information on location maps.

## Installing the Tutorial

If you have not already done so, download the tutorial files from ftp://ftp.xilinx.com/pub/documentation/M2.1i\_tutorials/ men\_tut\_files\_21i.tar.Z. Once they are downloaded un-compress and un-tar the files.

```

uncompress men_tut_files_21i.tar.Z

```

```

tar xvf men_tut_files_21i.tar

```

### **Standard Directory Structure**

When you create a design object in Mentor Graphics, a directory is created in the project directory with the same name as the design object. This directory contains a schematic directory, symbol files, viewpoint files, and part interfaces. The directory is identified as a design object by the file, design\_name.mgc\_component.attr, that resides at the same level as the directory which has the name. For example, if you create a schematic named calc, a calc directory is created, and at the same level the file, calc.mgc\_component.attr, is created. The calc directory contains all the files that describe calc.

**Note:** In this tutorial, file names and directory names are in lower case and the design example is referred to as Calc.

### **Tutorial Directory and Files**

You will complete the Calc design in this tutorial. During the tutorial installation, the /tutorial directory is created; design object directories are created; and the tutorial files needed to complete the design are copied to the calc\_sch directory. Some of the files you need to complete the tutorial design are not copied, because you create these

files in the tutorial. However, solutions directories with all input and output files are provided. They are located in the /tutorial directory and are listed in the following table.

| Directory | Description                                        |

|-----------|----------------------------------------------------|

| calc_sch  | Schematic (Design Architect) tutorial directory    |

| calc_4ke  | Schematic solution directory for XC4003E-PC84      |

| calc_9k   | Schematic solution directory for XC95108-PC84      |

| calc_sot  | Schematic-on-top tutorial directory (uses XC4003E) |

Table 10-1

Tutorial Design Directories

The solution directories contain the design files for the completed tutorial, including schematics, intermediate files, and the bitstream file. Different intermediate files are created for different device families. Do not overwrite any files in the solutions directories.

The calc\_sch directory contains the incomplete copy of the tutorial design. The installation program copies a few intermediate files to the calc\_sch tutorial directory, and you create the remaining files when you perform the tutorial. As described in a later step, you copy the calc\_sch directory to another area and perform the tutorial in this new area. The following table lists and describes the directories and files in the calc\_4ke solution directory.

| Directory or File<br>Name | Description                                     |

|---------------------------|-------------------------------------------------|

| calc                      | Top-level design directory                      |

| control                   | Design directory for control module             |

| statmach                  | Design directory for state controller module    |

| alu                       | Design directory for ALU module                 |

| muxblk2                   | Design component for arithmetic function in ALU |

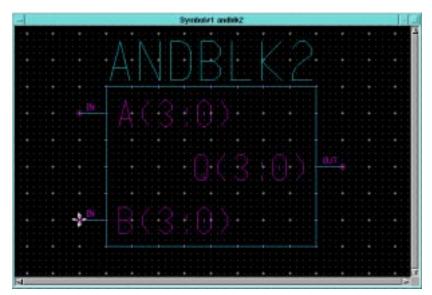

| andblk2                   | Design component for arithmetic function in ALU |

| clockgen                  | System-clock generator                          |

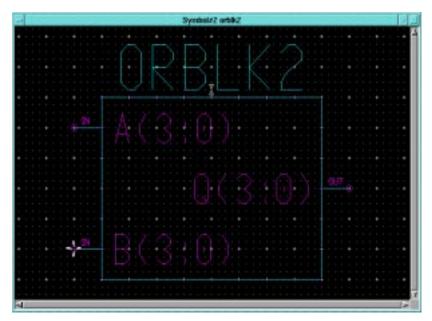

| orblk2                    | Design component for arithmetic function in ALU |

Table 10-2

Tutorial Directories/Files in the Calc\_4ke Directory

| Directory or File<br>Name | Description                                                   |

|---------------------------|---------------------------------------------------------------|

| xorblk2                   | Design component for arithmetic function in ALU               |

| muxblk5                   | Design component for multiplexer arithmetic outputs in ALU    |

| muxlbk2a                  | Design component for multiplexer operator function in control |

| stack                     | Design component for stack                                    |

| seg7dec                   | Design component for 7-segment decoder                        |

| debounce                  | Design component for debounce circuit                         |

| calc.edif                 | EDIF netlist files created by pld_men2edif                    |

| pld_men2edif.log          | pld_men2edif log file                                         |

| calc.ngo                  | Native Generic Object created by EDIF2NGD                     |

| calc_4ke.ucf              | User Constraints File                                         |

| calc.bld                  | Design database report generated by NGDBUILD                  |

| calc.ngd                  | Native Generic Design created by NGDBUILD                     |

| calc.mrp                  | Mapping report generated by MAP                               |

| calc.pcf                  | Physical Constraints File created by MAP                      |

| calc_map.ncd              | Native Circuit Description created by MAP                     |

| calc.par                  | Place-and-Route report generated by PAR                       |

| calc.pad                  | Pinout description generated by PAR                           |

| calc.ncd                  | Routed NCD file created by PAR                                |

| calc.twr                  | Timing report generated by Trace (TRCE)                       |

| calc.bit                  | Configuration bitstream created by BITGEN                     |

| calc.edn                  | Timing-model EDIF netlist created by NGD2EDIF                 |

| calc_lib/calc             | QuickSim timing simulation model created by pld_edif2tim      |

| pld_edif2tim.log          | pld_edif2tim log file                                         |

Table 10-2

Tutorial Directories/Files in the Calc\_4ke Directory

In addition to the files listed above, there is a file called *filename*.mgc\_component.attr associated with each design component directory. This file identifies the corresponding directory as a Mentor Graphics design component.

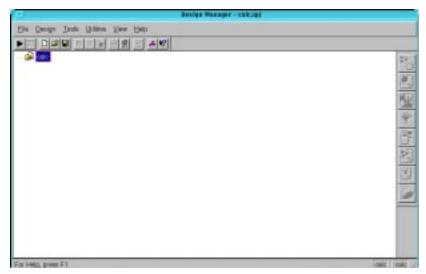

# Starting the Design Manager

To start the Design Manager configured for Xilinx designs, type the following at the operating system command line:

#### pld\_dmgr

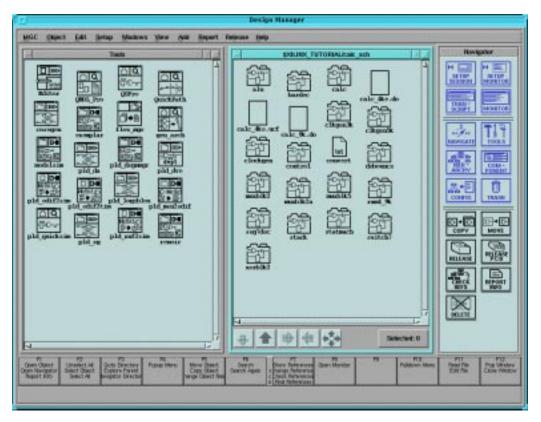

The Design Manager Window appears as shown in the following figure.

Figure 10-1 Mentor Design Manager Window

The Design Manager window contains the following three subwindows:

- Tools Window

- Navigator Window

- Command Palette

Each sub-window is described below.

Mentor Graphics windows conform to Motif standards. You should know how to move, close, and minimize (or iconize) the Motif windows. When multiple windows are open, the active window has a blue border and inactive windows have a grey-brown border. For more information on Design Manager operation, refer to the Mentor Graphics documentation.

### **Tools Window**

The Tools window on the left contains icons representing all the Mentor Graphics and Xilinx applications you need to execute the steps in the tutorial. A description of these programs is given in the "Features" section of the "Introduction" chapter.

### **Navigator Window**

Use the Navigator window to move around the directory hierarchy and select files, folders, and other types of design objects.

The Navigator has five buttons located at the bottom of the window, three of which are most used. The two buttons on the left have up and down arrows on them. Use these buttons to move up and down the directory hierarchy. To move down the hierarchy with the down arrow, you must first select the desired folder in the Navigator. The rightmost button has four arrows on it, one pointing in each direction. When you select this button, a dialog box appears and you can type in the path to the directory you want to display in the Navigator window. Using this button is sometimes quicker and easier than using the up and down arrows.

## **Command Palette**

Use the Command Palette to access the most commonly used Design Manager menu items.

# **Copying the Tutorial Files**

Mentor Graphics design objects contain absolute directory path references. Since many of these paths are self-referencing, using the cp or mv command in Unix to copy or move these design objects to new directories can break those references. The Mentor Graphics Design Architect allows design objects to be copied or moved across directories by adjusting path references within each design object as it is relocated.

To demonstrate the Copy operation in Design Manager, perform the following steps:

- 1. In the Navigator window, move to the directory where the tutorial files were installed.

- 2. Select the calc\_sch directory.

- 3. To see the references in this design, choose Right Mouse Button  $\rightarrow$  Report  $\rightarrow$  Show References  $\rightarrow$  For Design.

A List of Unique References underneath the calc\_sot directory is displayed. An example reference item might be:

\$XILINX\_TUTORIAL/calc\_sot/alu/alu:mgc\_symbol[6]

This indicates that an ALU symbol (version 6 under Mentor Graphics' versioning system) is referenced by the path \$XILINX\_TUTORIAL/calc\_sot/alu/alu.

All references in the design should contain either \$LCA or \$XILINX\_TUTORIAL.

- 4. Close the List of Unique References window.

- 5. With the calc\_sch directory selected in the Navigator window, choose Right Mouse Button  $\rightarrow$  Edit  $\rightarrow$  Copy.

A dialog box appears.

- 6. In the dialog box, type the directory path where you want the working copy of the tutorial files copied. For example, if you want to copy the files to /home/dum/tutor/mentor, enter / home/dum/tutor/mentor/calc\_sch. Click OK.

- 7. Use the Navigator to change directories to the location of the working copy of calc\_sch. In the example above, you would click

the "four-arrow" button at the bottom of the Navigator window, then type /home/dum/tutor/mentor in the dialog box.

- 8. Select the calc\_sch directory.

- 9. As before, choose Right Mouse Button  $\rightarrow$  Report  $\rightarrow$  Show References  $\rightarrow$  For Design. The example reference above with the ALU symbol appears:

/home/dum/tutor/mentor/calc\_sch/alu/alu:mgc\_symbol[6]

- 10. Close the List of Unique References window.

- 11. Modify your MGC\_LOCATION\_MAP file so that the \$XILINX\_TUTORIAL variable points to the directory where the copy of calc\_sch is located. In the example above, change the \$XILINX\_TUTORIAL section of the file so that it reads:

\$XILINX\_TUTORIAL

/home/dum/tutor/mentor

- 12. Read the newly modified location map into Design Architect by selecting MGC  $\rightarrow$  Location Map  $\rightarrow$  Read Map from the menu bar.

- 13. In the dialog box, type \$MGC\_LOCATION\_MAP, then click OK.

The \$XILINX\_TUTORIAL soft name now points to the new tutorial area. However, references in the calc\_sch directory use / home/dum/tutor/mentor instead of its new equivalent, \$XILINX\_TUTORIAL. While this is legal, it is best in Mentor to use soft names wherever possible.

- 14. To convert the hard name back into a soft name, select the calc\_sch directory and choose Right Mouse Button  $\rightarrow$  Edit  $\rightarrow$  Change  $\rightarrow$  References.

- 15. In the Change References dialog box, enter for From: /home/ dum/tutor/mentor (or whatever directory is applicable to your case). For To, enter \$XILINX\_TUTORIAL.

| t References               |

|----------------------------|

| Reference(s)               |

| To NX_TUTORIAU             |

| То                         |

|                            |

| Lock Source Object(s)      |

| 🔶 Yes                      |

| 🔶 No                       |

| Change pattern occurrences |

| \land First Only           |

| 🔶 Every                    |

| t Cancel                   |

|                            |

#### Figure 10-2 Change References Dialog Box

16. Click or.

The Change References process begins.

17. After the process is finished, you can do another Show References operation to verify that all references have been changed properly.

**Note:** You can copy or move a design object without rewriting path references by selecting Options  $\rightarrow$  Convert References? No from the Copy or Move dialog box.

# **Starting Design Architect**

To open the Calc design in Design Architect, perform the following steps:

1. Select  $\texttt{MGC} \to \texttt{Location} \ \texttt{Map} \to \texttt{Set}$  Working Directory from the menu bar.

A small dialog box appears at the bottom of the screen.

2. Type **\$XILINX\_TUTORIAL/calc\_sch** in the Directory field of the dialog box, then select **OK** or press return.

This sets the working directory to the directory where you work on the tutorial.

- 3. Select the \$XILINX\_TUTORIAL/calc\_sch/calc design object in the Navigator window.

- 4. Select Right Mouse Button  $\rightarrow \texttt{Open} \rightarrow \texttt{pld}\_\texttt{da}$ .

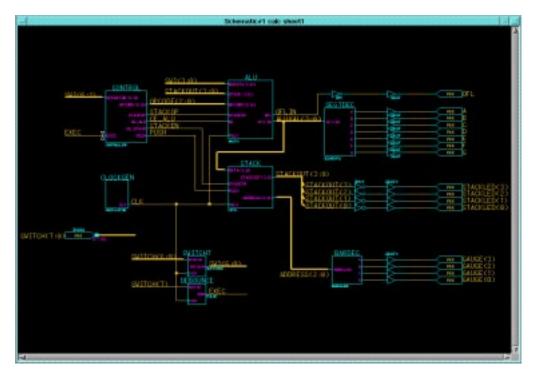

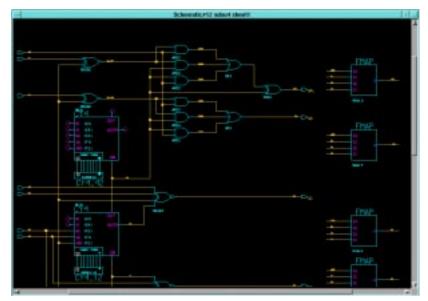

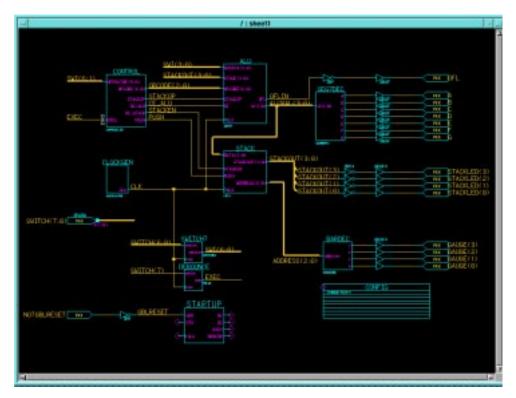

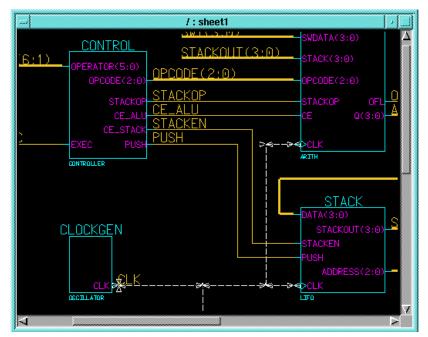

The Design Architect window appears and displays the Calc design as shown in the figure below.

5. Resize the Design Architect window to cover the entire screen.

Figure 10-3 Top-Level Schematic for Calc

## Using the Mouse in Design Architect

#### Left Mouse Button

Use this button to select or de-select objects on a sheet. A selected object has a white dashed outline. Hold down this button and drag the mouse to select multiple objects.

### Middle Mouse Button (Strokes)

Use the middle mouse button to perform actions known as strokes. You can use strokes as shortcuts to perform common tasks. Perform a stroke by pressing and holding the middle mouse button while moving the mouse to draw a line with a specific shape. Design Architect converts the shape you draw to a number string to determine which command to execute. The number is determined as shown in the following figure:

| - — -<br>1 | 2 | - <b>*</b> |       |

|------------|---|------------|-------|

| 4          | 5 | 6          |       |

| 7,★        | 8 | 9 🖊        | X7734 |

#### Figure 10-4 Using Strokes, Example of "Z" stroke (1235789)

For example, a "Z" stroke represents the number 1235789. To determine the commands that the strokes represent, select  $\texttt{Help} \rightarrow \texttt{On}$ **Strokes** from the menu bar at the top of the screen. You can also hold down the middle mouse button and draw the shape of a question mark "?" to display the stroke help screen. When applicable, this tutorial uses strokes and describes them using the numbering system shown in the "Using Strokes, Example of "Z" stroke (1235789)" figure.

### **Right Mouse Button**

You can use the right mouse button to display different menus depending on the object(s) selected on the schematic sheet. For

example, if a net is selected when you press the right mouse button, the Net menu appears. You can access other menus, regardless of what is selected, by using the "Other Menus" selection that appears at the top of each menu.

## **Using the Function Keys**

You can use the keyboard function keys to execute many Design Architect commands. The boxes at the bottom of the Design Architect window each contain up to four commands which you execute as follows:

- To execute the top command, press the associated Function key.

- To execute the middle command, press the associated Function key while holding down the Shift key.

- To execute the third command, press the associated Function key while holding down the Control key.

- To execute the bottom command, press the associated Function key while holding down the Alternate key.

### Selecting Commands from the Menu Bar

Use the left mouse button to select commands from the menu bar at the top of the screen.

### **Selecting Commands from the Palette**

Use the left mouse button to select commands from the Command Palette at the right side of the screen. The set of red buttons at the top of the palette change the commands that are available in the palette. The commands displayed in the palette vary depending on what type of window is active in Design Architect. For example, if a symbol editor window is active, commands such as Add Pin, Draw Rectangle, and other commands associated with creating symbols are available in the palette. If there are no windows open in Design Architect, commands such as OPEN SHEET or OPEN SYMBOL are available.

You may need to scroll the palette to access some of the commands by moving the cursor into the palette and using the PageUp and Page-Down keys. You can also select Right Mouse Button  $\rightarrow$  Show Scroll Bars to display scroll bars.

### **Entering Commands from the Keyboard**

You can type commands anywhere in the Design Architect window. A dialog box appears at the cursor location to capture the command text. For example, you can open a schematic sheet by typing **open sheet** in the Design Architect window.

## **Cancelling Commands**

When you select a command, it is displayed in either a small rectangular box in the lower-left area of the screen, or in a larger dialog box. In either case, you can cancel commands by selecting the cancel button in the box or by pressing the escape key.

## **Repeating Menu Commands**

You can repeat commands that were executed by using either the menu bar or the menus accessed through the right mouse button by holding down the control key, moving the cursor to the appropriate area, and pressing the right mouse button. For example, if Right Mouse Button  $\rightarrow$  Properties  $\rightarrow$  Add was the last command sequence performed, you can repeat this sequence by holding down the control key and pressing the right mouse button with the cursor in the window where the command was last executed. You can also perform this function with the stroke 12369, which looks like an upside-down "L".

### Manipulating the Screen

To zoom in on a specific area of the screen, hold down the F8 key and move the mouse to create a box around the area you want to zoom on. To view the entire schematic, hold down the shift key and press F8. You can also perform these commands with the strokes 159 and 951, respectively. You can also zoom the schematic in or out with the menu bar commands  $\forall iew \rightarrow \texttt{Zoom}$  In and  $\forall iew \rightarrow \texttt{Zoom}$  Out or the strokes 357 and 753.

# Targeting the Design for the XC9000 or XCR Family

The incomplete calc\_sch design is configured for an XC4003E-PC84 part. If you want to target a demonstration board with this device, go to the "Completing the Calc Design" section. If you are targeting the

tutorial design for an XC95108-PC84 (no demonstration board available) or other device family, you must convert the design to reference the XC9000 library instead of the XC4000E library.

The Xilinx CoolRunner (XCR) series can be targeted by using the XC9000 library. The XCR series currently uses XPLA Workstation for implementing designs on the workstation. Xilinx Design Manager does not support XCR designs.

With three exceptions, the calc design can target the XCR as defined in this tutorial. XPLA Workstation cannot compile designs which use LogiBLOX. The config cell is not supported. Timing simulation uses ModelSim rather than QuickSim. The tutorial entitled Workstation Flow for Xilinx CoolRunner CPLDs provides steps to implement and do a timing simulation of the calc design.

The procedure provided below allows you to change every Xilinx component in the Calc design from the XC4000E library to the XC9000 library. Since the designs were created using the Unified Libraries, the parts in the XC4000E and XC9000 libraries have identical footprints and pinouts. This allows you to easily retarget designs to a different device family, provided only library parts common to the two families are used. You must manually replace any library parts that are not common to both families. This example shows a situation where this may happen.

**Note:** Although an XC4000E-to-XC9000 conversion is shown here, this procedure may be used to retarget from any family to any other family.

To retarget the Calc design to the XC9000 or XCR family:

- 1. Close the Calc schematic window by selecting **Close** from the window's control menu. This is the menu accessed by clicking on the button in the upper left-hand corner of the window.

- 2. In the gray desktop area, choose Right Mouse Button  $\rightarrow$  Convert Design.

- 3. A dialog box appears as shown in the figure below. Fill in the fields as shown and click **OK**.

| CONVERT DE<br>Select a group of designs from a list            | ESIGN TO NEW TECHNOLOGY                 |

|----------------------------------------------------------------|-----------------------------------------|

| Enter top level Design name: 331L<br>Schematic name: schematic | Verbose mode switch Check & Save switch |

| Conv                                                           | vert Schematic sheets                   |

| From Technology: xc4000e                                       | e To Technology: xc9000                 |

| Log file name: log_fie                                         | Beep at ignored instances               |

| OK                                                             | Reset Cancel                            |

#### Figure 10-5 Convert Design Dialog Box

Convert Design begins by displaying a Hierarchy Window as it is taking account of the design hierarchy. After this, the Calc schematic and all lower-level design schematics are displayed while Design Architect is retargeting design components.

- 4. After this process is completed, perform the following for each schematic:

- a) Select  $Check \rightarrow Sheet$  from the menu bar. A window appears containing the results of the design rule check.

- b) After reviewing the contents of this window, close it and reselect the schematic window.

- c) Select  $\texttt{File} \rightarrow \texttt{Save}$  from the menu bar to save the schematic.

- d) Close the schematic window and repeat the process for the next schematic.

**Note:** Keep the top-level Calc design open, since you need it in the next section. You can also save yourself the step of checking and saving each design sheet by setting the Check & Save switch to Yes in the Convert Design dialog box.

**Warning:** Although turning the Check & Save switch on makes the Convert Design process more automatic, it is more dangerous since it prevents you from inspecting a converted design before saving it.

Use this setting with caution, and turn it on only when you are certain you wish to overwrite your original design.

# **Completing the Calc Design**

To complete the tutorial design, you need to add a few design objects to the Calc schematic using Design Architect.

If you need to stop the tutorial at any time, be sure to save your work as follows:

1. Select  $Check \rightarrow Sheet$  from the menu bar.

A window appears containing the results of the design rule check.

2. After reviewing the contents of this window, close it and reselect the schematic window.

Warning: It is important to check your design first before saving it.

- 3. Select File  $\rightarrow$  save from the menu bar to save the design.

- 4. Before proceeding to the next part of this tutorial, close (quit) the Calc schematic window.

- 5. If a dialog box appears asking if you want to save any changes, choose **NO**.

## **Design Description**

The top-level schematic of the Calc tutorial design has been created for you. Each of the blocks in the schematic, such as CONTROL or ALU, is linked to a second-level module that describes its logic. Additionally, any second-level module can contain another block that references a third-level drawing, and so on. This organization is known as a hierarchical structure.

In this tutorial, you add three symbols to the ALU block schematic to complete it. First, you create the ANDBLK2 and ORBLK2 symbols and their underlying schematics and then add them to the schematic. Additionally, you add the FD4RE symbol from the Unified Libraries to the ALU block. After the ALU block is finished, you add the STARTUP block to the top-level Calc schematic to tie the device's global reset network to a device pin. To complete design entry, you add a CONFIG block, which lists a set of instructions that dictate how the core tools should process the design.

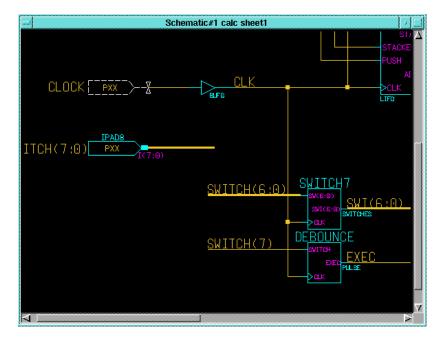

The Calc design is a four-bit processor with a stack. The processor performs functions between an internal register and either the top of the stack or data input from external switches. The results of the various operations are stored in the register and displayed in hexadecimal on a seven-segment display. The top value in the stack is displayed in binary on a bar LED. A count of the items in the stack is displayed as a "gauge" on another bar LED.

The design consists of the following functional blocks:

- **ALU**—The arithmetic functions of the processor are performed in this block.

- **CONTROL**—The opcodes are decoded into control lines for the stack and ALU in this module.

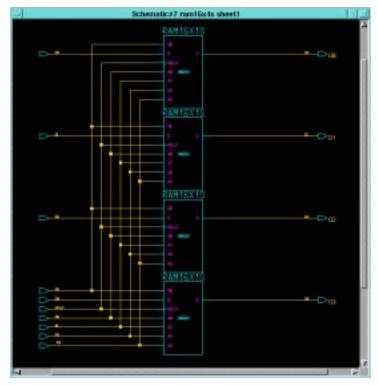

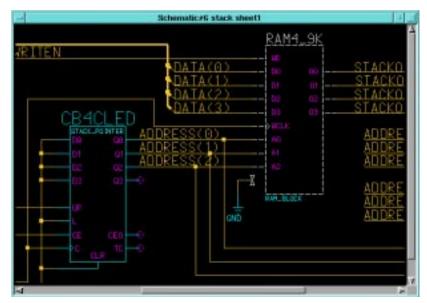

- **STACK**—The stack is a four-nibble storage device. It is implemented using synchronous RAM in the XC4000E design. You can substitute the RAM4\_9K module, which uses flip-flops, in place of the RAM16X4S macro in the STACK schematic to implement the stack in an XC9000 or other non-XC4000E device.

**Note:** If RAM4\_9K is used in a non-XC9000 device, it must be retargeted using Convert Design.

- **DEBOUNCE**—This circuit debounces the "execute" switch, providing a one-shot output.

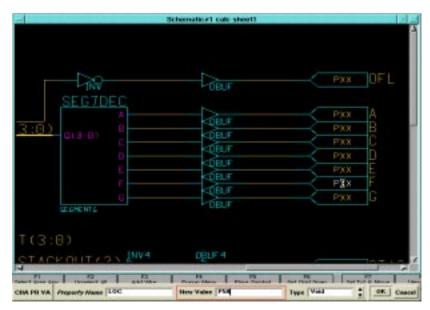

- **SEG7DEC**—This block decodes the output of the ALU for display on the 7-segment decoder.

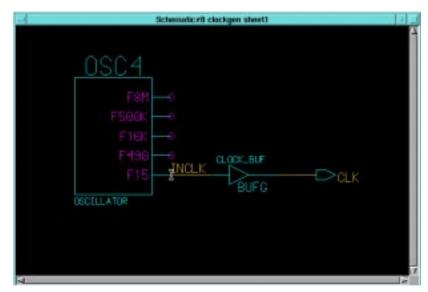

- **CLOCKGEN**—This block uses an internal oscillator circuit in XC4000E devices to generate the clock signal. In XC9000 designs, it is replaced by an input pad and a clock buffer.

**Note:** The XC3000 and XC5200 FPGA families also have on-board oscillators. See the CLKGEN3K and CLKGEN5K components included in the calc\_sch directory to see how the oscillators in these families are used.

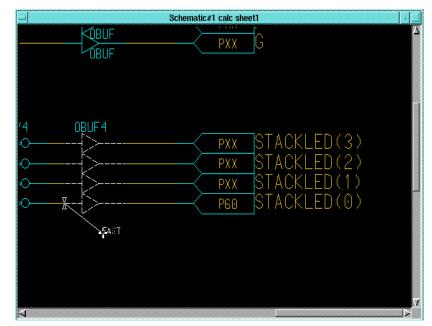

- **BARDEC**—This block shows how many items are on the stack on a "gauge" of four LEDs.

- **SWITCH7**—This block is a user-defined module consisting of seven input flip-flops used to latch the switch data.

## Creating the ANDBLK2 Symbol

#### **Opening a Symbol Window**

- 1. Use the left mouse button to select Open Symbol in the Command Palette.

- 2. Type **\$XILINX\_TUTORIAL/calc\_sch/andblk2** in the Component Name box.

- 3. Select OK.

A symbol editor window appears.

#### **Creating the Symbol Outline**

- 1. Zoom in until the grid space markers, represented by small crosses, are visible in the symbol window.

- 2. Select **ADD RECTANGLE** from the palette.

- 3. Position the cursor in the upper left corner of the symbol window and press the left mouse button.

- 4. While holding down the left mouse button, move the cursor diagonally to the opposite corner of the symbol window to draw a rectangle that is six grid squares high by eight grid squares wide. Be sure to measure using the grid marks, and not the small dots that define fractions of grid spacing.

### Adding Pins to the ANDBLK2 Symbol

1. Select Add Pin from the palette.

The dialog box in the following figure appears.

2. Fill in the Dialog box exactly as shown in the following figure and then select OK.

| Add Pin(s) :                                     |

|--------------------------------------------------|

| Name Height : 75% 50% 1.0 on 1.0 Pin Grid        |

| Name Placement : Manual 🔷 Name 🗛 Name            |

| PinType : IN OUT IXO omit Pin Placement : 어소 文 H |

| Pin Name(s) :                                    |

| A(3:0)                                           |

| (B(3:0))                                         |

| OK Reset Cancel                                  |

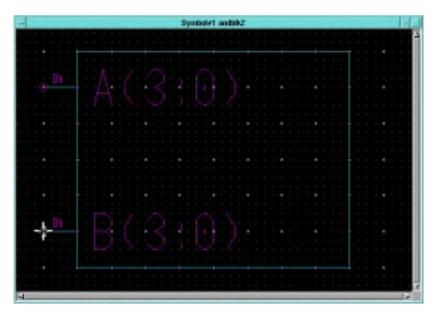

#### Figure 10-6 Add Pin(s) Dialog Box for A(3:0) and B(3:0)

A small crosshair appears under the cursor, and a rectangular box appears stating that the first pin, A(3:0), is to be placed.

3. Place pin B(3:0) as shown in the figure below by moving the cursor to the position where the diamond appears in the figure (one grid space to the left of the rectangle) and pressing the left mouse button. Small purple diamonds indicate pins.

If you make a mistake before placing a pin, press the escape key to cancel the command, then repeat the above steps. If you make a mistake after placing a pin, press the F2 key to unselect everything. Select the pin (diamond) and the line next to it and press and hold CTRL-F2 to execute a move command. Move the pin to the correct position and release the keys.

Figure 10-7 Adding Pins A(3:0) and B(3:0)

4. Select Add Pin from the palette and fill in the dialog box as shown in the following figure, then select OK. Be sure to set the name height to 1.0.

| Add Pin(s):                                                                         |

|-------------------------------------------------------------------------------------|

| Name Height : 75% 50% 1.0 on 1.0 Pin Grid                                           |

| Name Placement : Manual 💠 Name 🗛 Name                                               |

| PinType : IN OUT IXO omit Pin Placement : 어오 장 (>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> |

| Pin Name(s) :                                                                       |

| Q(3:0)                                                                              |

|                                                                                     |

| OK Reset Cancel                                                                     |

#### Figure 10-8 Add Pin(s) Dialog Box for Q(3:0)

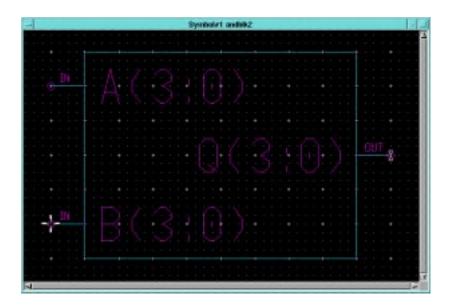

- 5. Place the pin Q(3:0) as shown in the figure below.

- 6. To adjust the positioning of the pin names, move the mouse over the text, press and hold the F7 function, and move the mouse to reposition the text. Release the F7 key to place the text at the new location.

Figure 10-9 Adding Pin Q(3:0)

### **Adding Text**

You can add comment text to a symbol to make it more easily identifiable on a schematic, or to annotate it without modifying its function. To add text to the symbol, perform the following steps:

- 1. Select the red **TEXT** button at the top of the palette to display the text editing icons.

- 2. Choose ADD TEXT from the palette.

A small rectangular dialog box appears in the lower left portion of the window.

- 3. Type **ANDBLK2** in the Text field of the dialog box, then press return or select **OK**.

- 4. Move the cursor into the symbol editor window and place the text directly above the symbol body by moving the mouse to the proper position and pressing the left mouse button.

If you make a mistake while typing the text and the text has already been placed, move the mouse over the text and press the F7 key while holding down the shift key. A small dialog box appears at the bottom of the screen containing the selected text. Modify the text in the dialog box. Select OK to change the text on the symbol. You can use this method to modify any text on the symbol, such as pin names.

### **Modifying Text Size**

To modify symbol text size, perform the following steps:

- 1. Press the F2 key to unselect everything.

- 2. Use the left mouse button to select the text, **ANDBLK2**, at the top of the symbol.

- 3. Select Right Mouse Button  $\rightarrow$  Change Height  $\rightarrow$  1.5 X pin spacing.

- 4. Place the cursor over the text and press and hold the F7 key.

- 5. While still holding down the F7 key, move the text so that it is centered above the symbol body, as shown in the following figure.

Figure 10-10 Completed ANDBLK2 Symbol

#### Saving the ANDBLK2 Symbol

To save the ANDBLK2 symbol, perform the following:

1. From the menu bar, select  $Check \rightarrow With Defaults$ .

A text window appears containing the results of the design rule check.

2. Check to see that the information displayed is the same as that in the following figure. If you do not have the same output, correct the symbol to eliminate the differences and then check the symbol again.

```

Check#2 andblk2:Symbol 3 Check Symbol "andblk2/andblk2"

Check Symbol "andblk2/andblk2"

Check Body ------ 0 errors 0 warnings (MGC-required)

Check Interface -- 0 errors 0 warnings (MGC-required)

Check Special ---- 0 errors 0 warnings (MGC-required)

"andblk2/andblk2" passed check : 0 Errors, 0 Warnings

```

#### Figure 10-11 Output from Check

- 3. Close the text window by selecting **Close** from the menu that appears when the left mouse button is pressed in the box in the upper left hand corner of the text window.

- 4. Select File  $\rightarrow$  Save Symbol from the menu bar to save the symbol.

### **Creating the ORBLK2 Symbol**

The next step is to create the symbol for ORBLK2, as shown in the following figure. Since ORBLK2 is similar to ANDBLK2, use the ANDBLK2 symbol and modify the text as described below.

- 1. Move the cursor above the ANDBLK2 text.

- 2. Press the F7 key while holding down the shift key to select the Change Text Value command.

3. In the small dialog box that appears in the lower left corner, type ORBLK2 in the New Text field, then select OK.

Figure 10-12 Completed ORBLK2 Symbol

- 4. If necessary, use the cursor and F7 key to move and center the text, as described earlier.

- 5. From the menu bar, select  $Check \rightarrow With Defaults$ .

A text window appears containing the results of the design rule check. Since you are modifying the ANDBLK2 symbol, the text still refers to ANDBLK2.

- 6. If any errors are reported in the Check text window, correct them on the symbol and check the schematic again. Otherwise, close the text window.

- 7. To save the symbol as ORBLK2, select File  $\rightarrow$  Save Symbol AS.

A dialog box appears.

**Warning:** It is important that you select the Save Symbol As command instead of Save to prevent overwriting the original ANDBLK2 file.

- 8. Enter \$XILINX\_TUTORIAL/calc\_sch/orblk2 in the component name field and enter orblk2 in the interface name field.

- 9. Select **ok** to execute the command.

This saves the symbol as ORBLK2.

10. Close the window containing the symbol.

A dialog box appears prompting you to save the changes to ANDBLK2. Since the symbol for ANDBLK2 was saved prior to modifying it for the ORBLK2 symbol, it is not necessary to save changes to the ANDBLK2 symbol.

11. In the dialog box, select **No**.

### **Creating Schematics for ANDBLK2 Symbol**

You have created symbols for ANDBLK2 and ORBLK2. The next step is to create schematics for these blocks. You can then reference the schematics in a higher-level schematic by placing the symbols.

### **Opening a Schematic Window**

- 1. To open a schematic window, select **OPEN SHEET** from the palette.

- 2. In the dialog box that appears, type **\$XILINX\_TUTORIAL**/ calc\_sch/andblk2 in the Component Name field.

- 3. Select OK.

A blank schematic sheet appears.

#### Adding the First Component to a Schematic

1. From the menu bar, select Libraries  $\rightarrow XILINX$  Libraries.

The Xilinx Libraries menu appears.

2. Select the correct library for the device you are targeting, either XC4000E or XC9000.

If you select the wrong library, use the PageUp key to go to the top of the Library Palette menu and click the left mouse button on the Back option. This moves the library menu back up the hierarchy.

3. Choose **BY TYPE** from the palette.

This option organizes the library parts into categories. The ALL PARTS option displays all the library parts at once. A menu appears similar to that shown in the figure below.

| XACT_XC4000E_E    | Зу_Ту            |  |  |  |  |  |  |  |  |  |  |  |

|-------------------|------------------|--|--|--|--|--|--|--|--|--|--|--|

| MENU ROOT         | r 🛔              |  |  |  |  |  |  |  |  |  |  |  |

| BACK              |                  |  |  |  |  |  |  |  |  |  |  |  |

| Schematic Palette |                  |  |  |  |  |  |  |  |  |  |  |  |

| Set as Default    |                  |  |  |  |  |  |  |  |  |  |  |  |

| ALL PARTS         | $\triangleright$ |  |  |  |  |  |  |  |  |  |  |  |

| XC4000E By Ty     | /pe              |  |  |  |  |  |  |  |  |  |  |  |

| arithmetic        | $\triangleright$ |  |  |  |  |  |  |  |  |  |  |  |

| buffer            | $\triangleright$ |  |  |  |  |  |  |  |  |  |  |  |

| carry_logic       |                  |  |  |  |  |  |  |  |  |  |  |  |

| comparator        | $\triangleright$ |  |  |  |  |  |  |  |  |  |  |  |

| counter           | $\triangleright$ |  |  |  |  |  |  |  |  |  |  |  |

| data_register     |                  |  |  |  |  |  |  |  |  |  |  |  |

| decoder           | $\triangleright$ |  |  |  |  |  |  |  |  |  |  |  |

| edge_decoder      | $\triangleright$ |  |  |  |  |  |  |  |  |  |  |  |

| encoder           | $\triangleright$ |  |  |  |  |  |  |  |  |  |  |  |

| flip_flop         |                  |  |  |  |  |  |  |  |  |  |  |  |

| general           |                  |  |  |  |  |  |  |  |  |  |  |  |

| io                |                  |  |  |  |  |  |  |  |  |  |  |  |

| io_flip_flop      | $\triangleright$ |  |  |  |  |  |  |  |  |  |  |  |

| io_latch          |                  |  |  |  |  |  |  |  |  |  |  |  |

| logic             |                  |  |  |  |  |  |  |  |  |  |  |  |

| map               |                  |  |  |  |  |  |  |  |  |  |  |  |

#### Figure 10-13 XC4000E Library BY TYPE Menu

- 4. To move up and down in the menu, turn on the scroll bars by moving the cursor into the menu window and selecting Right Mouse Button  $\rightarrow$  Show Scroll Bars. You can also move up and down using the PageUp and PageDown keys.

- 5. Click the left mouse button on the Set As Default option. This option allows you to return to this area and view of the library menu by clicking on the Library icon in the Schematic Palette.

- 6. Choose the logic category from the **BY TYPE** menu.

- 7. Select and 2.

- 8. In the small dialog box that appears on the screen, move the cursor into the schematic window.

The outline of a 2-input and gate appears.

9. Move the symbol outline to the location shown in the following figure and then click the left mouse button to place the object.

| 4 |   |   |   |   |   |   |   |   |     | 1.500 | dicist? | 100 | 2 ster | 11 |   |   |   |   |    |   |   |   | 1 |

|---|---|---|---|---|---|---|---|---|-----|-------|---------|-----|--------|----|---|---|---|---|----|---|---|---|---|

|   | + | - | + | + | + | ÷ | + | + | - 4 |       | 4       | -   | ÷      | +  | ÷ | + | + | ÷ | -+ | + | + | + | + |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     | -     |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   | ī |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   | H   |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

|   |   |   |   |   |   |   |   |   |     |       |         |     |        |    |   |   |   |   |    |   |   |   |   |

Figure 10-14 Placing a Component

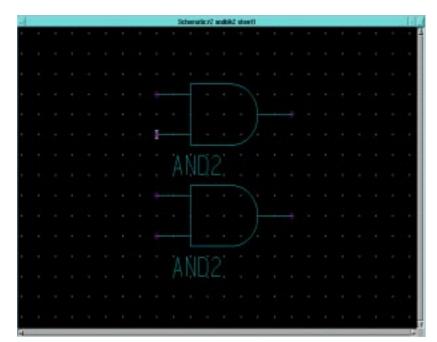

### **Placing Additional Components**

After placing the and2, note that a picture of it appears in the small window in the upper right area of the screen. The last library element selected appears in this window.

- 1. To select another component of the same type, move the mouse inside this window, and click the left mouse button.

- 2. Then move the cursor to the schematic window, position the component, and release the mouse button to place it on the sheet.

- 3. Using this method, select and place a second and2 symbol as shown in the following figure.

Figure 10-15 Placing a Second Component

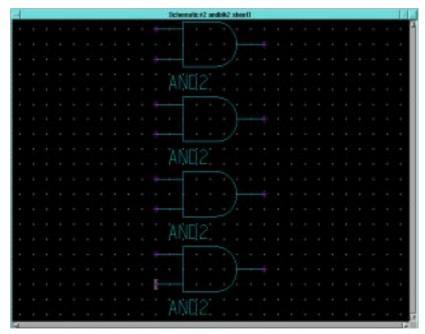

### **Copying a Component**

Use the Copy command to add more components by copying a component that already appears on the schematic.

1. Press the F2 function key to ensure that nothing is selected.

It is important to use the F2 key before selecting objects because objects selected in previous steps are sometimes not deselected.

- 2. Move the mouse above and to the left of the two symbols on the sheet.

- 3. While holding down the left mouse button, move the mouse below and to the right of the two symbols.

A white box appears surrounding the two symbols.

- 4. Release the mouse button to select the objects.

- 5. Select Right Mouse Button  $\rightarrow$  Copy. Alternatively, use stroke 3214789, a stroke in the form of a "C", to select the copy command.

A small dialog box appears at the bottom of the screen.

6. Place the two copied gates above the original two using the left mouse button. If necessary, use the 753 stroke to zoom out.

The dialog box disappears after you place the gates.

7. Press Shift - F8 to view the entire schematic.

The schematic now looks like the following figure.

Figure 10-16 Component Placements for ANDBLK2

### **Moving a Component**

If you make a mistake when placing a component, you can use the menu commands to move the component.

- 1. Use the F2 key to deselect.

- 2. Select the component by clicking on it with the left mouse button.

The component appears highlighted, indicating that it has been selected.

3. Select Right Mouse Button  $\rightarrow$  Move, or use the stroke 74159.

A small dialog box appears.

4. Click the left mouse button to correctly place the component.

The dialog box disappears after the component is placed.

### Adding Buses to a Schematic

Sometimes it is convenient to draw a set of signals as a bus rather than as several separate wires. It is not necessary to physically connect a bus to the nets that make up the bus. There are several schematics in the Calc design that have short bus segments that are not connected to anything. This is done so that a bus pin can be used to represent the bus on the symbol. A bus must exist on the schematic if a bus pin is to be used for a set of signals.

Add buses to the schematic as follows:

1. After pressing the F2 key, select Right Mouse  $\texttt{Button} \rightarrow \texttt{Bus}.$

A small dialog box appears, and a white cross appears under the cursor.

2. Draw a bus by clicking the left mouse button to specify the starting point, moving the mouse to a new position, and then clicking the button again to make a bend in the bus or to connect it to a pin. Terminate the bus is by clicking the mouse button in the same place twice. Add the three buses shown in the figure below. You may want to zoom the schematic view out before performing adding the buses.

If you make a mistake, press the F2 key to deselect everything on the sheet. Then click on the bus segments you want to delete so that they appear highlighted. Press the Delete key and then redraw them correctly.

3. After adding the three buses, press the **Escape** key to exit the bus adding mode.

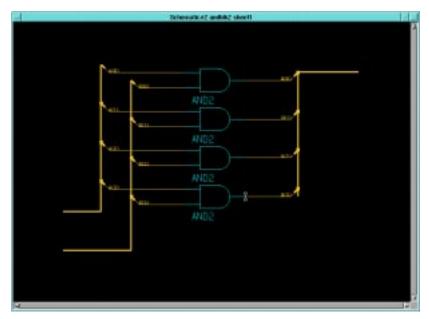

Figure 10-17 ANDBLK2 Schematic with Buses

### Adding Nets to a Schematic

Next, nets must be added to attach the appropriate pins on the gates to the buses. You may want to enlarge the view of the components to make it easier to draw the nets.

- 1. Press the F2 key.

- 2. Select Right Mouse Button  $\rightarrow$  Wire from the ADD menu.

A small dialog box appears, and a white cross appears under the cursor.

**Note:** If the ADD menu does not appear, it may be that something is still selected, resulting in a different menu appearing on the screen. If this happens, press the F2 key and repeat step one.

3. Move the cursor to the top input pin of the top and2 gate, then click the left mouse button.

4. Move the cursor to the left, so that the pointer is laying atop the leftmost bus. (The wire should form a ninety-degree angle with the bus.) Click the left mouse button twice to terminate the wire.

|  |   |     | - 22 | States | MICH? | - | about 1 | 1 |  |      |   |      |  |

|--|---|-----|------|--------|-------|---|---------|---|--|------|---|------|--|

|  |   |     |      |        |       |   |         |   |  |      |   |      |  |

|  |   |     |      |        |       |   |         |   |  |      |   |      |  |

|  |   |     |      |        |       |   |         |   |  |      |   |      |  |

|  | k |     |      |        |       |   |         |   |  |      |   |      |  |

|  |   | 74- |      |        |       |   |         |   |  | - 14 |   |      |  |

|  |   |     |      | 1      |       |   |         |   |  |      |   |      |  |

|  |   |     |      |        |       |   |         |   |  |      |   |      |  |

|  |   |     |      |        |       |   |         |   |  |      |   | NIE  |  |

|  |   |     |      |        |       |   |         |   |  |      | A | INL. |  |

|  |   |     |      |        |       |   |         |   |  |      |   |      |  |

|  |   |     |      |        |       |   |         |   |  |      |   |      |  |

|  |   |     |      |        |       |   |         |   |  |      |   |      |  |

|  |   |     |      |        |       |   |         |   |  |      |   | NIE  |  |

|  |   |     |      |        |       |   |         |   |  |      | A | NL   |  |

Figure 10-18 Connecting a Net

A bus ripper is inserted automatically between the wire and the bus as shown in the "Connecting a Net" figure. A bus ripper defines which bit of the bus is connected to the wire. Automatically inserting bus rippers is referred to as autoripping.

If the bus ripper did not automatically get inserted, make sure that you clicked on the pin first and then on the bus to attach a net between the two. If the net is attached to the bus first, autoripping does not occur. Also, check the Setup menu to make sure that autoripping is turned on. "Set Autoripping Off" should be displayed in the menu to indicate that autoripping is turned on. If "Set Autoripping On" is displayed, select it to turn autoripping on. Also, the \$MGC\_GENLIB environment variable must be set correctly for the autoripping function.

A dialog box as shown in the "Label Bus Dialog Box" figure below appears. This box allows you to label a net which has a bus ripper connected to it. Labeling is the process of identifying a net or a component by assigning a text string to it. It is recommended that you label all nets on the schematic, to simplify debugging and simulation. To specify the bus signals they are related to, all nets that are attached to buses must have a number in parentheses at the end of their names. For example, a net that is bit zero of bus A must be labeled A(0).

| Name Ripped Net                               |  |  |  |  |  |  |  |  |

|-----------------------------------------------|--|--|--|--|--|--|--|--|

| NOTE: The wide net to which you have attached |  |  |  |  |  |  |  |  |

| this wire is unnamed. Please name it          |  |  |  |  |  |  |  |  |

| to ensure correct connectivity.               |  |  |  |  |  |  |  |  |

| Wide Net Name                                 |  |  |  |  |  |  |  |  |

| Ripped Net Name A(0)                          |  |  |  |  |  |  |  |  |

| OK Reset Cancel                               |  |  |  |  |  |  |  |  |

#### Figure 10-19 Label Bus Dialog Box

Fill out the fields as shown in this example, so that this first net is labeled A(0). Note that you can label the bus as well as the net, but you will do this later.

If the dialog did not appear as shown, choose SETUP RIPPER from the palette and make sure that Ripper Mode is set to "Implicit" and that Ripper Query is set to "On". After setting these parameters, select OK, then delete the net and start again from step one.

5. After filling out the dialog box, you are asked to place the net label, or net name, on the schematic. Place the label as shown in the following figure and click the left mouse button.

| 4   |   |   |   |     | 1100 | School | 10102 | -  | sheet | 1  |   |    |   |   |    |      | 11 |

|-----|---|---|---|-----|------|--------|-------|----|-------|----|---|----|---|---|----|------|----|

| e + | ÷ | ٠ | 4 | 4   |      | -      |       | ł. | ł.    | ł. | 4 | ł. | 4 |   |    |      |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   |   |    |      |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   |   |    |      |    |

|     |   | N |   |     |      |        |       |    |       |    |   |    |   |   |    |      |    |

|     |   |   | 1 | (0) |      |        |       |    |       |    |   |    |   |   |    |      |    |

|     |   |   |   |     |      | I      |       |    |       |    |   |    |   |   |    |      |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   |   |    |      |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   |   |    | ni s |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   | A | N  | Ц4   |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   |   |    |      |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   |   |    |      |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   |   |    |      |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   |   | ŃĽ |      |    |

|     |   |   |   |     |      |        |       |    |       |    |   |    |   | H |    | 44   |    |

Figure 10-20 Adding and Placing a Net Name

6. Press the Escape key to exit the wire-adding mode.

#### **Completing the Net Connections**

Add the remaining nets to the schematic as follows:

- 1. Press the F3 key to execute the Add Wire command, or use the downward stroke 258.

- 2. Add the remaining nets as shown in the "ANDBLK2 with All Wires and Buses Connected" figure below.

**Note:** When a wire is properly attached to a symbol pin, the small diamond that specifies the connection point for the pin disappears. If any of the diamonds are still visible, delete the associated net and reattach it.

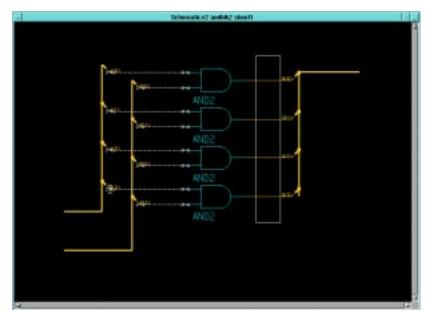

Figure 10-21 ANDBLK2 with All Wires and Buses Connected

#### **Increasing Text Size**

At this point, all nets in the ANDBLK2 schematic have been labeled. However, the text of these labels is quite small compared to the other elements in the schematic.

To make the labels more readable:

1. Select all nets in the design by dragging with the left mouse button over the A(x) and B(x) nets then releasing, then doing the same with the Q(x) nets. In each case, a selection marquis appears as shown in the "Selecting Nets" figure. This is an additive selection; elements selected previously remain selected. Note that the marquis need only touch elements you wish to select; it need not enclose these elements completely.

**Note:** If you accidently select any elements besides the nets (bus rippers, buses, or gates), press F2 to unselect everything, then repeat the selection procedure.

Figure 10-22 Selecting Nets

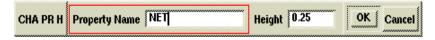

- 2. To change the size of the net labels, choose Right Mouse Button  $\rightarrow$  Properties  $\rightarrow$  Change Text Height  $\rightarrow$  1.0 x Pin Spacing.

- 3. In the Change Property Height dialog box that appears as shown below, type **NET** in the Property Name field as indicated to increase the height of all NET properties on all selected elements.

#### Figure 10-23 Increasing Text Size

All net and bus labels are attached as a property called "NET" with a value equivalent to the net or bus label.

The label sizes are increased as shown in the figure below.

Figure 10-24 Schematic with Larger Net Names

#### **Adding Ports**

You must add port symbols to nets and buses to define the connectivity between a schematic and its associated symbol. For the ANDBLK2 schematic, all three buses need ports. Input signals are given PORTINs and output signals are given PORTOUTS.

Add ports to the schematic as follows:

- If the appropriate Unified library is not displayed in the palette, use the menu bar command Libraries → XILINX Libraries to select it. Select the Unified Libraries and the appropriate library for the part being used.

- 2. If the library is already visible, you may need to choose the **BACK** option from the top of the Library Palette to move up to the general library categories. Continue selecting **BACK** until the **ALL PARTS** and **BY TYPE** selections are displayed.

- 3. Select **BY TYPE**, and then choose the io category.

- 4. Select the portin library part from the menu.

- 5. Place the portin so that the white crosshair is *exactly* above the left end of the upper input bus, on the left side of the window.

- 6. Place another portin at the end of the lower input bus, on the left side of the window.

- 7. Select a portout symbol from the library and place it at the end of the output bus.

- 8. Press **Shift-F8** to view the entire schematic.

The schematic appears as in the following figure.

Figure 10-25 Adding Ports

#### **Labeling Ports**

Normally, you label nets and buses by selecting them, then executing the menu selection Right Mouse Button  $\rightarrow$  Name Nets as shown later in this tutorial. However, the addition of the port symbols to the buses has automatically assigned a default name of "NET" to each bus. This simplifies the process since you can modify the existing names rather than add new ones.

1. Press the F2 key to unselect everything on the schematic sheet.

- 2. Move the cursor so that it sits above the NET label on the output bus.

- 3. Press Shift-F7 to choose the Text Change Value command.

A small dialog box appears.

- 4. In the New Value field, change the text to Q(3:0).

- 5. Press return or choose **OK** in the dialog box.

- 6. Repeat this procedure on the two remaining buses, giving them names as shown in the following figure.

Figure 10-26 Labeling Buses

#### **Saving the Schematic**

The schematic is now complete. Check and save the schematic as follows:

1. Select  $Check \rightarrow Sheet$ .

The text window that appears should not contain any warnings about unnamed or dangling net vertices, since all pins in the schematic should be connected. 2. If these or any other warnings or errors occur, recheck the schematic against the following figure.

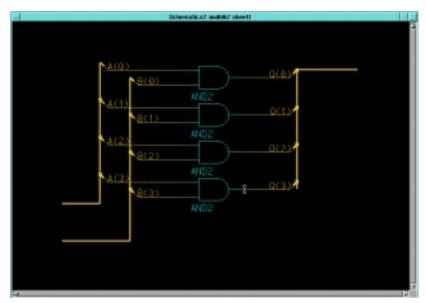

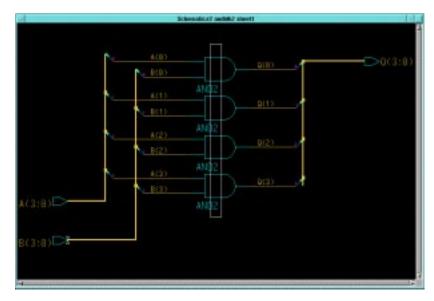

Figure 10-27 Completed ANDBLK2 Schematic

The check sheet window is also linked to the schematic window. Any net, vertex, or instance names can be highlighted in the check sheet window by clicking the left mouse button on it. The corresponding net, vertex, or instance on the schematic is highlighted. This is useful for relating an error message in check sheet to the schematic.

- 3. Once all schematic errors have been corrected, check the design again if necessary, and close the check sheet text window.

- 4. Select  $\mathtt{File} \rightarrow \mathtt{Save}$  Sheet from the menu bar to save the schematic.

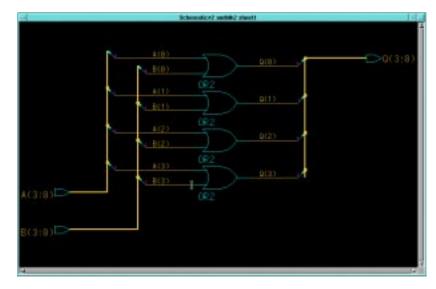

## **Creating Schematics for ORBLK2 Symbol**

The ORBLK2 schematic is similar to the ANDBLK2 schematic. To create schematics for the ORBLK2 symbol, you can use the ANDBLK2 schematic and simply replace the four and2 gates with or2 gates as described in the following procedure.

- 1. Press the **F2** key to unselect everything on the ANDBLK2 schematic.

- 2. Display the BY TYPE library menu and select the logic category.

- 3. Press and hold the left mouse button and move the mouse to create a rectangle to include part of all four and2 gates, as shown in the following figure. It is not necessary to box the entire gate to select it. Do not include any part of the attached nets in the rectangle.

#### Figure 10-28 Selecting Gates

- 4. When the rectangle is positioned correctly, release the left mouse button to select all four and2 gates.

- 5. Select Right Mouse Button  $\rightarrow$  Replace  $\rightarrow$  From Library Menu.

A message appears at the bottom of the screen requesting that you select the replacement library part from the menu.

6. Use the PageUp and PageDown keys to scroll the component list. Select the or2 component.

The four and 2 gates are replaced with or 2 gates. The ORBLK2 schematic is complete.

7. Select  $Check \rightarrow Sheet$  from the menu bar.

The check program refers to the ANDBLK2 schematic, since this was modified to create the ORBLK2 schematic.

- 8. Close the text window containing the results of check sheet.

- 9. Select File  $\rightarrow$  Save Sheet As.

- In the dialog box that appears, type \$XILINX\_TUTORIAL/ calc\_sch/orblk2 in the Component name field and leave all other fields blank.

- 11. Press return to save the schematic.

Figure 10-29 Completed ORBLK2 Schematic

### **Editing the ALU Schematic**

So far you have created symbols for ANDBLK2 and ORBLK2. You have also created underlying schematics for these symbols. The next step is to place the symbols in the ALU block schematic.

1. Close the only open window, which is the modified ANDBLK2 schematic, using the button in the upper left corner of the window.

- 2. In the dialog box that appears asking whether to save the changes to the schematic, select **No**, since the ANDBLK2 schematic was saved earlier, but then modified for use as the ORBLK2 schematic.

- 3. Choose **OPEN SHEET** from the Session Palette.

- 4. Press the Navigator button to open a Navigator window.

- 5. If necessary, change directories to the \$XILINX\_TUTORIAL/ calc\_sch directory using the up arrow to move up one directory level and double-clicking folders to push into them. Then, select the Calc design, which is represented by a folder with a "c" on it and with the name "calc" next to it. The "c" specifies that it is a component, and not just a directory.

- 6. Press return or select OK from the Navigator window.

The Component Name field of the OPEN SHEET dialog box is automatically back-filled with " $XILINX_TUTORIAL/calc_sch/calc$ ".

- 7. Press return or select OK from the OPEN SHEET dialog box. The top level Calc design appears in a window. Press Shift - F8 to view the entire schematic, if necessary.

- 8. Press F2 key to unselect everything on the schematic.

- 9. Select the **ALU** symbol.

- 10. The additions you need to make are all in the ALU schematic, so choose  $\texttt{File} \rightarrow \texttt{Open}$  Down from the menu bar using the left mouse button.

The Open Down dialog box appears as shown in the following figure.

|                     | -               |              |         |

|---------------------|-----------------|--------------|---------|

| Symbol<br>schematic | : alu<br>sheeti | A            |         |

| Fuioting            |                 |              | Version |

| Existing            | New Sneet Ne    |              |         |

| Open as :           |                 |              |         |

| Editable            | Read Onl        | y Show Hiera | chy     |

| pecific Star        | tup : No Yes    |              |         |

|                     |                 |              |         |

Figure 10-30 Open Down Dialog Box

- 11. In the Open Down dialog box, specify whether to modify the symbol or the schematic for ALU by selecting schematic sheet1, with the left mouse button. The selected line appears highlighted in the dialog box.

- 12. Press return or select OK.

A second schematic window appears containing the ALU schematic.

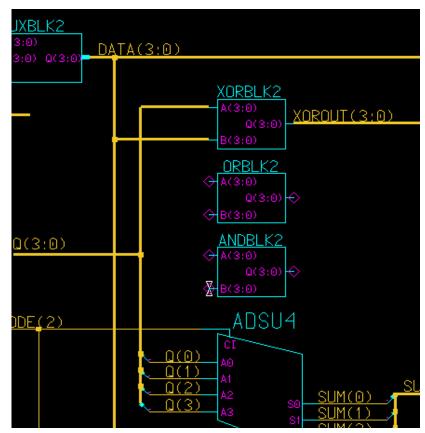

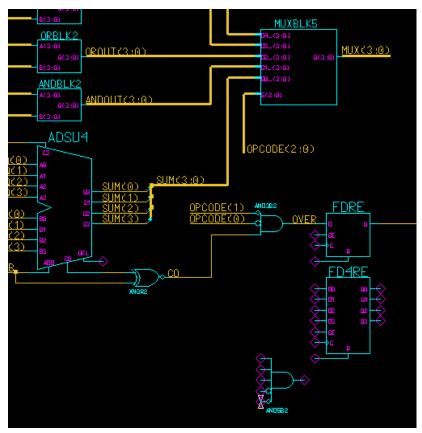

### **Placing User-Created Components**

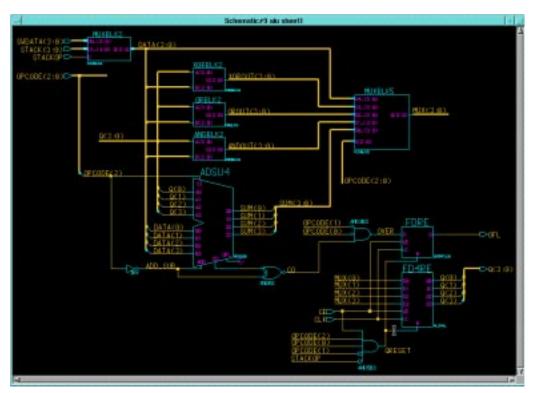

You can now place the ANDBLK2 and ORBLK2 symbols on the schematic as shown in the figure below. You place the symbols using the same procedure you used to place the and2 gate from the Xilinx libraries when you created the ANDBLK2 schematic.

- 1. Use the **F8** key to zoom into the empty area near the center of the schematic, between the XORBLK2 and ADSU4 symbols.

- 2. Press the F2 key to ensure that nothing is selected.

3. Choose Right Mouse  $\texttt{Button} \to \texttt{Instance} \to \texttt{Symbol}$  by Path.

In the Add Instance dialog box that appears, use the Navigator button to select the \$XILINX\_TUTORIAL/calc\_sch/andblk2 component, or type the name in the Component Name field.

- 4. Press return or select OK to execute the command.

- 5. Move the cursor to the correct location as shown in the following figure.

Figure 10-31 Adding ANDBLK2 and ORBLK2 to ALU Schematic

- 6. Press the left mouse button to place the component.

- 7. Follow the same procedure to add the ORBLK2 symbol. Refer to the ALU schematic in the figure above for proper placement.

8. If you make a mistake when placing a component, select it (after pressing F2 key) and use Right Mouse Button  $\rightarrow$  Move to reposition it.

### **Placing Library Components**

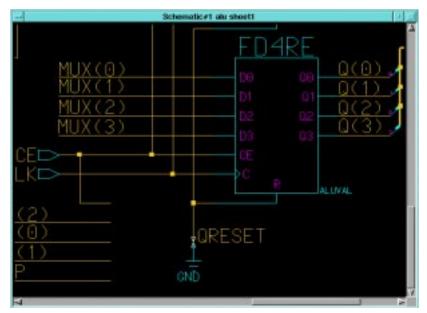

The next step in the tutorial is to add the fd4re and and5b2 components to the ALU schematic. The fd4re component is available in the Xilinx Unified Libraries and consists of four flip-flops with a clock enable. The and5b2 component is a five-input AND gate with two inputs inverted ("bubbled," hence the "b").

**Note:** These components are available in all libraries, including those for the XC4000E and XC9000.

- 1. Use the **Shift -F8** keys to display the entire ALU schematic.

- 1. Use the **F8** key to zoom into the open area in the lower righthand corner.

- 2. Select Libraries  $\rightarrow$  XILINX Libraries from the menu bar.

- 3. Select the Unified Libraries and the appropriate family library using the left mouse button.

- 4. Choose BY TYPE  $\rightarrow \texttt{flip}\_\texttt{flop} \rightarrow \texttt{fd4re}$  from the Library menu.

- 5. Move the cursor into the schematic window.

An outline of the fd4re component appears.

- 6. Move the component to lower right corner of the schematic, approximately to the location shown the "Adding FD4RE and AND5B2 to ALU Schematic" figure.

- 7. Press the left mouse button to place the component.

- 8. Repeat steps two through six to place the and5b2 component next to the fd4re as shown in the figure below.

When choosing the component from the library menu, use the selection BY TYPE  $\rightarrow logic \rightarrow and5b2$ .

Figure 10-32 Adding FD4RE and AND5B2 to ALU Schematic

## Adding Nets, Buses, Ports and Labels

#### FD4CE and AND5B2

Next, complete adding the fd4re and and5b2 symbols by adding nets, buses, and labels as follows:

1. Add the necessary nets and buses to complete connections for fd4re and and5b2 as you did for the previous schematic.

The figure below displays the labeled nets and buses for fd4re and and5b2.

- 2. Add ports to the nets and buses attached to the fd4re and and5b2, as shown in the figure below.

- 3. Change the default "NET" properties to the proper names using the Shift-F7 key, as shown in the following figure.

- 4. To add net labels to nets not connected to ports or buses, select the nets as described earlier, then select Right Mouse Button  $\rightarrow$  Name Nets.

For each selected net, the schematic editor asks you for a net label, then offers you the opportunity to place each label on the schematic. The nets should be labeled as shown.

5. Increase the size of the label text as described earlier.

Figure 10-33 Nets, Buses, and Ports for FD4RE and AND5B2

#### ANDBLK2 and ORBLK2

Next, complete the addition of ANDBLK2 and ORBLK2 to the ALU schematic.

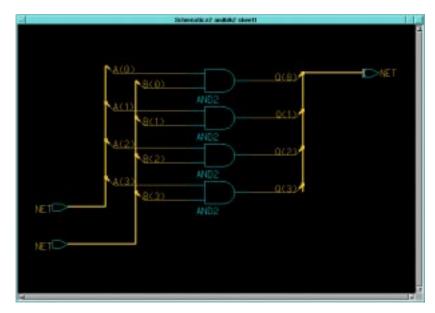

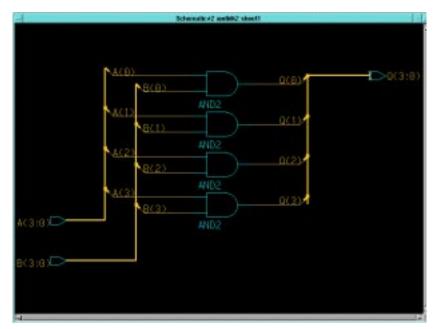

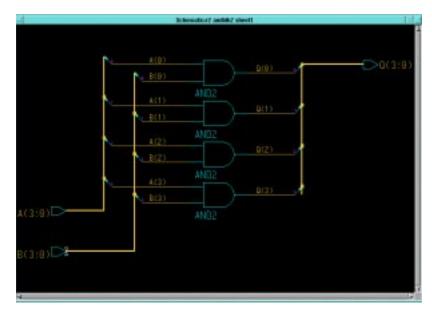

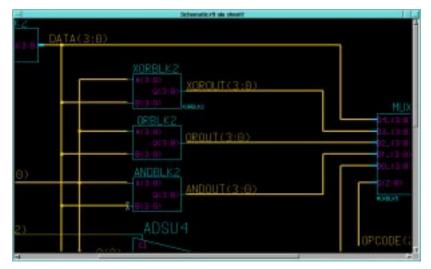

- 1. Add the necessary buses to complete connections for ANDBLK2 and ORBLK2. The figure below displays the labeled nets and buses for ANDBLK2 and ORBLK2.

- 2. Use the figure below to name the added buses by using the same Right Mouse Button  $\rightarrow$  Name Nets from the previous

section. You only need to label the output buses of the two components, since the inputs to these components are connected to pre-labeled buses.

Figure 10-34 Nets, Buses and Labels for ANDBLK2 and ORBLK2

## Adding Labels to Components

It is important to add labels to components. Error and warning messages often reference component labels, and labels also appear in simulation netlists. Also, net names at lower levels of hierarchy are referenced using the following format:

...component\_label/component\_label/net\_label

In the ALU schematic, labels have already been added to the MUXBLK2, XORBLK2, and MUXBLK5 blocks.

To add a label to the ANDBLK2 placement, follow these steps.

- 1. Press the **F2** key to unselect everything.

- 2. Use the left mouse button to select the ORBLK2 symbol.

- 3. Select Right Mouse Button  $\rightarrow$  Properties  $\rightarrow$  Add.

A dialog box appears.

- 4. In the window labeled "Existing Property Name", choose the **INST** property with the left mouse button. It appears highlighted.

- 5. In the Property Value field, type ORBLK2, then press return or choose OK.

- 6. Move the text to position it as shown in the following figure and click the left mouse button to place the text.

- 7. Label the ANDBLK2 symbol the same way using the label ANDBLK2, as shown in the following figure.

- 8. Give the FD4RE component the label ALUVAL.

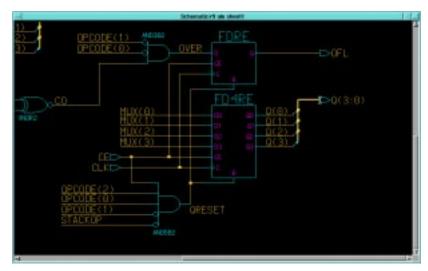

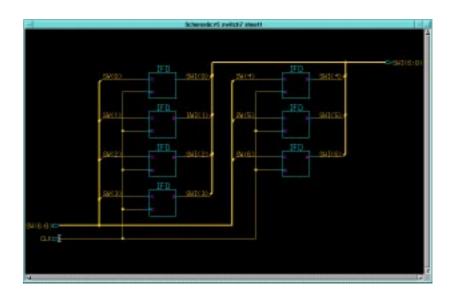

Figure 10-35Adding Component Labels to ALU SchematicThe completed ALU schematic is shown in the following figure.

Figure 10-36 Completed ALU Schematic

## Saving the ALU Schematic

Check the schematic. If errors occur, resolve them and then check and save the schematic.

## **Exploring Xilinx Library Elements**

The Xilinx libraries contain three types of elements. Primitives are basic logic elements such as the and2 and or2 gates that you previously placed in ANDBLK2 and ORBLK2. Soft macros are schematics created by combining primitives and other soft macros. Relationally Placed Macros (RPMs) are soft macros that contain placement information. RPMs are currently only available in the XC4000E library.

All three types of library elements are placed on a schematic in exactly the same way.

### Viewing a Xilinx Soft Macro Schematic

Soft macro schematics are schematics such as you might make for your own designs. In fact, you can load one of these schematics and use the File Save As command to save it under another name, and then edit this new schematic to customize it to your needs.

Open the schematic underneath the fd4re symbol as follows:

- 1. Press the **F2** key to unselect everything.

- 2. Select fd4re with the left mouse button.

- 3. Select  $\mathtt{File} \rightarrow \mathtt{Open}$  Down from the menu bar.

- 4. In the dialog box that appears, select the schematic sheet and click OK.

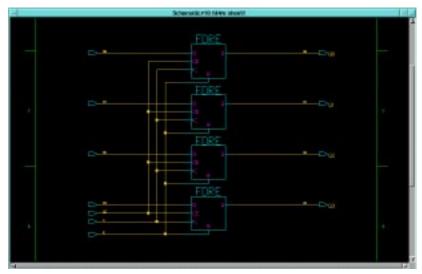

As shown in the following figure, fd4re consists of four fdre symbols.

Figure 10-37 FD4RE Schematic from XC4000E Library

## Viewing a Xilinx RPM (XC4000-Based Families Only)

**Note:** The following description of RPMs contains detailed information on the XC4000E architecture. Refer to *The Programmable Logic*  *Data Book* for more information on the XC4000E CLB structure and fast carry logic.

If your design is not targeted for the XC4000E family, read this section, but do not perform any of the commands. Continue the tutorial with the "Opening the Calc Schematic" section (the next section).

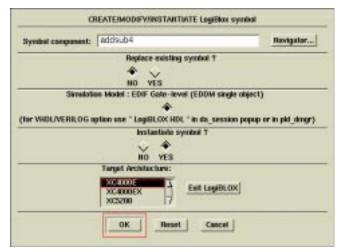

**Note:** The XC5200 library also contains RPMs. If you have an XC5200 schematic, you may open the ADSU4 component as described here to see how this RPM is implemented in that family.