Programming Xilinx CPLDs on GENRAD Testers

**Preface**

Introduction

**Creating SVF Files**

**Creating GenRad Test Files**

Revision 1.8.6

DTS Example and Explanation

**Optimizations**

Using the Batch Download Tool to Generate SVF Files

May 4, 2000 Printed in U.S.A.

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5.717.340: 5.719.506: 5.719.507: 5.724.276: 5.726.484: 5.726.584: 5.734.866: 5.734.868: 5.737.234: 5.737.235:

5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5.847.993; 5.852.323; 5.861.761; 5.862.082; 5.867.396; 5.870.309; 5.870.327; 5.870.586; 5.874.834; 5.875.111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5.990.704; 5.991.523; 5.991.788; 5.991.880; 5.991.908; 5.995.419; 5.995.744; 5.995.988; 5.999.014; 5.999.025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

## **Preface**

### **About This Manual**

This manual describes how to program Xilinx CPLDs on GenRad testers.

Table 0-1 Supported Device Families

| XC9500 Series | XC9500 (5V)<br>XC9500XL (3.3V)                                                                                               |

|---------------|------------------------------------------------------------------------------------------------------------------------------|

| CoolRunner    | XPLA Original XCR3128 (3.3V) XCR5128 (5V) XPLA Enhanced XCR5000C (5V) XCR3000A (3.3V) XCR3000C (3.3V) XPLA3 XCR3000XL (3.3V) |

### **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Introduction," lays out the basic procedure for programming a Xilinx CPLD in a GenRad test environment.

- Chapter 2, "Creating SVF Files," discusses how to create SVF files using JTAG Programmer or XPLA Programmer on a PC.

- Chapter 3, "Creating GenRad Test Files," discusses how to use svf2dts to create compiled test files for use in the GenRad test environment.

- Appendix A, "DTS Example and Explanations," provides a programming example.

- Appendix B, "Optimization," contains some optimization hints.

- Appendix C, "Using the Batch Download Tool to Generate SVF Files Using JTAG Programmer," describes using the batch programming tool.

## **Conventions**

In this manual the following conventions are used for syntax clarification and command line entries.

• Courier font indicates messages, prompts, and program files that the system displays, as shown in the following example.

```

speed grade: -100

```

• Courier bold indicates literal commands that you must enter in a syntax statement.

```

rpt_del_net=

```

• *Italic font* indicates variables in a syntax statement. See also, other conventions used on the following page.

```

xdelay design

```

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

xdelay [option] design

```

Braces "{}" enclose a list of items from which you choose one or more.

```

xnfprep designname ignore rlocs={true|false}

```

• A vertical bar " | " separates items in a list of choices.

```

symbol editor [bus|pins]

```

Other conventions used in this manual include the following.

• *Italic font* indicates references to manuals, as shown in the following example.

See the *Development System Reference Guide* for more information.

• Italic font indicates emphasis in body text.

If a wire is drawn so that it overlaps the pin of a symbol, the two nets *are not* connected.

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "..." indicates that the preceding can be repeated one or more times.

```

allow block blockname loc1 loc2 ... locn;

```

## Chapter 1

## Introduction

This document assumes that you have obtained a JEDEC file for a given design, and describes the procedure necessary to program Xilinx CPLDs with a GenRad in-circuit test system. This document presents the steps you need to perform, which includes:

- Creating an serial vector format (SVF) file using Xilinx's Programmer software

- Generating a GenRad digital test source (.dts) using Xilinx's svf2dts version 1.8.6 software

- Merging a digital test source and other GenRad files into the test program

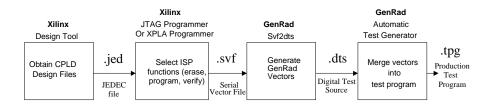

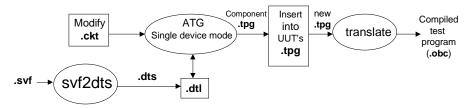

Xilinx programmer software translates a JEDEC file (.jed) into a Serial Vector Format (.svf) file. The Xilinx svf2dts v1.8.6 tool translates a .svf file to a GenRad digital test source, and is maintained by GenRad. Xilinx svf2dts v1.8.6 has been designed specifically to provide support for XC9500 and XC9500XL .svf file constructs created by JTAG Programmer using the program flow illustrated in Figure 1-1.

Figure 1-1 Program Flow

**Note:** GenRad and Xilinx have successfully verified the flow with all members of the XC9500 and XC9500XL families. Certain Xilinx Cool-Runner devices can be programmed with the GenRad tester by replacing JTAG Programmer with XPLA Programmer (available free of charge at <a href="www.xilinx.com/sxpresso/webpack.htm">www.xilinx.com/sxpresso/webpack.htm</a>. GenRad's ISP support page contains more information related to GenRad's support of Xilinx's ISP-capable PLDs. See <a href="www.genrad.com/CSC/isp/default.htm">www.genrad.com/CSC/isp/default.htm</a>)

The Xilinx **svf2dts** v1.8.6 program runs under Windows NT, 95, or 98. JTAG Programmer runs under Windows 95/98 or NT on a PC.

Chapter 2 describes the procedure for creating an SVF file from JTAG Programmer or XPLA Programmer on a PC.

Chapter 3 describes how to produce the GenRad digital test source file (.dts) and merge it into the a test program for production programming.

## **Hardware Requirements**

This software and ISP methodology applies to the following Genrad in-circuit tester families running GenRad software release 3.2 or greater.

- GR2287L/LX

- GR228X i-Series

- TS121

- TS8X

## Software Requirements

#### Xilinx Programmer Software

Software modules can be downloaded for free from http://www.xilinx.com/sxpresso/webpack.htm

- JTAG Programmer (for XC9500/XL)

- XPLA Programmer (for CoolRunner)

#### Genrad Translator svf2dts

Xilinx svf2dts v1.8.6 program requires a GenRad ISP Tools license. **svf2dts** version 1.8.6 is a standalone program complete with a graph-

ical user interface and runs under Windows NT, 95, or 98. The program uses only 164 kilobytes of memory, but requires at least 24 megabytes of hard disk for output files.

• http://www.xilinx.com/isp/ate.htm

#### **Genrad Software**

• http://www.genrad.com

## **Creating SVF Files**

#### Introduction

Xilinx SVF files are created with the JTAG Programmer for XC9500/XL devices, or the XPLA Programmer for Xilinx CoolRunner Devices. This chapter is divided into two sections:

"Using the JTAG Programmer to Generate SVF Files for XC9500/XL Devices" section

"Using the XPLA Programmer to Generate SVF Files for CoolRunner Devices" section

In addition, there is a batch tool for generating SVF files for XC9500/ XL devices. For information on using the JTAG Programmer batch tool, see Appendix C.

## Using the JTAG Programmer to Generate SVF Files for XC9500/XL Devices

This procedure describes how to create an SVF file for XC9500/XL devices; it assumes that you have JTAG Programmer, Version 2.1i or newer. JTAG Programmer is included with the Xilinx Foundation or Alliance Series software. JTAG Programmer is also available free of charge with the *Device Programming Tools* on the Xilinx World Wide Web site, http://www.xilinx.com/sxpresso/webpack.htm.

JTAG Programmer is supplied with both graphical and batch user interfaces. The batch user interface executable name is **jtagprog**; and the graphical user interface executable is named **jtagpgmr**. The graphical tool can be launched from the Design Manager or Project Manager, but may also be launched by opening a shell and invoking **jtagpgmr**. The batch tool is available by opening a shell and invoking

**jtagprog** on the command line. For information on using the JTAG Programmer batch tool, see Appendix C.

In order to program XC9500(XL) devices, the procedure is to **create a separate SVF file for each device being programmed**.

- Run your design through the Xilinx fitter and create a JEDEC file.

- 2. Double-click on the JTAG Programmer icon or open a shell and type jtagpgmr. The JTAG Programmer interface will appear.

Figure 2-1 JTAG Programmer Interface

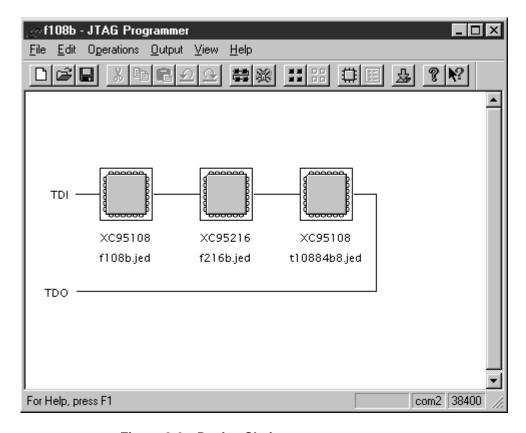

- Instantiate your boundary-scan chain: Manually add each device in the correct boundary-scan order from system TDI to system TDO.

- a) Select  $\mathtt{Edit} \to \mathtt{Add}$  Device for each device in the boundary-scan chain.

- b) Fill in the device properties dialog to identify the JEDEC (if it is an XC9500(XL) device) or BSDL (if it is not an XC9500(XL) device) file associated with the device you are adding.

Figure 2-2 Device Chain

The device type and JEDEC file name will appear below the added device.

4. Put the JTAG Programmer into SVF mode by selecting

Output  $\rightarrow$  Create SVF File...

to create a new SVF file. Fill in the SVF file dialog with the desired name of the target SVF file to be created.

**Note:** Once you enter SVF mode the composition of the boundary-scan chain cannot be edited in order to ensure consistency of the boundary-scan data in the SVF file.

Highlight one of the Xilinx XC9500/XL devices by clicking it once with the mouse. Then, select the Operation -> Program

- menu item and check the **Erase Before Programming** and **Verify** options in the ensuing Program dialog box.

- 6. When you completed the required operations, you may close the current SVF output file by selecting the Output -> Use Cable menu item and pressing Cancel in the ensuing Use Cable dialog box.

- 7. Repeat steps 4 through 6 for each Xilinx XC9500/XL CPLD.

- 8. When you are done with JTAG Programmer, exit by selecting: File->Exit

## Using the XPLA Programmer to Generate SVF Files for CoolRunner Devices

This section describes how to create an SVF file for the CoolRunner devices; it assumes that you have the XPLA Programmer, Version 4.08 or newer. XPLA Programmer software is available free of charge with the Device Programming Tools on the Xilinx World Wide Web site, http://www.xilinx.com/sxpresso/webpack.htm. Simply download the single XPLA Programmer module.

In order to program CoolRunner devices, the procedure is to create a separate SVF file for each device being programmed. We will show you how to do this using the XPLA Programmer software.

**Note:** GenRad does not support programming of XCR (CoolRunner) parts configuration in multiple device JTAG chains

### **Generating SVF Files**

Run your design through the Xilinx CoolRunner fitter and create a JEDEC file. XPLA Programmer 4.09 \_ 🗆 × File Check Cable Port Setup... Device Info ATE output OFF Batch Editor... SS configuration... Windows Help 😽 Configure JTAG chain devices \_ 🗆 × Enter JTAG Chain Description (JCD) below: Total device: 0 PC-ISP Current JCD file: Execute device UES Device # Device Name | IR\_length | Operation Design file name result 😽 Message ■□× NTAG chain route \_ I N TDI

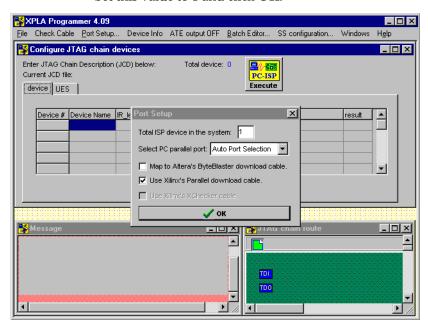

2. Double-click on the "WebPACK XPLA Programmer" icon or invoke the Programmer from the start menu.

Figure 2-3 XPLA Programmer Interface

3. Put the XPLA Programmer into the SVF mode by selecting the following options:

Port Setup -> Total Device in the system

Set this value to 1 and click OK.

Select from the menu bar ATE output OFF -> Generate svf vectors (.svf) (Note: When this option is selected the menu option will change to ATE output ON)

Figure 2-4 ATE SVF Output Generation Selection

5. Select Off-line programming as follows:

Help -> Output/Debug Options -> Off-line programming

(no I/O port access)

#### then click OK.

Figure 2-5 Output/Debug Option to write to a file

**Note:** When this option is selected a flag <<OFF-LINE>> is highlighted in red next to the **Execute** option.

6. Once you are in SVF mode, you can then select the CoolRunner device and programming file. Double-click the **Device Name** field and select from the menu the CoolRunner device targeted.

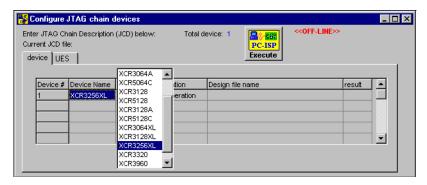

Figure 2-6 Device Selection

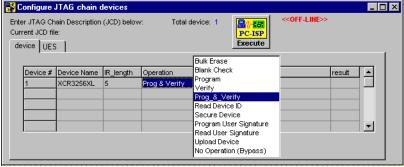

Double-click the **Operation** field and select from the menu **Prog** & **Verify** or some other desired operation.

Figure 2-7 Operation Selection

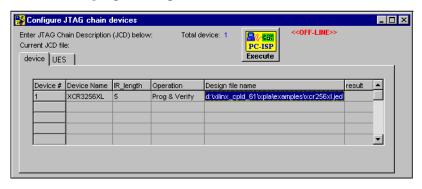

8. Double-click the **Design file name** field and browse for the programming file.

Figure 2-8 Programming File Selection

**Note:** Once you enter SVF mode the composition of the boundary-scan chain cannot be edited in order to ensure consistency of the boundary-scan data in the SVF file.

9. To save the SVF file:

Select File -> Save JCD file and select a directory.

(**Note**: This is the directory in which the SVF file will be saved.) Click the **Execute** button to write the SVF file to the location selected.

10. When you are done with the XPLA Programmer, exit by selecting:

File -> Exit

## Chapter 3

## **Creating GenRad Test Files**

## Using svf2dts

Use the SVF file that you generated as input to the **svf2dts** Conversion Utility. This tool takes an SVF file as input and creates a digital test source (.**dts**) file and report file (.**rpt**) which relays errors or warnings encountered during the conversion process. This chapter provides an overview of the **svf2dts** v1.8.6 user interface, file conversion, and integration program prep steps. While the program prep flow is rather straight forward, the user should be aware of different device configurations and programming techniques. The following sections also discuss different board configurations and GenRad programming options (standard driver/sensor pin memory or Deep Serial Memory) to enhance file management and minimize programming times.

This chapter is divided into the following sections:

- Review of Program Prep

- svf2dts Interface Overview

- Programming an Isolated JTAG Device

- Programming a Device in JTAG Chain Configuration

- Using the Deep Serial Memory Option

- Troubleshooting

## **Review of Program Prep Flow**

Recall that converting the JEDEC design file into an SVF file with a Xilinx Programmer is only one step in the program prep process. The SVF file must be converted into GenRad vectors (.dts file) and integrated into the GenRad test program (.tpg file). The svf2dts tool creates a digital test source (.dts). GenRad's automatic test generator then creates an abbreviated .tpg file which contains the programming instructions and correlates the Xilinx CPLD's signal pins to the target UUT's nodes and test nails. Then the user cuts and pastes the single component .tpg file into the target UUT's test program file. Finally, GenRad's software translates the new .tpg into object code.

Figure 3-1 GenRad Program Prep Flow for Xilinx ISP

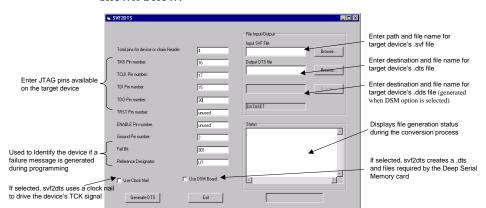

#### Svf2dts Interface Overview

The conversion tool creates a digital test source, complete with header section, and then incorporates the <code>.svf</code> file's programming vectors into commands that will instruct the test systems hardware to drive the Xilinx CPLD's JTAG pins and accomplish various supported functions. In order to successfully generate the GenRad program file(s), the conversion software must obtain information specific to the CPLD device, circuit description and GenRad programming tech-

nique. All required information is entered via the **svf2dts** interface shown below.

Figure 3-2 SVF2DTS V1.8.6 Interface

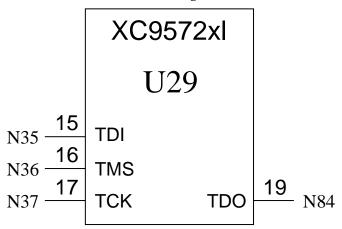

## **Programming an Isolated JTAG Device**

If the target PCB contains an isolated JTAG device or single device chain, all JTAG pins are free and not connected to any other components (see Figure 3-3). The JTAG pins (TDI, TDO, TMS, TCK, TRST) are likely connected to a header or the gold fingers on the PCB. If the target Xilinx CPLD's JTAG pins are connected to another JTAG-

compliant device(s), please skip to the next section (*Programming a Device in a JTAG Chain Configuration*).

Figure 3-3 Single ISP-capable CPLD

```

U29 xc9572xl 1=N24, 2=N103, 3=N199, 4=N222,

: : : : :

13=N13, 14=N43, 15=N35, 16=N36,

17=N37, 18=N92, 19=N84, 20=N233,

U29_P U29PV 1=N24, 2=N103, 3=N199, 4=N222,

: : : :

13=N13, 14=N43, 15=N35, 16=N36,

17=N37, 18=N92, 19=N84, 20=N233,

```

Figure 3-4 Adding a CPLD Programming Entry in the .ckt File

## **Programming Example for a Single Device Chain**

This section presents a step-by-step example for generating a .dts file using the svf2dts v1.8.6 for a Xilinx ISP-capable CPLD.

- 1. Start the **svf2dts**.

- 2. When the user interface appears, carefully fill in all fields in the left column with information related to the target CPLD. (It may be useful to have a schematic available to answer some of the specific device related questions).

Total number of pins for device or chain Header

This field refers to the number of JTAG-related pins present on the target CPLD and will dictate the argument of the SIZE keyword statement in the resultant .dts file. After reviewing the CPLD's pin-out in your schematic document, enter the total number of ISP-related pins. ISP-capable devices should employ at a minimum 4 JTAG-related pins (TDI, TDI, TMS, and TCK).

#### TMS Pin Number

This field refers to the CPLD's TMS signal pin. **svf2dts** will enter this number as the argument/value for TMS in the resultant .**dts** file's INPUT keyword statement located in the Header section.

#### TCK Pin Number

This field refers to the CPLD's TCK signal pin. **svf2dts** will enter this number as the argument/value for TCK in the resultant **.dts** file's INPUT keyword statement.

#### TDI Pin Number

This field refers to the CPLD's TDI signal pin. **svf2dts** will enter this number as the argument/value for TDI in the resultant .**dts** file's INPUT keyword statement located in the Header section.

#### TDO Pin Number

This field refers to the CPLD's TDO signal pin. **svf2dts** will enter this number as the argument/value for TDO in the resultant .dts file's OUTPUT keyword statement located in the Header section.

#### TRST Pin Number

XC9500/XL and CoolRunner devices do not have a TRST JTAG pin. If you are using a device from either of these Xilinx families, leave this space blank when queried by the **svf2dts** program

#### ENABLE Pin Number

XC9500(XL) and CoolRunner devices do not have an ENABLE JTAG pin. If you are using a device from one of these Xilinx families, leave this space blank when queried by the **svf2dts** program. If another device in the JTAG chain employs a ENABLE pin, enter the pin designator.

If you used an alpha-numeric for the signal names above, you must edit the DTS file to add or change all other pins on the device to be alpha-numeric. This will maintain consistency across library modules.

#### Ground Pin Number

Enter on the pin number for one of the CPLD's ground pins.

#### Fail Bit

This field refers to the fail bit to be set in the event that a programming function fails. The default is fail bit 901. Any number over 900 is acceptable.

#### Reference Designator

Enter the reference designator shown in the schematic to identify the target CPLD. In the event that a programming operation fails, the resultant test program will generate an error message which indicts the name denoted in this field (i.e., U29\_P).

Designating input files and output files. In the upper right of the interface, fill in the fields beneath *File Input/Output*

#### Input SVF File

Provides the conversion tool with the path and name of the target CPLDs SVF file. Enter the path and name of the target SVF file (e.g., c:\temp\design1.svf).

#### Output DTS File

Provides the conversion tool with the target location and name for the resultant .dts file. Enter the path and name of the new .dts

- file (e.g., c:\temp\design1.dts). This feature allows you to use a different name for the .dts and .rpt files than you had on the .svf files. This allows easier integration into the ATG process.

- 3. Select clock driver nail to drive the CPLD's TCK signal by clicking the option box next to *Use Clock Nail* located in the lower left of the interface. Using a Clock Driver Nail gives a faster slew rate and, therefore, better noise immunity. Noise can be a significant problem for some applications when programming parts insystem. GenRad recommends selecting this option if one of the test systems clock driver nails is available.

- 4. Selecting the *Use DSM Board* Option (**XC9500/XL only**). If you have a Deep Serial Memory card, GenRad recommends selecting this option which will help minimize programming time and data vector file sizes. However, since a few more program prep steps are required, please proceed to the section entitled Programming Xilinx CPLDs with Deep Serial Memory. If you're not using a DSM continue to step 6.

- 5. Once all of the option selections and fields have been completed, press *Generate DTS*. The resulting .dts file may contain multiple bursts and require a lot of disk space. A resulting .rpt file contains a summary of the data used to generate the .dts and the number of bursts generated. Actual execution time for file conversion varies depending on the size of the .svf file and the speed of your computer.

- 6. Insert the new .dts file into a user .dtl. If a user .dtl does not exist create one with GenRad's library tool interface.

- 7. Run GenRad's Automatic Test Generator in single component mode for the new .dts (in the previous example the single component is U29\_P). The software creates a file named U29\_P.tpg. Copy the file's content and paste in the UUT's .tpg file beneath the section of code for U29\_P in the digital test section.

- 8. Translate the target **.tpg** file.

- 9. Debug the test program

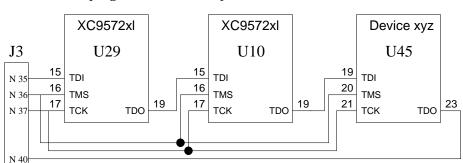

## Programming a Device in a JTAG Chain Configuration

**Note:** The CoolRunner family is supported in single device chains only.

When the target XC9500/XL CPLD lies in a multiple device or JTAG chain configuration, the user must make a couple additional modifications to the .ckt file and generate a .dts for each Xilinx ISP-capable CPLD. In a multiple-device chain, all JTAG-compliant devices in the chain share TCK and TMS signals. However, the first device's TDO signal is connected to the TDI of the second device and so forth (see figure below). From a program prep perspective, each Xilinx ISP-

capable CPLD has an **.svf** file which contains vectors to erase, program, and/or verify the device.

Figure 3-5 Multiple JTAG Device Chain Configuration

Figure 3-6 Modifying the .ckt to Program CPLDs in the Same JTAG Chain

The above example illustrates a three device chain consisting of U29, U5 and U40. The three entries have the same node numbers since the chain must always be driven from the beginning and there are three devices to program and verify.

## **Programming Example for a Multiple Device Chain**

**Note:** The CoolRunner family is supported in single device chains only.

Remember, for each Xilinx XC9500/XL CPLD in the JTAG chain that you want to program, the **svf2dts** must generate a separate .**dts** file. In the example, there are three devices in the JTAG chain. Two are Xilinx XC9572XL devices (which can be programmed) and the third is an arbitrary JTAG-compliant device (e.g., a DSP). In order to program the XC9572XL parts, two .**svf** files (at minimum) should be available. One .**svf** contains instructions to put U10 and U45 into bypass mode and program U29. The other contains instructions to put U29 and U45 into bypass mode and program U10. This section walks through a step-by-step example for generating a .**dts** for U29. Use the same steps to create a .**dts** file for U10.

- 1. Start the **svf2dts** tool.

- 2. When the user interface appears, carefully fill in all of the required fields with information related to the target XC9500/XL CPLD. (It may be useful to have a schematic available to answer some of the specific device related questions).

Total number of pins for device or chain Header

This field refers to the JTAG-related pins employed on the target CPLD. In the example, there are 4 such pins (TDI, TDO, TMS, and TCK)

#### TMS Pin Number

This field refers to the JTAG chain's TMS signal pin. In the multiple-device chain example, TMS for all devices should be referred to entered as 16.

#### TCK Pin Number

This field refers to the JTAG chain's TCK signal pin. In the example, TCK for all devices should be referred to entered as 17.

#### TDI Pin Number

This field refers to the JTAG chain's TDI signal pin. **svf2dts** will enter this number as the argument/value for TDI in the resultant .**dts** files INPUT keyword statement located in the Header section.

#### TDO Pin Number

This field refers to the JTAG chain's TDO signal pin. Since the last device in the chain is U40, it provides the TDO reference for the chain. Since the .ckt file has been modified to note that U29\_P's pin 19 connects to N40 (the node connected to U40's TDO signal), simply enter 19 in this field.

#### TRST Pin Number

XC9500(XL) devices do not have a TRST JTAG pin. If you are using XC9500(XL) devices, leave this space blank when queried by the **svf2dts** program. If another device in the JTAG chain employs a TRST pin, enter the pin designator.

#### ENABLE Pin Number

XC9500(XL) devices do not have an ENABLE JTAG pin. If you are using XC9500(XL) devices, leave this space blank when queried by the **svf2dts** program. If another device in the JTAG chain employs a ENABLE pin, enter the pin designator.

If you used an alpha-numeric for the signal names above, you must edit the DTS file to add or change all other pins on the device to be alpha-numeric. This will maintain consistency across library modules.

#### Ground Pin Number

Enter on the pin number for one of the XC9500/XL CPLD's ground pins.

#### Fail Bit

This field refers to the fail bit to be set in the event that a programming function fails. The default is fail bit 901 and could be used for the first device in the chain (any number over 900 is acceptable). However, subsequent devices require a different fail bit to differentiate one from the other when a failure is encountered. GenRad recommends incrementing the failure bit by one for each additional device (i.e., in the example, use 902 for U10).

#### Reference Designator

This field denotes reference designator for the target XC9500/XL XC9500/XL Series CPLD. In the event that a programming operation fails, the resultant test program will generate an error

message which indicts the name denoted in this field (i.e., U29\_P). This assists in properly identifying a failed device.

3) Designate input files and output files. In the upper right of the interface, fill in the fields beneath *File Input/Output*

#### Input SVF File

Provides the conversion tool with the path and name of the target XC9500/XL CPLD's SVF file. Enter the path and name of the target SVF file (e.g., c:\temp\design1.svf).

#### **Output DTS File**

Provides the conversion tool with the target location and name for the resultant .dts file. Enter the path and name of the new .dts file (e.g., c:\temp\design1.dts). This feature allows you to use a different name for the .dts and .rpt files than you had on the .svf files. This allows easier integration into the ATG process. The DTS file will be in the kilobyte range.

- 3. Select clock driver nail to drive the XC9500/XL CPLD's TCK signal by clicking the option box next to *Use Clock Nail* located in the lower left of the interface. Using a Clock Driver Nail gives a faster slew rate and, therefore, better noise immunity. Noise can be a significant problem for some applications when programming parts in- system. GenRad recommends selecting this option if one of the test systems clock driver nails is available.

- 4. Selecting the *Use DSM Board* Option. If you have a Deep Serial Memory card, GenRad recommends selecting this option which will help minimize programming time and data vector file sizes. However, since a few more program steps are required please proceed to the section entitled Programming Xilinx XC9500/XL CPLDs with Deep Serial Memory.

- 5. Once all of the option selections and fields have been completed, press *Generate DTS*. The resulting .dts file will contain multiple bursts and may require a lot of disk space. There will also be a .rpt file that contains a summary of the data used to generate the .dts and the number of bursts generated. Actual execution time for the file conversion varies depending on the size of the .svf file and the speed of your computer.

- 6. Repeat steps 1-5 for each device and/or .svf file.

- 7. Insert the new .dts file into a user .dtl. If a user .dtl does not exist create one with GenRad's library tool interface.

- 8. Run GenRad's Automatic Test Generator in single component mode for the new .dts (in the previous example the single component is U29\_P). The software creates a file named U29\_P.tpg. Copy the file's content and paste in the UUT's .tpg file beneath the section of code for U29\_P in the digital test section.

- 9. Translate the target .tpg file.

- 10. Debug the test program

- 11. Repeat steps 6-10 for each new .dts file.

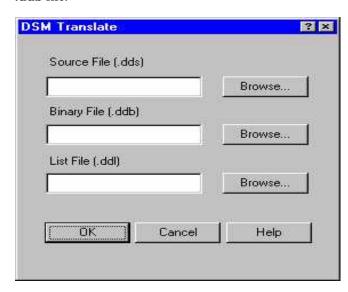

## **Using the Deep Serial Memory Option**

**Note:** The Deep Serial Memory Option is supported for XC9500/XL devices only. CoolRunner devices do not support this option.

If you have a Deep Serial Memory (DSM) board on your tester you should use it. Using Deep Serial Memory will result in significantly smaller file sizes. The DDS file will be in the 1 to 4 megabyte range. The DTS file will be in kilobyte range.

- 1. Enter the appropriate information into all **svf2dts** interface fields.

- 2. Click the option box next to *Use DSM Board* located in the lower left of the interface. Notice that a new field is now present within the File Input/Output section.

- 3. Enter a filename and destination path for the resultant .dds file required for the DSM option.

- 4. Press Generate DTS.

- 5. Insert the new .dts component into .dtl

- 6. Deep Serial Memory provisions

- a) Create an automatic test options file (.ato). This file will load the DSM binary file for the ISP component

- b) Run DSM Translate on the DSM source (.dds) file to create the .ddb file. Use the DSM Translate Page in GenRad' ISP

Tool or 228X monitor pages DSM Translate page to create the .ddb file.

Figure 3-7 DSM Translate Interface Available in GenRad's ISP Tool V1.0

- c) Run GenRad's ATG with the newly created .ato file

- 7. Translate/compile test program (.tpg)

- 8. Debug test program

## **Troubleshooting**

- There MUST be accurate BSDL files for all devices in the chain.

- Unique FAIL bits MUST be assigned to each Xilinx device being tested.

- Branch statements may need to be added at label DDONE: to include the FAIL bits used in testing the devices.

- For erase vectors on XC9500 devices, you may need to increase

the erase "pulse" times. In fact, this is highly recommended for a

robust program. To increase the erase "pulse" times, you must

manually edit the DTS or SVF file. It is easiest to edit the SVF file

before running it through the svf2dts translator. In the SVF,

replace every instance of "RUNTEST 1300000 TCK;" with

"RUNTEST 2600000 TCK;". This will double the erase "pulse" time from 1.3 seconds to 2.6 seconds per erase "pulse". There are 2 to 32 erase "pulses" per erase operation depending on the device. This is not usually required for XC9500XL devices.

## **Appendix A**

## **DTS Example and Explanation**

```

/* U5PV.DTS created by SVF2DTS version 1.8.6 utility 04-2-2000 09:30:33 */

.HEAD;

.SIZE 4;

.INPUT(1=TMS,2=TCLK,3=TDI);

.OUTPUT (4=TDO);

.PERIOD 1U; /* TCK is set to 1 MHz by the conversion tool

.END HEAD;

Any routine used more than once is put in a subroutine to decrease

the number of bursts required.

.FASTSUB TCLK;

$ IC(TCLK) IH(TCLK);

$ IL(TCLK);

$ RETURN;

.END FASTSUB;

Additional subroutines deleted for readability.

.MAIN USING (F=TDO);

BURST ACTIVE NOPRINT NOFAULT NODIAG FAIL() MAXTIME=60;

FAST;

```

Test steps deleted for readability.

The output .DTS is fully commented and includes any comments that were in the input .SVF file. Test steps that check data set the assigned FAIL bit if they fail.

```

/* Shift in FF masked with FF */

```

The Xilinx programming algorithm requires the location be tried up to 32 times if it fails to program. To accomplish this we loop on the programming command 31 times. The two status bits are tested each pass through the loop and set the local FLAGFAIL Status bit.

If FLAGFAIL is not set then both status checks pass. Branch around retry and continue programming. If either status check fails, attempt to program the location up to 31 times.

```

GOTO P1 FLAG PASSES;

/* Operation failure retry */

$ GOSUB RETRY;

$ GOSUB W1800000;

/* Set state to DRSHIFT from IDLE */

$ GOSUB IDL2DRS;

IL (TMS);

/* State is now DRSHIFT */

END FLOOP:

If after 31 attempts the location still fails, try one more time. This time

if it fails set the status FAIL bits 193 or 194

OS(TDO) OH(TDO) FLAGFAIL ~FAIL(193)~;

$ IL(TDI);

$ GOSUB TCLK;

OH(TDO) FLAGFAIL ~FAIL(194)~;

$ IH(TDI);

Test steps deleted for readability.

/* Branch to burst end if fails after 32 attempts */

Check the fail flag and branch to the end of the burst if the location

failed.

GOTO BE1 FLAG FAILS;

P1:

Test steps deleted for readability.

BE1: $ ;

END FAST;

The END BURST statement clears FAIL bits 193 and 194. Then it

checks the FAIL bit assigned to the device. If the FAIL bit is set, a

failure message is printed and any remaining bursts are branched.

DTG will add the correct branch statement before the "]".

END BURST[IF FAIL(193) THEN BITCLR(FAIL, 193);

```

```

IF FAIL(194) THEN BITCLR(FAIL,194);

IF FAIL(196) THEN WRITE ID=MESFILE 'Device U5 failed%NL%';

IF FAIL(196) THEN ];

```

Additional bursts deleted.

The last burst is done only to clear the active state.

```

BURST;

/* This burst is done only to clear the active state!! */

IC(TDI,TMS,TCLK);

ID(#);

END BURST;

.END MAIN;

```

## Appendix B

## **Optimizations**

You can use several simple techniques to optimize and reduce the overall programming time.

- If you have Deep Serial Memory, use the Deep Serial Memory option. Deep Serial Memory more efficiently handles the large ISP vector sets (not applicable to CoolRunner devices).

- If you always program factory fresh (i.e. blank) XC9500 devices, eliminate the erase operation by unchecking the Erase Before Programming option in the Program dialog box when generating the SVF file. The erase operation consumes the majority of the overall programming time for XC9500 devices.

The erasure time for CoolRunner devices is only 100 ms; the removal of the Erase procedure will not significantly improve the programming times for CoolRunner CPLDs.

Additionally, several advanced techniques may be used to optimize and reduce the overall programming time:

• If most of the devices you program are blank (erased), you can conditionally erase an XC9500 device. You must generate separate SVF files that contain the following operations per SVF file: blank check, erase, and program+verify. To create the blank check SVF, you must obtain the .jed file for a blank (erased) device. Blank .jed files can be obtained via ftp://ftp.xilinx.com/pub/swhelp/cpld/blank.zip. Use JTAG Programmer to generate an SVF that contains a verify operation using the blank .jed file. In your GenRad test program, you must first execute the blank verify operation. Then, based on the result, you can conditionally execute the erase vectors from the SVF with the erase operation. Finally, execute the program+verify vectors on the device. The verify (blank check) operation executes very quickly in comparison to the regular, sector-based erase operation.

- You can use the faster bulk erase method for later revisions of the XC9500 devices. By default, JTAG Programmer uses the sectorbased erase operation for XC9500 devices because the sectorbased erase is supported in all revisions of the XC9500 devices.

- All XC9500 devices with a 0000 bit value in the revision field (4 most-significant-bits) of the IDCODE only support the sector-based erase. The later revisions of the XC9500 devices support a faster *bulk erase* operation.

- To force JTAG Programmer to use the bulk erase operation, you must temporarily replace the base BSDL file in the \$XILINX/xc9500/data/ directory with the higher revision BSDL file while you create the SVF files. For example, you can replace the xc9536.bsd file with the xc9536\_v2.bsd file. Now, you can generate an SVF that contains the bulk erase operation. (Remember to restore the original BSDL file so that JTAG Programmer will work correctly with all revisions of the XC9500 devices.)

- You may want to implement your GenRad test program such that it conditionally performs either the sector-based erase or the bulk erase operation based on the device IDCODE. To create vectors that check a device IDCODE, create an SVF that contains the Get IDCODE operation. By default, JTAG Programmer generates the IDCODE check (SDR command) in the SVF with a MASK value that ignores the revision field (4 most-significant-bits) of the IDCODE. Manually edit the SVF to check all bits of the 32-bit IDCODE. Make sure the TDO is expecting all zeroes for the revision field of the IDCODE. Then, you can use the IDCODE SVF to check if a device is a revision 0000 device. If it is a revision 0000 device, you perform the regular sector-based erase. Otherwise, you can perform the bulk erase.

## **Appendix C**

# Using the Batch Download Tool to Generate SVF Files Using JTAG Programmer

- 1. Run your design through the Xilinx fitter and create a JEDEC programming file. If you have already been provided with a JEDEC file, proceed to the next step.

- 2. Set the Xilinx environment variable to the Xilinx installation directory:

#### SET XILINX=C:\XILINX\_CPLD

Invoke the batch JTAG Programmer tool from the command line in a new shell.

```

jtagprog -svf

```

The following messages will appear:

```

JTAGProgrammer: version <Version Number> Copy-

right:1991-2000

Sizing system available memory...done.

***SVF GENERATION MODE***

[JTAGProgrammer::(1)]>

```

4. Set up the device types and assign design names by typing the following command sequence at the JTAG Programmer prompt:

```

part deviceType1:designName1 deviceType2:designName2

... deviceTypeN:designNameN

```

where devicetype is the name of the BSDL file for that device and designName is the name of the design to translate into SVF.

Multiple deviceType:designName pairs are separated by spaces. For example:

```

part xc95108:abc12 xc95216:ww133

```

The part command defines the composition and ordering of the boundary-scan chain. The devices are arranged with the first device specified being the first to receive TDI information and the last device specified being the one to provide the final TDO data.

**Note** For any non-XC9500(XL) device in the boundary-scan chain, make certain that the BSDL file is available either in the XILINX variable data directory, or by specifying the complete path information in the deviceType. The designName in this case can be any arbitrary name.

5. Enter the following command to create SVF files for each Xilinx XC9500/XL CPLD:

```

program -h -v designName -j jedecName.jed

```

You may enter any of the following alternate commands:

erase [-fh] designName -- generates an SVF file to describe the boundary-scan sequence to erase the specified part. The -f flag generates an erase sequence that overrides write protection on devices. The -h flag indicates that all other parts (other than the specified designName) in the boundary-scan chain should be held in the HIGHZ state during the erase operation. Xilinx recommends erase -f -h designName.

**verify** [-h] *designName* [-j *jedecFileName*] -- generates an SVF file to describe the boundary-scan sequence to read back the device contents and compare it against the contents of the specified JEDEC file. The JEDEC file defaults to be the designName.jed in the current directory, or may be alternatively specified using the j flag. The -h flag is used to specify that all other parts (other than the specified designName) in the boundary-scan chain should be held in the HIGHZ state during the verify operation. Xilinx recommends **verify** -h *designName*.

**program** [-**vbh**] *designName* -**j** [*jedecFileName*] -- generates an SVF file to describe the boundary-scan sequence to program the device using the programming data in the specified JEDEC file. The JEDEC file defaults to be *designName*.**jed** in the current directory, or may be alternatively specified using the -**j** flag. The -**h**

flag is used to specify that all other parts (other than the specified *designName*) in the boundary scan chain should be held in the HIGHZ state during the programming operation. The -v option specifies that a verify operation should be performed immediately after the program operation has completed. The -b flag indicates the erase operation should be skipped. The erase operation is performed, by default, prior to the program operation. This is useful when programming devices shipped from the factory. Xilinx recommends program -h -v designName.

partinfo [-h] -idcode designName -- generates an SVF file to describe the boundary-scan sequence to read back the 32 bit hard-coded device IDCODE. The -h flag is used to specify that all other parts (other than the specified designName) in the boundary scan chain should be held in the HIGHZ state during the IDCODE operation. This operation can be performed in any combination of the three SVF files.

partinfo [-h] -signature designName -- generates an SVF file to describe the boundary-scan sequence to read back the 32 bit user-programmed device USERCODE. The -h flag is used to specify that all other parts (other than the specified designName) in the boundary scan chain should be held in the HIGHZ state during the USERCODE operation. This operation can be performed in any combination of the SVF files.

6. Exit JTAG Programmer by entering the following command:

quit

The SVF file will be named designName.svf and will be created in the current working directory. Consecutive operations on the same designName will append to the SVF file. To create SVF files with separate operations in each, you will need to rename the SVF file after each operation by exiting to the system shell.