November 3, 2000

Xilinx Inc.

Phone:

Fax:

URL:

•

٠

٠

٠

•

2100 Logic Drive

Features

**FPGAs**

memorv

phase accumulator)

can be supported

Generator System

performance

San Jose, CA 95124

XILINX<sup>®</sup>

+1 408-559-7778

$+1\ 408-559-7114$

www.xilinx.com/ipcenter

Sine, Cosine or quadrature outputs

4-to-32 bit output sample precision

Simple fixed output frequency option

www.xilinx.com/support/techsup/appinfo

Drop-in module for Virtex<sup>™</sup>, Virtex<sup>™</sup>-E, Spartan<sup>®</sup>-II

Look-up table can be allocated to distributed or block

Sine/cosine table depths from 8 to 65536 samples

resolution (  $\Delta f = 0.02$  Hz @ fclk = 100 MHz, 32-bit

synthesizers with precisely controlled phase differences

Incorporates Xilinx Smart-IP technology for maximum

To be used with version 3.1i or later of the Xilinx CORE

High precision synthesizer with fine frequency

Optional phase offset capability so that several

## **Direct Digital Synthesizer (DDS)** V2.0

**Product Specification**

# **General Description**

Direct digital synthesizers (DDS), or numerically controlled oscillators (NCO), are important components in many digital communication systems. Quadrature synthesizers are used for constructing digital down and up converters, demodulators, and implementing various types of modulation schemes, including PSK (phase shift keying), FSK (frequency shift keying), and MSK (minimum shift keying). A common method for digitally generating a complex or real valued sinusoid employs a look-up table scheme. The lookup table stores samples of a sinusoid. A digital integrator is used to generate a suitable phase argument that is mapped by the look-up table to the desired output waveform.

Typical applications of a DDS include

- Digital radios and modems •

- Software-defined radios (SDR)

- Digital down/up converters for cellular and PCS base stations

- Waveform synthesis in digital phase locked loops

- Generating injection frequencies for analog mixers

## Theory of Operation

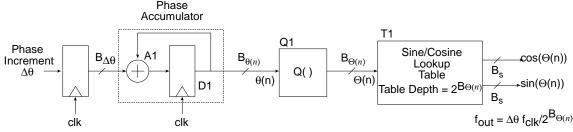

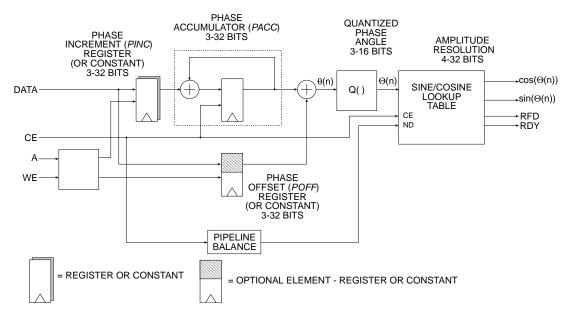

A high-level view of the DDS Core is presented in Figure 1. The integrator (components D1 and A1) computes a phase slope that is mapped to a sinusoid (possibly complex) by the look-up table T1. The quantizer Q1, which is simply a slicer, accepts the high-precision phase angle  $\Theta(n)$  and generates a lower precision representation of the angle denoted as  $\Theta(n)$  in the figure. This value is presented to the address port of a look-up table that performs the mapping from phase-space to time.

Figure 1: Phase truncation DDS. This is a simplified view of the DDS Core.

The fidelity of a signal formed by recalling samples of a sinusoid from a look-up table is affected by both the phase and amplitude quantization of the process. The length and width of the look-up table affect the signal's phase angle resolution and the signal's amplitude resolution respectively. These resolution limits are equivalent to time base jitter and to amplitude quantization of the signal, and add spectral modulation lines and a white broad-band noise floor to the signal's spectrum.

Direct digital synthesizers use an addressing scheme with an appropriate look-up table to form samples of an arbitrary frequency sinusoid. If an analog output is required, the DDS presents these samples to a digital-to-analog converter (DAC) and a low-pass filter to obtain an analog waveform with the specific frequency structure. Of course, the samples are also commonly used directly in the digital domain. The look-up table traditionally stores uniformly spaced samples of a cosine and a sine wave. These samples represent a single cycle of a length  $N = 2^{B_{\Theta(n)}}$  prototype complex sinusoid and correspond to specific values of the sinusoid's argument  $\Theta(n)$  as shown in Eq.(1).

$$\Theta(n) = n \frac{2\pi}{N} \tag{1}$$

where *n* is the time series sample index.

Quarter wave symmetry in the basis waveform can be exploited to construct a DDS that uses shortened tables. In this case, the two most significant bits of the quantized phase angle  $\Theta(n)$  are used to perform quadrant mapping. This implementation results in a more area efficient implementation because the memory requirements are minimized – either fewer FPGA block RAMs or reduced distributed memory. Based on the Core customization parameters, the DDS core will automatically employ quarter-wave symmetry when appropriate<sup>1</sup>.

#### Output Frequency

The output frequency,  $f_{\rm out}$ , of the DDS waveform is a function of the system clock frequency  $f_{\rm clk}$ , the number of bits  ${}^B{}_{\Theta\,(n)}$  used to address the sine/cosine lookup table and the phase increment value  $\Delta\theta$ . That is,  $f_{\rm out}=f\bigl(f_{\rm clk},B_{\Theta(n)},\Delta\theta\bigr).$

The output frequency in Hertz is defined as

$$f_{\rm out} = \frac{f_{\rm clk} \Delta \theta}{2^{B_{\Theta(n)}}} \,\mathrm{Hz} \tag{2}$$

For very short tables, FPGA logic resources are actually minimized by storing a complete cycle. The user is not required to make any design decisions in this context – the Core Generator will always produce the smallest Core possible. For example, if the DDS parameters are

$$f_{clk} = 120 \text{ MHz}$$

$$B_{\Theta(n)} = 10$$

$$\Delta \theta = 12_{10}$$

(3)

the output frequency will be

$$f_{\text{out}} = \frac{f_{\text{clk}} \Delta \theta}{2^{B_{\Theta(n)}}} \text{Hz}$$

$$= \frac{120 \times 10^{6} \times 12}{2^{10}}$$

$$= 1.406250 \text{ MHz}$$

(4)

The phase increment value  $\Delta \theta$  required to generate an output frequency  $f_{\rm out}$  Hz is

$$\Delta \theta = \frac{f_{\text{out}} 2^{B_{\Theta(n)}}}{f_{\text{clk}}}$$

(5)

## **Frequency Resolution**

The frequency resolution  $\Delta f$  of the synthesizer is a function of the clock frequency and the number of bits  $B_{\theta(n)}$  employed in the phase accumulator. The frequency resolution can be determined using the following equation

$$\Delta f = \frac{f_{\text{clk}}}{2^{B_{\theta(n)}}} \tag{6}$$

For example, for the DDS parameters

$$f_{\rm clk} = 120 \text{ MHz}$$

(7)

$$B_{\theta(n)} = 32$$

the frequency resolution is

$$\Delta f = \frac{f_{\text{clk}}}{2^{B_{\theta(n)}}}$$

$$= \frac{120 \times 10^{6}}{2^{32}}$$

$$= 0.0279396 \text{ Hz}$$

(8)

#### **Phase Increment**

The phase increment term  $\Delta \theta$  defines the synthesizer output frequency. Consider a DDS with the following parameterization

$$f_{clk} = 100 \text{ MHz}$$

$$B_{\theta(n)} = 28 \qquad (9)$$

$$B_{\Theta} = 12$$

To generate a sinusoid with frequency  $f_{out} = 19$  MHz, the required phase increment would be

$$\Delta \theta = \frac{f_{\text{out}} 2^{B_{\Theta(n)}}}{f_{\text{clk}}}$$

$$= \frac{19 \times 10^{6} \times 2^{12}}{100 \times 10^{6}}$$

$$= 778.24$$

(10)

#### Spectral Purity Considerations

The fidelity of a signal formed by recalling samples of a sinusoid from a look-up table is affected by both the phase and amplitude quantization of the process. The length and width of the look-up table affect the signal's phase angle resolution and the signal's amplitude resolution respectively. These resolution limits are equivalent to time base jitter and to amplitude quantization of the signal and add spectral modulation lines and a white broad-band noise floor to the signal's spectrum.

In conjunction with the system clock frequency, the phase accumulator width determines the frequency resolution of the DDS. The accumulator must have a sufficient field width to span the desired frequency resolution. For most practical applications, a large number of bits are allocated to the phase accumulator in order to satisfy the system frequency resolution requirements. By way of example, if the required resolution is 1 Hz, and the clock frequency is 100 MHz, the required field width of the accumulator is

$$B_{\theta(n)} = \log_2 \left[ \frac{f_{\text{clk}}}{\Delta f} \right]$$

=  $\left[ \log_2 \frac{100 \times 10^6}{1} \right]$  (11)

=  $\left[ 26.5754 \right]$

= 27 bits

where denotes the ceiling operator. Due to excessive memory requirements, the full precision of the phase accumulator cannot be used to index the sine/cosine look-up table. A quantized (or truncated) version of the phase angle is used for this purpose. The block labeled Q1 in Figure 1 performs the phase angle quantization. The lookup table can be located in block or distributed memory.

Quantizing the phase accumulator introduces time base jitter in the output waveform. As shown in Eq. (12), this jitter results in undesired phase modulation that is proportional to the quantization error.

$$\Theta(n) = \theta(n) + \delta\theta(n)$$

$$e^{j\Theta(n)} = e^{j[\theta(n) + \delta\theta(n)]} = e^{j\theta(n)}e^{j\delta\theta(n)}$$

$$e^{j\Theta(n)} \approx e^{j\theta(n)}[1 + j\delta\theta(n)]$$

$$\approx e^{j\theta(n)} + j\delta\theta(n)e^{j\theta(n)}$$

(12)

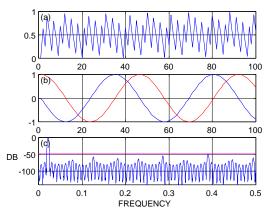

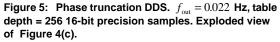

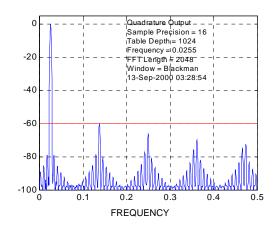

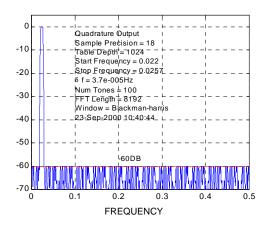

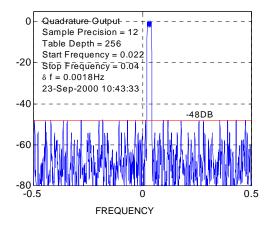

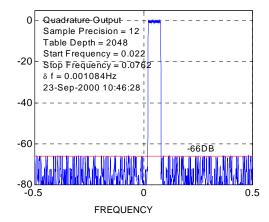

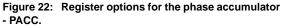

Figure 2 shows the look-up table addressing error, complex output time-series and the spectral domain representation of the output waveform produced by the DDS structure shown in Figure 1. The normalized frequency for this signal is 0.022 Hz, which corresponds to phase accumulation steps of 7.92 degrees per output sample. The angular resolution of the 256-point look-up table is 360 / 256 or 1.40625 degrees per address, which is equivalent to 7.92 / 1.40625 or 7.0549 addresses per output sample. Since the address must be an integer, the fractional part is discarded and the resultant phase jitter is the cause of the spectral artifacts. Figure 3 provides an exploded view of the spectral plot in Figure 2(c).

Figure 2: Phase truncation DDS.  $f_{\rm out} = 0.022$  Hz, table depth = 256 12-bit precision samples. (a) Phase angle addressing error. (b) Complex output time series. (c) Output spectrum.

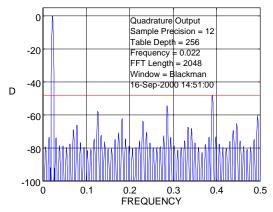

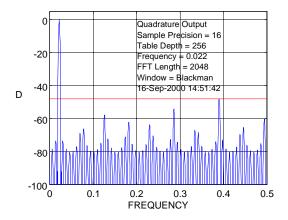

Figure 3: Phase truncation DDS.  $f_{out} = 0.022$  Hz, table depth = 256 12-bit precision samples. Exploded view of Figure 2(c).

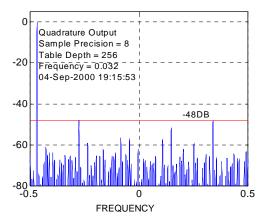

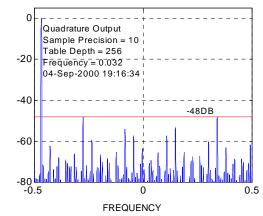

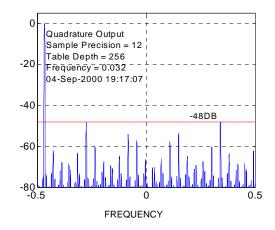

We make two observations related to the phase jitter structure level. Observe that the fractional part of the address count is a periodic (sawtooth) error sequence which is responsible for the harmonic rich (and aliased) low-level phase modulation evident in Figure 3. We also note that the peak distortion level due to incidental phase modulation is approximately 48 dB below the desired signal level, which is consistent with 6 dB/bit of address space. Put another way, if *S* dB of spur suppression is required in the output waveform, as referenced to the 0 dB primary tone, the DDS lookup table must support at least  $\lceil \log_2 S \rceil$  address bits. For example, if *S* = 70 dB, which means that the highest spur will be 70 dB below the main signal, then the minimum number of address bits for the lookup table is  $\lceil \log_2 70 \rceil = 12$  bits, that is, a 4096-bit deep table.

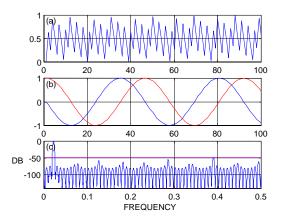

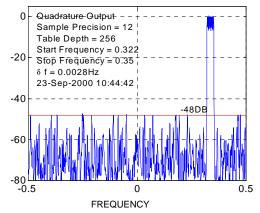

Figure 4 and Figure 5 demonstrate the performance of a similar DDS to the one presented in Figure 2, but in this example 16-bit precision output samples have been used. Observe that the highest spur is still at the -48 dB level, and allocating 4 additional bits to the output samples has not contributed to any further spur reduction. For a phase truncation DDS, the only option to further reduce the spur levels is to increase the depth of the look-up table.

Figure 4: Phase truncation DDS.  $f_{\rm out} = 0.022$  Hz, table depth = 256 16-bit precision samples. (a) Phase angle addressing error. (b) Complex output time series. (c) Output spectrum.

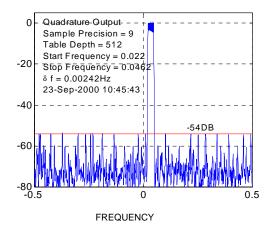

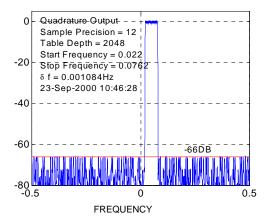

Further examples illustrating the performance of various DDS configurations are shown in Figure 6 through Figure 16. The configuration details are annotated on the plot. For some of these examples, the synthesized frequency has been swept across a small range of the available output bandwidth. For these cases, the sweep start frequency, stop frequency, frequency increment  $\partial_{f}^{r}$  and the number of tones in the sweep interval (*Num Tones*) is indicated. The analysis transform length and window function applied to the output time series is also indicated on the plots.

Figure 8:

Figure 10:

Figure 11:

Figure 13:

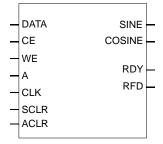

Figure 1 provides a simplified view of the DDS core. A detailed view is shown in Figure 17. This detailed figure is similar to the simplified view, but also indicates the DDS control and interface *signals CE, A, WE, DATA, RFD* and *RDY*. Also note the inclusion of the *PHASE OFFSET* register designated *POFF*. This register is used for applying a constant phase offset to the phase slope computed in the phase accumulator *PACC*. When the Core is customized, the phase offset source can be defined as either a register, a constant, or it can be omitted entirely. When the *register* option is selected, the phase offset value is supplied via the *DATA* port. The phase offset value is treated as an unsigned quantity. If necessary, the phase offset is zero-extended before it is added to the phase accumulator.

Figure 17: DDS Core—detailed view.

#### Figure 18: DDS Symbol

The phase increment value can be sourced from either a register or a constant. When the registered option is selected, the *DATA* port supplies the phase increment value to the phase increment register. When the *constant* option is selected, the DDS output frequency is fixed and cannot be adjusted once the Core is embedded in a design.

Table 1: DDS Core ports and definitions. † denotes optional pin

| Signal<br>Name | Direction | Description                                                                                                                                                                                                               |

|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK            | Input     | Master Clock (active rising edge)                                                                                                                                                                                         |

| A†             | Input     | Internal register address select. The $A$ port selects either the <i>PINC</i> or <i>POFF</i> for a write operation. When $A$ =0 the <i>PINC</i> register is selected. When $A$ =1, the <i>POFF</i> register is selected.  |

| WE†            | Input     | Write enable signal that enables a write operation to the <i>PINC</i> or <i>POFF</i> register. This is an active high signal that must be active to perform write operations to the <i>PINC</i> or <i>POFF</i> registers. |

| CE†            | Input     | Clock enable (active high). <i>CE</i> must<br>be high during normal Core opera-<br>tion, but it is not required to be active<br>during a write access to any internal<br>registers.                                       |

| DATA†          | Input     | Time shared data bus. The DATA port is used for supplying values to the PINC or POFF registers.                                                                                                                           |

<sup>2</sup>Assuming this port is present

# Table 1: DDS Core ports and definitions. † denotes optional pin (Cont.)

| Signal<br>Name | Direction | Description                                                                                                                                                                                                                 |

|----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACLR†          | Input     | Asynchronous clear - active high.<br>When ACLR is asserted, the all reg-<br>isters in the Core are cleared. RDY<br>is also deasserted.                                                                                      |

| SCLR†          | Input     | Synchronous clear - active high.<br>When <i>SCLR</i> is asserted, all regis-<br>ters in the Core are cleared. <i>RDY</i> is<br>also deasserted.                                                                             |

| RDY†           | Output    | Indicates when the output samples are available.                                                                                                                                                                            |

| RFD†           | Output    | <i>RFD</i> is a dataflow control signal<br>present on many Xilinx LogiCOREs.<br>In the context of the DDS, it is sup-<br>plied only for consistency with other<br>LogiCores. This optional port is al-<br>ways tied to VCC. |

| SINE           | Output    | Sine time-series.                                                                                                                                                                                                           |

| COSINE         | Output    | Cosine time-series.                                                                                                                                                                                                         |

# Interface, Control and Timing

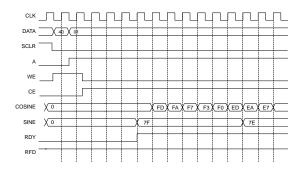

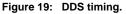

Figure 19 shows the timing sequence required to initialize and activate the DDS core. In this example, the DDS has both a phase increment (PINC) and a phase offset register (POFF). The phase increment register is first initialized with the value 0x40. This is realized by supplying the phase increment value on the DATA port and selecting the PINC register by defining the address port as A=0. The write is performed on the positive clock edge. WE must be active; *i.e.*, WE=1, to perform this operation. Immediately after the PINC register is loaded, the value 0x1 is written to the POFF register. This requires A=1 and WE=1. The register is loaded on the rising edge of the clock. CE does not have to be active to write to either the PINC or POFF registers. The DDS will start operating once the clock enable is applied (CE=1). Since CE is an optional pin, DDS configurations that do not include this pin will begin operating once the FPGA is configured and the system clock is active. After a start-up latency (measured from the assertion of  $CE^{2}$ ) that depends on the pipelining configuration chosen for the Core, in addition to the register configuration in the phase accumulator (zero-cycle latency or one-cycle latency), samples will be presented on the output port(s). This is indicated by RDY=1. For most configurations, the assertion by the Core of RDY indicates the first valid output sample. However, there is an exception. If a DDS is customized such that the O-cycle latency phase accumulator option is selected, and the sine-cosine look-up table is in distributed memory, and the table is purely combinatorial, any writes to the PINC register will be immediately reflected at the output port(s). This is irrespective of whether CE is asserted or not. In this situation, there are no registers between the PINC register and the output nodes, there is only a combinatorial arrangement of logic. Therefore, the CE pin cannot have any influence on this path through the system. The CE pin will, of course, still control the operation of the register (now in the upper arm of the phase accumulator shown in Figure 22(b)) in the PACC.

The DDS can have an optional asynchronous clear or synchronous clear port. The option to simultaneously support both clear options is also provided. When either type of clear is applied, the Core will cease operation. This is indicated by the deassertion of the *RDY* output signal. The *SINE* and *COSINE* output ports will assume a value of 0. All internal registers will also be reset.

## **Parameters**

The DDS parameterization screens are shown in Figure 20 and Figure 21.

|                                                               | Direct Digital Synthesizer                                                                                                                                                                                      |                     |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| DATA SINE<br>GE COBINE<br>WE RFD<br>A RDY<br>CLK<br>ZGLR SOLR | Component Name bigboo<br>Output Width 16 Valid Range -<br>Function Memory Ty<br>Sine Cosine Sine and Cosine<br>Negative Sine Negative Cosine<br>Handshaking Options Layout Create I<br>ROY Pin RFD Pin Create I | ned ROM C Block ROM |

| Display Core Viewer after Genera                              | dine.                                                                                                                                                                                                           |                     |

Figure 20: DDS parameterization screen - field 1.

|                                                                | Direct Digita                                                                                                                                                                                                                                                                                       | Marcontact  <br>Direct Digital Synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DATA SINE<br>OE COSINE<br>WE RFD<br>A RDY<br>CLK<br>//CLR SOLR | Registers         Data Width         16       Valid Range 3.16         Phase Accumulator         Accumulator Latency         Zero Cycle         Width         16         Valid Range 3.32    Phase Increment          Register         Constant         O         Olick Enable         Clock Enable | Phase Angle<br>Width 4 Valid Range 3.10<br>Pipelined<br>Pipelined<br>Latency 1<br>Latency 1<br>Phase Offset<br>Constant<br>Constant<br>Constant<br>Constant<br>Constant<br>Constant<br>Constant<br>Constant<br>Constant<br>Constant<br>Constant<br>Phase Offset<br>Phase |  |  |

| Display Core Viewer after Genera                               | ăon                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

#### Figure 21: DDS parameterization screen - field 2.

The customization parameter definitions are:

- Component Name: The user-defined DDS component name.

- **Output Width:** The output precision of the *SINE* and *COSINE* outputs. Depending on the customization selection, only one of these ports might be present on a component. If both the sine and cosine components are present, the bit precision for each signal will be the same.

- Function: The DDS may have a quadrature output (sine and cosine), or a single output port either sine or cosine. In addition, the sign of the output signal(s) can be defined using the *Negative Sine* and *Negative Cosine* checkboxes. For example, if the quadrature output option is selected (*Sine and Cosine* GUI option) and both the *Negative Sine* and *Negative Cosine* boxes are unchecked, then the output signal *s*(*n*) is

$$s(n) = e^{j\Theta(n)} = \cos\Theta(n) + j\sin\Theta(n) \quad (13)$$

If the Negative Sine box had been checked, the output signal is defined by

$$s(n) = e^{-j\Theta(n)} = \cos\Theta(n) - j\sin\Theta(n) \quad (14)$$

• **Memory Type:** This field controls the location of the DDS trigonometric lookup table. When the *Distributed ROM* is selected, the table is placed in distributed

memory. If the *Block ROM* option is selected, the table will be implemented using FPGA block memory.

- **Data Width:** The *Data Width* field defines the bit precision of the *DATA* port. This port sources the *PINC* and *POFF* registers.

- **Phase Offset:** The phase offset value shown in Figure 17 can be sourced from a register or it can be a constant that is defined when the Core is customized. This function can be completely omitted by selecting *None.* When the Register or Constant option is selected, the bit precision is determined by the *DATA* port. Using the *Register* option, the phase offset value can be changed on-line using the Core *DATA* port and associated control signals.

If the *Constant* option is selected, the value in the textbox is used as the phase offset value. Just like the *Register* option, this is an unsigned value that, if necessary, is zero-extended before it is added to the high-precision phase angle supplied by the phase accumulator.

The bit field range of the phase offset is always less than or equal to the precision carried by the phase accumulator.

• **Phase Increment:** The phase increment can be sourced from either a register or a constant. This is an unsigned value that, if necessary, is zero-extended before it is applied to the summing junction at the input of the phase accumulator. The phase increment value can be changed on-line using the Core *DATA* port and associated control signals.

If the *Constant* option is employed, the value in the textbox will define the output frequency of a fixed-frequency synthesizer.

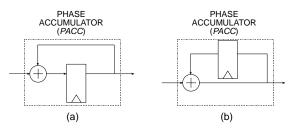

• **Phase Accumulator:** Phase accumulator precision. This field defines the precision of the *PACC* register (Figure 17). The location of the register in the phase accumulator is controlled by the latency selection options. When the *one-cycle* latency option is selected, the phase accumulator will be as shown in Figure 22(a). When the *zero-cycle* option is selected, the arrangement in Figure 22(b) is employed.

Phase Angle: This is the number of bits allocated to the quantized phase angle - <sup>B</sup><sub>Θ</sub>(n) in Figure 17.

$B_{\Theta(n)}$  is the number of address bits used to address the sine/cosine lookup table. This value defines the depth of the lookup table.

- **Clock Enable:** The Core can have an optional clock enable port.

- Handshaking Options: Optional handshaking ports -*RDY* and *RFD* - can be included on the Core. The *RFD* output signal is simply tied to VCC and is an optional port that can be included for compatibility with other Xilinx LogiCores that employ this style of dataflow inferface. As shown in Figure 19, the *RDY* output signal identifies when valid sine/cosine samples appear on these ports after the Core is started from rest — either after system power-on or a reset (synchronous or asynchronous). Any type of Core reset will cause RDY to be removed (*RDY*=0).

- Layout: This checkbox controls whether a relationally placed MACRO (RPM) or a module with no placement information is generated. When checked, an RPM is produced. The RPM option is supported only for the distributed ROM implementation.

## **XCO File Parameters**

The parameters supplied via the filter GUI are captured and logged to the *.xco* file. The full name of this file is simply the Component Name with an *.xco* file extension. Table 2 defines the *.xco* file parameter names and range specifications.

| Parameter Name           | Definition                                                                                 | Range                                            |

|--------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------|

| BusFormat                | Controls the notation employed for identify-<br>ing buses in the output edif netlist file. | {BusFormatAngleBracket   BusFormat-<br>Paren}    |

| SimulationOutputProducts | Core HDL simulation selection — either VHDL or Verilog.                                    | {VHDL   VERILOG}                                 |

| ViewlogicLibraryAlias    | Pathname to Viewlogic directory                                                            | Valid path name for the user's operating system. |

| Parameter Name        | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Range                                                                        |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| XilinxFamily          | The FPGA target device family.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | {Virtex   Spartan2}                                                          |

| DesignFlow            | HDL flow specifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | {VHDL   VERILOG}                                                             |

| FlowVendor            | Design flow vendor information.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | {Other   Synplicity   Exemplar   Synopsis  <br>Foundation}                   |

| function              | The DDS may be customized to provide a sine only output ( <i>function=Sine</i> ), cosine only output ( <i>function=Cosine</i> ) or both sine and cosine (quadrature) outputs ( <i>function=Sine_and_Cosine</i> ).                                                                                                                                                                                                                                                                     | {Sine   Cosine   Sine_and Cosine}                                            |

| data_width            | The bit precision of the input <i>DATA</i> port. The <i>DATA</i> port is a time shared bus that is used for supplying values to the phase increment ( <i>PINC</i> ) and phase offset ( <i>POFF</i> ) registers. The maximum allowable number of bits for this port must be less than or equal to the field width defined for the phase accumulator ( <i>PACC</i> ). The field width of the <i>PINC</i> and <i>POFF</i> registers is inherited from the width of the <i>DATA</i> port. | [3,,32]                                                                      |

| phase_increment       | The phase increment value, that is the delta<br>phase increment supplied to the phase accu-<br>mulator, may be sourced (by the PACC) from<br>either a register (phase_increment-=REG) or<br>it may be a constant (phase_increment=Con-<br>stant).                                                                                                                                                                                                                                     | {REG   Constant}                                                             |

| phase_increment_value | When <i>phase_increment=Constant</i> the DDS<br>produces a fixed output frequency as defined<br>by the <i>phase_increment_value</i>                                                                                                                                                                                                                                                                                                                                                   | Any hexadecimal value not to exceed the range supported by <i>data_width</i> |

| phase_offset          | As shown in Figure 17 an optional phase off-<br>set can be introduced at the output of the<br>phase accumulator. When<br>phase_offset=REG this value is supplied by<br>a register. When phase_offset=Constant the<br>phase offset is a constant that is supplied by<br>the phase_offset_value field when the Core<br>is elaborated. If phase_offset=None no<br>phase offset is included in the datapath.                                                                              | {REG   Constant   None }                                                     |

| phase_offset_value    | Initialization value for the phase offset con-<br>stant. The field width of this value must be<br>less than or equal to the number of bits spec-<br>ified for the phase accumulator. The field<br>width of the phase offset value is always the<br>same as that of the phase offset value.                                                                                                                                                                                            | [3,,32]                                                                      |

| accumulator_width     | The field width for the phase accumulator ( <i>PACC</i> ).                                                                                                                                                                                                                                                                                                                                                                                                                            | [3,,32]                                                                      |

#### Table 2: XCO File Parameter Names, Definitions, and Range Specifications (Cont.)

## Table 2: XCO File Parameter Names, Definitions, and Range Specifications (Cont.)

| Parameter Name      | Definition                                                                                                                                                                                                                                                                                                        | Range                                                                                                                                               |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| accumulator_latency | The user may control the position of the reg-<br>ister in the phase accumulator. When<br>accumulator_register=ONE_CYCLE the reg-<br>ister location shown in Figure 22(a) is em-<br>ployed. When<br>accumulator_register=ZERO_CYCLE the<br>register location shown in Figure 22(b) is em-<br>ployed.               |                                                                                                                                                     |

| phase_angle_width   | This is the number of bits allocated to the quantized phase angle - $B_{\Theta(n)}$ in Figure 17.<br>$B_{\Theta(n)}$ is the number of address bits used to address the sine/cosine lookup table. This value defines the depth of the lookup table.                                                                | [3,,16]                                                                                                                                             |

| aclr_pin            | Asynchronous clear. When <i>aclr_pin=true</i> an asychronous reset port is included on the component. When <i>aclr_pin=false</i> the asy-chronous reset port suppressed.                                                                                                                                          | {true   false}                                                                                                                                      |

| component_name      | Textbox that defines the DDS component name.                                                                                                                                                                                                                                                                      | Any valid file name for the user's operating system consisting of the letters az, 09 and '_'. The component name may be a maximum of 32 characters. |

| pipelined           | This parameter controls the degree of pipe-<br>lining employed in the sine/cosine lookup ta-<br>ble. When set to <i>true</i> the table is fully<br>pipelined. When set to <i>false</i> the minimum<br>(zero for the case of a distributed ROM) num-<br>ber of pipeline registers are used.                        | {true   false}                                                                                                                                      |

| memory_type         | The sine/cosine samples can be stored in<br>distributed or block memory. When<br><i>memory_type=Block_ROM</i> the samples are<br>stored in Block memory. When<br><i>memory_type=Distributed_ROM</i> distributed<br>memory is used.                                                                                | {Block_ROM   Distributed_ROM}                                                                                                                       |

| negative_sine       | Only applicable if a sine port has been spec-<br>ified for the particular Core instance.<br>When <i>negative_sine=false</i> , the signal pre-<br>sented at the <i>sine</i> port is sin $\theta(n)$ . When<br>negative_sine=true, the signal presented at<br>the sine port is - sin $\theta(n)$ .                  | {true   false}                                                                                                                                      |

| negative_cosine     | Only applicable if a cosine port has been<br>specified for the particular Core instance.<br>When <i>negative_cosine=false</i> , the signal pre-<br>sented at the <i>cosine</i> port is $\cos \theta(n)$ . When<br><i>negative_cosine=true</i> , the signal presented<br>at the cosine port is $-\cos \theta(n)$ . |                                                                                                                                                     |

| output_width        | The output precision of the SINE and/or the COSINE output ports.                                                                                                                                                                                                                                                  | [4,,32]                                                                                                                                             |

| Parameter Name | Definition                                                                                                                                                                          | Range          |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| sclr_pin       | Synchronous clear. When <i>sclr_pin=true</i> a sy-<br>chronous reset port is included on the com-<br>ponent. When <i>sclr_pin=false</i> the sychronous<br>re reset port suppressed. | {true   false} |

| clock_enable   | Clock enable. When <i>ce_enable=true</i> a clock<br>enable port is included on the component.<br>When <i>clock_enable=false</i> the clock enable<br>port suppressed.                | {true   false} |

| rdy_pin        | When <i>rdy_pin=true</i> the DDS Core includes a<br><i>RDY</i> output signal. If <i>rdy_pin=false</i> the <i>RDY</i><br>port is suppressed.                                         | {true   false} |

| rfd_pin        | When <i>rfd_pin=true</i> the DDS Core includes a <i>RFD</i> output signal. If <i>rfd_pin=false</i> the <i>RFD</i> port is suppressed.                                               | {true   false} |

| create_rpm     | When create_rpm=true a Core with embed-<br>ded physical placement information is gener-<br>ated. If create_rpm=false the Core is<br>generated without placement data.               | {true   false} |

Table 2: XCO File Parameter Names, Definitions, and Range Specifications (Cont.)

Figure 23 is an example .xco file.

# Xilinx CORF Generator 3.1i # Username = rslous # COREGenPath = c:\visualcafe\projects # ProjectPath = H:\newcore # ExpandedProjectPath = H:\newcore SET BusFormat = BusFormatParen SET SimulationOutputProducts = VHDL SET ViewlogicLibraryAlias = primary SET XilinxFamily = Virtex SET DesignFlow = VHDL SET FlowVendor = Synplicity SELECT Direct\_Digital\_Synthesizer Virtex Xilinx,\_Inc. 2.0 CSET rdy\_pin = true CSET aclr\_pin = false CSET phase\_increment = Register CSET latency = One\_Cycle CSET component\_name = test

Figure 23: Example DDS .xco file.

# **DDS Design Example 1**

Consider a DDS that is to satisfy the following requirements

frequency resolution  $\Delta f = 0.25$  Hz minimum spur suppression S = 70 dB  $f_{\rm clk} = 120$  MHz

Quarature output:  $s(n) = e^{-j(\Theta(n)+\phi)} \cos(\Theta(n) + \phi) - \sin(\Theta(n) + \phi))$ where the phase offset  $\phi = +\pi/4$  radians

The field width of the phase accumulator (PACC in Figure 17) defines the DDS frequency resolution according to

CSET data\_width = 16 CSET rfd pin = true CSET pipelined = true CSET outputs\_required = Sine\_and\_Cosine CSET phase offset = None CSET memory\_type = Distributed\_ROM CSET negative\_sine = false CSET accumulator width = 16 CSET phase\_angle\_width = 4 CSET negative\_cosine = false CSET output\_width = 16 CSET sclr\_pin = false CSET clock\_enable = false CSET phase increment value = 0 CSET phase\_offset\_value = 0 CSET create\_rpm = true GENERATE

$$\Delta f = \frac{f_{clk}}{2^{B_{\theta(n)}}} \tag{15}$$

Therefore, the bit-precision for the PACC register is

$$B_{\theta(n)} = \log_2 \left[ \frac{f_{\text{clk}}}{\Delta f} \right]$$

$$= \left[ \log_2 \frac{120 \times 10^6}{0.25} \right]$$

$$= \left[ 28.838459 \right]$$

$$= 29 \text{ bits}$$

(16)

The spur suppression requirement is the dominant consideration when selecting the depth of the sine/cosine lookup table. Of course, the table samples must be specified with an appropriate precision to support this value. As noted in an earlier section of this document, each sine/cosine table address bit contributes approximately 6 dB of spur suppression. To meet the -70 dB spur level, the number of address bits required is

$$B_{\Theta(n)} = \left\lceil \log_2 \frac{70}{6} \right\rceil$$

(17)

=  $\left\lceil 11.66\dot{6} \right\rceil$

= 12 bits

The table depth N is

$$N = 2^{B_{\Theta(n)}} = 2^{12} = 4096 \text{ samples} \quad (18)$$

The phase offset value POFF is determined as

$$POFF = N \frac{\phi}{360}$$

(19)

= 4096  $\frac{45}{360}$

= 512<sub>10</sub>

To generate a 10.2 MHz output signal the phase increment would be

$$\Delta \theta = \frac{f_{\text{out}} 2^{B_{\Theta(n)}}}{f_{\text{clk}}}$$

(20)

=  $\frac{10.2 \times 10^6 \times 2^{12}}{120 \times 10^6}$

= 348.16

This value must be expressed in the same format as the phase accumulator. The phase accumulator is a 29-bit word. Of these bits, the top 12 are interpreted as the integer field and the bottom 17 as the fractional component. That is, a 12.17 number. The phase increment value is therefore  $\Delta \theta = 000101011100.00101000111101100_{2}$ .

Figure 24 is a spectral plot of the 10.2 MHz output signal. Observe that the highest spur meets the 70 dB spur suppression requirement.

Figure 24: DDS example 1. 10.2 MHz output tone. The highest spur is below the required 70 dB suppression value.

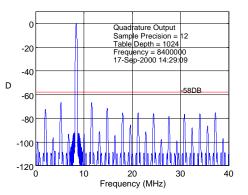

## **DDS Design Example 2**

Consider a DDS that is to satisfy the following requirements

frequency resolution  $\Delta f = 0.3$  Hz minimum spur suppression S = 58 dB  $f_{\rm clk} = 80$  MHz

Quarature output:  $s(n) = e^{-j(\Theta(n)+\phi)} \cos(\Theta(n) + \phi) - \sin(\Theta(n) + \phi))$ where the phase offset  $\phi = -50$  degrees

The field width of the phase accumulator (PACC in Figure 17) defines the DDS frequency resolution according to

$$\Delta f = \frac{f_{\text{clk}}}{2^{B_{\theta(n)}}} \tag{21}$$

Therefore, the bit-precision for the PACC register is

$$B_{\theta(n)} = \log_2 \left[ \frac{f_{\text{clk}}}{\Delta f} \right]$$

$$= \left[ \log_2 \frac{80 \times 10^6}{0.3} \right]$$

$$= \lceil 27.99046 \rceil$$

$$= 28 \text{ bits}$$

(22)

The spur suppression requirement is the dominant consideration when selecting the depth of the sine/cosine look-up table. Of course, the table samples must be specified with an appropriate precision to support this value. As noted in an earlier section of this document, each sine/cosine table address bit contributes approximately 6 dB of spur suppression. To meet the -58 dB spur level, the number of address bits required is

$$B_{\Theta(n)} = \left\lceil \log_2 \frac{58}{6} \right\rceil$$

=  $\left\lceil 9.666 \right\rceil$  (23)

= 10 bits

The table depth N is

$$N = 2^{B_{\Theta(n)}} = 2^{10} = 1024$$

samples (24)

In this example the required phase offset has been specified as a negative value. The DDS Core supports only positive phase offsets. This is, of course, not a problem because a phase angle of -50 degrees is the same as +315 degrees.

The phase offset value POFF is determined as

POFF =

$$N \frac{\phi}{360}$$

=  $1024 \frac{315}{360}$  (25)

=  $896_{10}$

To generate an 8.4 MHz output signal, the phase increment would be

$$\Delta \theta = \frac{f_{\text{out}} 2^{B_{\Theta(n)}}}{f_{\text{clk}}}$$

$$= \frac{8.4 \times 10^{6} \times 2^{10}}{80 \times 10^{6}}$$

$$= 107.52$$

(26)

This value must be expressed in the same format as the phase accumulator. The phase accumulator is a 28-bit word. Of these bits, the top 10 are interpreted as the integer field and the bottom 18 as the fractional component. That is, a 10.18 number. The phase increment value is therefore  $\Delta \theta = 0001000111.101011100001010010_2$ .

Figure 25 is a spectral plot of the 8.4 MHz output signal. Observe that the highest spur meets the 58 dB spur suppression requirement.

Figure 25: DDS example 2. 8.4 MHz output tone. The highest spur is below the required 58 dB suppression value.