# **Compact UART**

January 10, 2000

**Product Specification**

## CAST, Inc.

24 White Birch Drive

Pomona, New York 10907 USA

Phone: +1 914-354-4945

Fax: +1 914-354-0325

E-Mail: info@cast-inc.com

URL: www.cast-inc.com

#### **Features**

- Supports 4000X, 9500, Spartan, Spartan<sup>™</sup>-II, Virtex<sup>™</sup>, and Virtex<sup>™</sup>-E devicesCompact UART

- 8-bit characters

- TxC / RxC (16 times the desired output baud rate)

- 1 start bit / 1 stop bit

- · Polling and interrupt modes

- Flexibility for adding other features

#### AllianceCORE™ Facts **Core Specifics** See Table 1 Provided with Core Documentation Core Design Document Design File Formats EDIF netlist, .ngo, Verilog Source RTL available extra Constraints File C\_UART.ucf Verification VHDL testbench, test vectors Instantiation VHDL, Verilog **Templates** Reference Designs & None **Application Notes** Additional Items None Simulation Tool Used 1076 compliant, VHDL simulator, Verilog simulator Support Support provided by CAST, Inc.

## **Applications**

The C\_UART core is used in serial data communications applications.

**Table 1: Core Implementation Data**

| Supported<br>Family | Device<br>Tested | Macrocells <sup>2</sup> | Product<br>Terms <sup>2</sup> | <b>I/O</b> <sup>1</sup> | Performance <sup>2</sup> (MHz) | Special<br>Features | Xilinx<br>Tools |

|---------------------|------------------|-------------------------|-------------------------------|-------------------------|--------------------------------|---------------------|-----------------|

| 9500                | 9572-7           | 68                      | 163                           | 26                      | 100³                           | None                | M1.5            |

| 9500XL              | 9572XL-5         | 68                      | 161                           | 26                      | 178.5 <sup>3</sup>             | None                | M1.5            |

| Supported Family | Device<br>Tested | CLBs⁵ | Clock<br>IOBs | IOBs <sup>1</sup> | Performance<br>(MHz) | Special<br>Features | Xilinx<br>Tools |

|------------------|------------------|-------|---------------|-------------------|----------------------|---------------------|-----------------|

| 4000XL           | 4013XL-08        | 43    | 2             | 24                | 94                   | None                | M1.5i           |

| Spartan          | S30-4            | 46    | 2             | 24                | 65                   | None                | M1.5i           |

| Virtex           | V50-6            | 424   | 2             | 24                | 142                  | None                | M1.5i           |

#### Notes:

- 1. Assuming all core I/O are routed off-chip.

- 2. CPLD figures stated are optimized for density.

- 3. Max CPLD performance measured for CLK16 input.

- 4. Utilization numbers for Virtex are in CLB slices.

- 5. Optimized for speed.

January 10, 2000 3-1

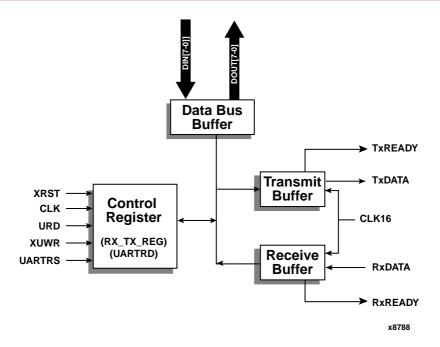

Figure 1: C\_UART Compact UART Block Diagram

## **General Description**

The C\_UART core is a generic universal asynchronous receiver/transmitter (UART) and can be used to implement a peripheral data communication device. The designer can program the core with an 8-bit CPU.

# **Functional Description**

The C\_UART core is partitioned into modules as shown in Figure 1 and described below.

## **Control Register**

#### RX\_TX\_REG - UART R/W Data Register

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| d | d | d | d | d | d | d | d |

The Data Register is used for reading data from the receiver or writing data to the transmitter. This register is cleared during reset.

#### **UARTRD - UART Read STATUS Register**

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | n | n |

| Bit 0 RxREADY | n=0 | Rx BUFFER FULL  |

|---------------|-----|-----------------|

| DILU KAKLADI  | n=1 | Rx BUFFER EMPTY |

| Bit 1 TxREADY | n=0 | Tx BUFFER EMPTY |

| DICTIXICADI   | n=1 | Tx BUFFER FULL  |

The Status Register maintains information about the current operational status of the UART. During reset, bit 0 of the register is set, and bit 1 is cleared.

#### **Data Bus Buffer**

The Data Bus Buffer is used to interface with the external Data Bus. Its contents are either written to the RX\_TX\_REG or are loaded from it depending on the state of the Control Register.

#### **Transmit Buffer**

The Transmit Buffer is used to hold the data being transmitted out of the C\_UART. It is loaded from the Data Bus Buffer. The data is output serially to the TxDATA pin by the data clock (CLK16).

#### **Receive Buffer**

The Receive Buffer is used to hold data as it comes into the C\_UART via the RxDATA pin input serially by the data clock (CLK16).

3-2 January 10, 2000

### **Core Modifications**

The C\_UART core can be customized to include:

- · Different Character length

- Parity

- · Different Start/Stop bits

- · Modem Functions

Please contact CAST directly for any required modifications.

#### **Pinout**

The pinout of the C\_UART core has not been fixed to specific FPGA I/O, allowing flexibility with a users application. Signal names are shown in the block diagram in Figure 1, and in Table 2.

#### **Verification Methods**

The C\_UART core's functionality has been extensively tested with a VHDL testbench and a large number of test patterns.

# Recommended Design Experience

The user must be familiar with HDL design methodology as well as instantiation of Xilinx netlists in a hierarchical design environment.

## **Ordering Information**

The C\_UART core is available from CAST, Inc. Please contact CAST, Inc. directly for pricing and information.

The C\_UART core is licensed from Moxsyn S.R.L.

#### Related Information

Xilinx, Inc.

## Xilinx Programmable Logic

For information on Xilinx programmable logic or development system software, contact your local Xilinx sales office, or:

2100 Logic Drive

San Jose, CA 95124

Phone: +1 408-559-7778

Fax: +1 408-559-7114

URL: www.xilinx.com

**Table 2: Core Signal Pinout**

| Signal    | Signal Direction | Description                                               |

|-----------|------------------|-----------------------------------------------------------|

| XRST      | Input            | Master Reset                                              |

| CLK       | Input            | System Clock                                              |

| URD       | Input            | Decoded UART Read                                         |

| XUWR      | Input            | Decoded UART Write Control for Transmitter Register       |

| UARTRS    | Input            | Register Select 0 = Status Register 1 = R/W Data Register |

| DIN[7:0]  | Input            | Input Data Bus                                            |

| DOUT[7:0] | Output           | Output Data Bus                                           |

| TxREADY   | Output           | Transmitter Empty (ready to accept new character)         |

| TxDATA    | Output           | Transmitter Data                                          |

| CLK16     | Input            | Transmit/Receive Master Clock                             |

| RxDATA    | Input            | Receiver Data                                             |

| RxREADY   | Output           | Receiver Ready (character ready to be transferred to CPU) |

For general Xilinx literature, contact:

Phone: +1 800-231-3386 (inside the US)

+1 408-879-5017 (outside the US)

E-mail: literature@xilinx.com

For AllianceCORE™ specific information, contact:

Phone: +1 408-879-5381 E-mail: alliancecore@xilinx.com

URL: www.xilinx.com/products/logicore/alliance/

tblpart.htm

January 10, 2000 3-3