#### **CONV ENC Convolutional** Encoder

January 10, 2000

# **CSELT S.p.A**

Via G. Reiss Romoli, 274 I-10148 Torino, Italy Phone: +39 011 228 7165 +39 011 228 7003 Fax: E-mail: viplibrary@cselt.it URL: www.cselt.it

# Features

- Supports Spartan, Spartan<sup>™</sup>-II, Virtex<sup>™</sup>, and ٠ Virtex<sup>™</sup>-E devices

- Encoder for convolutional codes

- . Customizable VHDL source code available, allowing generation of different netlist versions

- ٠ Customized testbench for pre- and post-synthesis verification supplied with the module

- Core customization:

- Convolutional code definition parameters: Code rate; Code generation vectors; Code constraint length

- Input data bus width

- Output data period -

# **Applications**

· Encoding of convolutional codes

**Product Specification**

| AllianceCORE            |                            |                      |

|-------------------------|----------------------------|----------------------|

| C                       | ore Specifics <sup>1</sup> |                      |

| Supported Family        | Spartan                    | Virtex               |

| Device Tested           | S10-3                      | V50-6                |

| CLB Slices <sup>2</sup> | 12                         | 16                   |

| Clock IOBs              | 1                          | 1                    |

| IOBs <sup>3</sup>       | 11                         | 11                   |

| Performance (MHz)       | 67                         | 144                  |

| Xilinx Tools            | M1.5i/M2.1i                | M1.5i/M2.1i          |

| Special Features        | None                       | None                 |

| Pro                     | vided with Core            |                      |

| Documentation           |                            | User Manua           |

| Design File Formats     | EDIF r                     | netlist, XNF netlist |

|                         | VHDL sou                   | rce available extra  |

| Constraints File        | TOP_C                      | CONV_ENC_nl.nc       |

| Verification            |                            | VHDL testbench       |

| Instantiation           |                            | VHDL, Verilog        |

| Templates               |                            |                      |

| Reference Designs &     |                            | None                 |

| Application Notes       |                            |                      |

| Additional Items        |                            | None                 |

|                         | lation Tool Used           | k                    |

| Synopsys VSS            |                            |                      |

Design and customization support provided by CSELT

Notes:

- 1. Data refer to the following customization:

- Code parameters: rate = 1/2, constraint length = 5, generation vectors =  $(23)_8, (33)_8;$

- Input data bus width = 4;

- Output data period = 2 clock cycles.

- 2. Utilization numbers for Virtex are in CLB slices

- 3. Assuming all core I/Os are routed off-chip

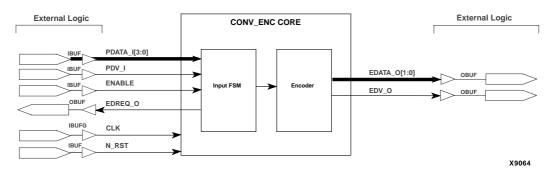

#### Figure 1: Convolutional Encoder Block Diagram

# **General Description**

This core implements an encoder for convolutional codes. The core encodes a specific convolutional code, with user defined constraint length, rate and generation vectors. User customizable core features also include the input bus width and the encoder output period.

The Absolute Maximum ratings, Operating Conditions, DC Electrical Specifications and Capacitances depend on the Xilinx device selected for implementation and can be retrieved from the corresponding Xilinx datasheet.

# **Functional Description**

The internal architecture of the Convolutional Encoder core is shown in Figure 1. A brief description of the operation of each module follows.

#### Input FSM

The input FSM handles the serialization of the incoming parallel data flow and the data request signal.

#### Encoder

The encoder performs convolutional encoding of the serialized data flow.

#### **Pinout**

The pinout of this core has not been fixed to a specific FPGA I/O allowing flexibility with a user's application. Signal names are shown in the block diagram in Figure 1 and described in Table 1.

# **Core Modifications**

CSELT provides netlist customized to user's requirements. The Convolutional Encoder core source code is parametric. Parameters shown in Table 2 are implemented as a set of generics in the synthesizable VHDL source code of the core. Parameters allow the user to specify some architectural and functional features, so as to adapt the netlist to a specific design or application.

# **Verification Methods**

Extensive functional (pre-synthesis) and timing (post-synthesis) simulation has been performed for different values of the core parameters, using the Synopsys VSS simulator. Simulation scenarios (including data and command files) and parametric test bench used for design verification are provided with the core.

# Recommended Design Experience

Experience with the Xilinx design flow is recommended to the users of the netlist version of the core. For the source code version, users should also be familiar with the Synopsys FPGA synthesis tools (VHDL Compiler, FPGA Compiler) and simulator (VSS).

# **Ordering Information**

The CONV\_ENC core is provided under license by CSELT S.p.A. for use in Xilinx programmable logic devices. Please contact CSELT S.p.A. for information about pricing, terms and conditions of sale.

CSELT S.p.A. reserves the right to change any specification detailed in this document at any time without notice, and assumes no responsibility for any error in this document.

All trademarks, registered trademarks, or servicemarks are property of their respective owners.

#### **Table 1: Core Signal Pinout**

| Signal       | Signal Direction | Description           |

|--------------|------------------|-----------------------|

| PDATA_I[3:0] | Input            | Parallel data input:  |

|              |                  | Port size equal to    |

|              |                  | DSIZE, where DSIZE    |

|              |                  | is a generic          |

| PDV_I        | Input            | Data valid input      |

| ENABLE       | Input            | Encoder enable        |

| EDREQ_O      | Output           | Encoder data request  |

| EDATA_O[1:0] | Output           | Encoded data output:  |

|              |                  | Port size is equal to |

|              |                  | N, where N is a ge-   |

|              |                  | neric                 |

| EDV_O        | Output           | Data valid output     |

| CLK          | Input            | Master clock          |

| N_RST        | Input            | Asynchronous reset    |

#### Table 2: Core Parameters (VHDL Generics)

| Parameter           | Description             |

|---------------------|-------------------------|

| Ν                   | Inverse code rate       |

| CONST_LENGTH        | Code constraint length  |

| POLGENx (x=0,1,2,3) | Code generation vectors |

| DSIZE               | Input data size         |

| OUTPUT_PERIOD       | Output period           |

# **Related Information**

#### Xilinx Programmable Logic

For information on Xilinx programmable logic or development system software, contact your local Xilinx sales office, or:

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 Phone: +1 408-559-7778 Fax: +1 408-559-7114 URL: www.xilinx.com

For general Xilinx literature, contact:

| Phone:  | +1 800-231-3386 (inside the US)  |

|---------|----------------------------------|

|         | +1 408-879-5017 (outside the US) |

| E-mail: | literature@xilinx.com            |

For AllianceCORE<sup>™</sup> specific information, contact:

| Phone: + | -1 408-879-5381 |

|----------|-----------------|

|----------|-----------------|

| E-mail: | alliancecore@xilinx.com |

|---------|-------------------------|

|         |                         |

URL: www.xilinx.com/products/logicore/alliance/ tblpart.htm

# Convolutional Encoder

To: CSELT S.p.A.

FAX: +39 011 228 7003

E-mail: viplibrary@cselt.it

CSELT configures and ships Xilinx netlist versions of the Convolutional Encoder core customized to your specification. Please fill out and fax this form so CSELT can respond with an appropriate quotation that includes performance and density metrics for the target Xilinx FPGA.

#### Implementation Issues

1. Code rate:

2. Constraint length:

3. Coding polynomial:

4. Input data size:

5. Output period:

| From:           |

|-----------------|

| Company:        |

| Address:        |

| City,State,Zip: |

| Country:        |

| Phone:          |

| FAX:            |

| E-mail:         |

#### **Business Issues**

1. Indicate timescales of requirement:

- \_\_\_\_\_ date for decision

- \_\_\_\_\_ date for placing order

- \_\_\_\_\_ date of delivery

2. Indicate your area of responsibility:

- \_\_\_\_\_ decision maker

- \_\_\_\_\_ budget holder

- \_\_\_\_\_ recommender

3. Has a budget been allocated for the purchase? Yes \_\_\_\_\_ No \_\_\_\_\_

4. What volume do you expect to ship of the product that will use this core? \_\_\_\_\_

- 5. What major factors will influence your decision?

- \_\_\_\_\_ cost

- \_\_\_\_\_ customization

- \_\_\_\_\_ testing

- \_\_\_\_\_ implementation size

6. Are you considering any other solutions?