# **DSD Distributed Sample Descrambler**

January 10, 2000

**Product Specification**

### **CSELT S.p.A**

Via G. Reiss Romoli, 274 I-10148 Torino, Italy

Phone: +39 011 228 7165 Fax: +39 011 228 7003 E-mail: viplibrary@cselt.it URL: www.cselt.it

#### **Features**

- Supports Spartan, Spartan<sup>™</sup>-II, Virtex<sup>™</sup>, and Virtex<sup>™</sup>-E devices

- Distributed sample descrambler for cell-based data transmission

- Customizable VHDL source code available, allowing generation of different netlist versions

- Can implement ITU-T I.432 descrambler for standard 53-bit ATM cells

- Can implement custom descrambler for proprietary format ATM cells

- Customized testbench for pre- and post-synthesis verification supplied with the module

- · Core customization:

- 8/16 bits interface data width

- ATM cell length

- ATM cell header length and position

- Feedback and output polynomials of the descrambling sequence generator

- Reset value of the descrambling sequence generator

## **Applications**

· Physical layer ATM circuits

| AllianceCORE™ Facts                                |                   |                      |

|----------------------------------------------------|-------------------|----------------------|

|                                                    |                   |                      |

| Supported Family                                   | Spartan           | Virtex               |

| Device Tested                                      | S05-3             | V50-6                |

| CLB Slices <sup>2</sup>                            | 97                | 109                  |

| Clock IOBs                                         | 1                 | 1                    |

| IOBs <sup>3</sup>                                  | 28                | 28                   |

| Performance (MHz)                                  | 42                | 74                   |

| Xilinx Tools                                       | M1.5i/M2.1i       | M1.5i/M2.1i          |

| Special Features                                   | None              | None                 |

| Pro                                                | vided with Core   |                      |

| Documentation                                      |                   | User Manual          |

| Design File Formats                                | EDIF n            | etlist, XNF netlist, |

|                                                    | VHDL sour         | ce available extra   |

| Constraints File                                   |                   | TOP_DSD_nl.ncf       |

| Verification                                       |                   | VHDL testbench       |

| Instantiation                                      |                   | VHDL, Verilog        |

| Templates                                          |                   |                      |

| Reference Designs &                                |                   | None                 |

| Application Notes                                  |                   |                      |

| Additional Items                                   |                   | None                 |

| Simi                                               | ulation Tool Used |                      |

| Synopsys VSS                                       |                   |                      |

|                                                    | Support           |                      |

| Design and customization support provided by CSELT |                   |                      |

#### Notes:

- Data refer to the following customization:

- 8-bit interface

- 53 byte ATM cell

- ATM cell header from byte 1 to 5 inclusive

- Descrambling sequence generator with: feedback polynomial = x<sup>31</sup>+x<sup>28</sup>+1, output polynomial = x<sup>31</sup>+x<sup>28</sup>, reset value = 1

- 2. Utilization numbers for Virtex are in CLB slices

- 3. Assuming all core I/Os are routed off-chip

January 10, 2000 3-1

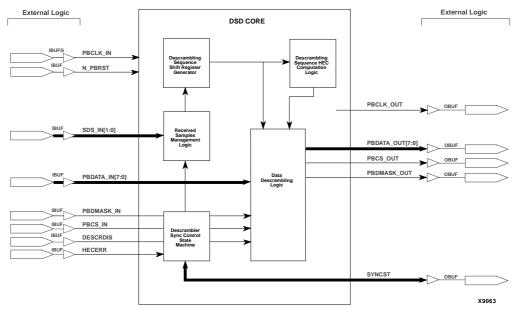

Figure 1: DSD Block Diagram

### **General Description**

The Distributed Sample Descrambler (DSD) core decodes a scrambled ATM cell stream by modulo-2 addition of the cell bits with a pseudo-random sequence identical to, and synchronized with the sequence used by the scrambler for encoding the stream. This core is the companion of the Distributed Sample Scrambler (DSS) core, which encodes a cell-based stream by modulo-2 addition of the cell bits with a pseudo-random sequence.

To allow synchronization of the descrambler to the scrambler, samples of the scrambling sequence are sent from the DSS to the DSD. In this implementation, two sequence samples, taken at half-cell distance are carried by the two most significant bits of the Header Error Correction (HEC) field of each ATM cell. While acquiring synchronization, the descrambler compares each received sample to its locally generated counterpart, and performs a correction of the descrambling sequence generator state whenever the two samples differ. After synchronization has been acquired, sample comparison continues for verification purposes, but no further generator state correction is performed.

The Absolute Maximum ratings, Operating Conditions, DC Electrical Specifications and Capacitances depend on the Xilinx device selected for implementation and can be retrieved from the corresponding Xilinx datasheet.

### **Functional Description**

The internal architecture of the DSD core is shown in Figure 1. A brief description of the operation of each module follows.

## **Descrambler Sync Control State Machine**

The Descrambler Sync Control State Machine handles the phase synchronization process of the Descrambling Sequence Shift Register Generator (SRG). The FSM controls the SRG correction process and signals the current synchronization status on the SYNCST outputs.

## Received Samples Management Logic

The Received Samples Management Logic handles the scrambling sequence samples received through the SDS\_IN input. New samples are expected on each input data word that carries a cell HEC field.

This logic also handles the storage of samples of the bit sequence generated by the Descrambling Sequence SRG. Samples are taken at half-cell distance, from the same position in the sequence as those forwarded by the scrambler.

3-2 January 10, 2000

## Descrambling Sequence Shift Register Generator

The Descrambling Sequence SRG generates the descrambling sequence for the received input data stream. The generator, a linear feedback shift register with customizable length, feedback logic and output generation logic, produces one descrambling sequence word per clock cycle. SRG correction performed by modulo-2 addition of a precomputed correction vector to the SRG register content, takes place at times specified by the Sequence Samples Management Logic (when correction is enabled by the Descrambler Sync Control FSM), if the received scrambling sequence sample does not match the corresponding locally generated sample.

## Descrambling Sequence HEC Computation Logic

The Descrambling Sequence HEC Computation Logic computes the Header Error Control codeword corresponding to the cell header descrambling sequence. The computed codeword is forwarded to the Data Descrambling Logic block.

### **Data Descrambling Logic**

The Data Descrambling Logic selects the appropriate descrambling data and generates output data as the modulo-2 sum of descrambling data and input data. The selected descrambling data is the descrambling sequence data from the Descrambling Sequence SRG for every cell byte excluding the HEC. For the HEC byte, the selected descrambling data is the HEC CRC of the header descrambling data sequence (from the Decsrambling Sequence HEC Computation logic block). Aso, the appropriate two bit samples of the descrambling sequence are added modulo-2, to the two most significant bits of the result.

#### **Pinout**

Pinout of the core has not been fixed to specific FPGA I/O allowing flexibility with a user's application. Signal names for this core are shown in Figure 1 and described in Table 1.

### **Core Modifications**

CSELT provides netlist customized to user's requirements. The DSD core is parametric. Parameters shown in Table 2 are implemented as a set of generics in the synthesizable VHDL source code of the core. Parameters allow the user to specify some architectural and functional features, so as to customize the netlist to a specific design or application.

**Table 1: Core Signal Pinout**

| Signal                   | Signal<br>Direction | Description            |  |  |

|--------------------------|---------------------|------------------------|--|--|

| Input Interface          |                     |                        |  |  |

| PBCLK_IN                 | Input               | Data clock             |  |  |

| PBDATA_IN [7:0]          | Input               | Data input; port size  |  |  |

|                          |                     | can be 8/16 bits       |  |  |

|                          |                     | based on DMODE         |  |  |

|                          |                     | generic                |  |  |

| PBDMASK_IN               | Input               | Data mask              |  |  |

| PBCS_IN                  | Input               | Start of cell flag     |  |  |

| Output Interface         |                     |                        |  |  |

| PBCLK_OUT                | Output              | Data clock             |  |  |

| PBDATA_OUT [7:0]         | Output              | Data output; port size |  |  |

|                          |                     | can be 8/16 bits       |  |  |

|                          |                     | based on DMODE         |  |  |

|                          |                     | generic                |  |  |

| PBCS_OUT                 | Output              | Start of cell flag     |  |  |

| PBDMASK_OUT              | Output              | Data mask              |  |  |

| Control and Status Ports |                     |                        |  |  |

| N_PBRST                  | Input               | Reset                  |  |  |

| SDS_IN [1:0]             | Input               | Scrambler data sam-    |  |  |

|                          |                     | ples                   |  |  |

| DESCRDIS                 | Input               | Descrambler disable    |  |  |

| HECERR                   | Input               | HEC error flag         |  |  |

| SYNCST [1:0]             | Output              | Descrambler syn-       |  |  |

|                          |                     | chronization status    |  |  |

**Table 2: Core Parameters (VHDL Generics)**

| Parameter | Description                                                          |

|-----------|----------------------------------------------------------------------|

| DMODE     | Data transfer mode (8/16 bit)                                        |

| NBYTES    | ATM cell size (in bytes)                                             |

| HECFIRST  | First cell byte covered by the HEC field                             |

| HECLAST   | Last cell byte covered by the HEC field (also, HEC field byte)       |

| SRGDEG    | Degree of the SRG feedback polynomial                                |

| SRGPOL    | Binary coefficients of the SRG feedback polynomial                   |

| SRGRVAL   | SRG reset value                                                      |

| SCRPOL    | Binary coefficients of the scrambling sequence generation polynomial |

#### **Verification Methods**

Extensive functional (pre-synthesis) and timing (post-synthesis) simulation has been performed for different values of the core parameters, using the Synopsys VSS simulator. Simulation scenarios (including data and command files) and parametric test bench used for design verification are provided with the core.

January 10, 2000 3-3

The parametric test bench is composed of a programmable ATM cell generator. The generated cell stream is customized; cell generation commands are read from a text file. Cell stream customizability includes header data, (random or user-defined), payload data (random, counter, fixed or user-defined), period and size of transmission holes, error injection (data errors, cell length errors).

# Recommended Design Experience

Experience with the Xilinx design flow and ATM transmission system design is recommended to the users of the netlist version of the core. For the source code version, users should also be familiar with the Synopsys FPGA synthesis tools (VHDL Compiler, FPGA Compiler) and simulator (VSS).

### **Available Support Products**

A copy of the ITU-T Recommendation I.432 *B\_ISDN User-Network Interface — Physical Layer Specification* can be purchased from the International Telecommunication Union. Contact:

International Telecommunication Union Sales and Marketing Service

Place des Nations

CH -1211 Geneva 20, Switzerland

Phone: +41 22 730 6141 Fax: +41 22 730 5194 E-mail: sales@itu.int URL: www.itu.int/publications

## **Ordering Information**

The DSD core is provided under license by CSELT S.p.A for use in Xilinx programmable logic devices. Please contact CSELT S.p.A for information about pricing, terms and conditions of sale.

CSELT S.p.A reserves the right to change any specification detailed in this document at any time without notice, and assumes no responsibility for any error in this document.

All trademarks, registered trademarks, or servicemarks are property of their respective owners.

### **Related Information**

### Xilinx Programmable Logic

For information on Xilinx programmable logic or development system software, contact your local Xilinx sales office, or:

Xilinx, Inc. 2100 Logic Drive

San Jose, CA 95124

Phone: +1 408-559-7778 Fax: +1 408-559-7114 URL: www.xilinx.com

For general Xilinx literature, contact:

Phone: +1 800-231-3386 (inside the US)

+1 408-879-5017 (outside the US)

E-mail: literature@xilinx.com

For AllianceCORE™ specific information, contact:

Phone: +1 408-879-5381 E-mail: alliancecore@xilinx.com

URL: www.xilinx.com/products/logicore/alliance/

tblpart.htm

3-4 January 10, 2000

7. Scrambling sequence generation polynomial:

8. Reset mode (sync/async):

|                                                                                                                                                                                                                | From:                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| To: CSELT S.p.A.                                                                                                                                                                                               | Company:                                                                     |

| FAX: +39 011 228 7003                                                                                                                                                                                          | Address:                                                                     |

| E-mail: viplibrary@cselt.it                                                                                                                                                                                    | City,State,Zip:                                                              |

| CSELT configures and ships Xilinx netlist versions of the                                                                                                                                                      | Country:                                                                     |

| DSD core customized to your specification. Please fill out and fax this form so that CSELT can respond with an appropriate quotation that includes performance and density metrics for the target Xilinx FPGA. | Phone:                                                                       |

|                                                                                                                                                                                                                | FAX:                                                                         |

|                                                                                                                                                                                                                | E-mail:                                                                      |

| Implementation Issues                                                                                                                                                                                          | Business Issues                                                              |

| 1. Data transfer mode (8 bit / 16 bit):                                                                                                                                                                        | 1. Indicate timescales of requirement:                                       |

|                                                                                                                                                                                                                | date for decision                                                            |

|                                                                                                                                                                                                                | date for placing order                                                       |

|                                                                                                                                                                                                                | date of delivery                                                             |

| 2. Cell size (bytes):                                                                                                                                                                                          | 2. Indicate your area of responsibility:                                     |

|                                                                                                                                                                                                                | decision maker                                                               |

|                                                                                                                                                                                                                | budget holder                                                                |

|                                                                                                                                                                                                                | recommender                                                                  |

| 3. First cell byte covered by the HEC:                                                                                                                                                                         | 3. Has a budget been allocated for the purchase?                             |

|                                                                                                                                                                                                                | Yes No                                                                       |

| 4. HEC byte position:                                                                                                                                                                                          | 4. What volume do you expect to ship of the product that will use this core? |

| 5. SRG feedback polynomial:                                                                                                                                                                                    | 5. What major factors will influence your decision?                          |

|                                                                                                                                                                                                                | cost                                                                         |

|                                                                                                                                                                                                                | customization                                                                |

|                                                                                                                                                                                                                | testing                                                                      |

|                                                                                                                                                                                                                | implementation size                                                          |

| 6. SRG reset value:                                                                                                                                                                                            | 6. Are you considering any other solutions?                                  |

January 10, 2000 3-5