# 200 MHz SDRAM Controller Core

Allianas CORETM Facto

January 10, 2000

**Product Specification**

## Rapid Prototypes Inc.

190 Hall Court P.O. Box 5010

Stateline, NV 89449-5010, USA

Phone: +1-775-790-5000, 1-800-227-2743 Fax: +1-781-240-2576, 1-800-278-7662

E-mail: sdram\_core@FPGA.com

URL: www.FPGA.com

## **Features**

- Supports 4000X, Spartan<sup>™</sup>-II, Virtex<sup>™</sup>, and Virtex<sup>™</sup>-E devices

- World's fastest FPGA SDRAM interface. 200MHz.

- Works with SDRAM or SGRAM. Currently 19 bit. address (512K), 32 bit data, but modifiable.

- Uses Auto-precharge mode with a CAS latency of 3 cycles and linear bursts of length 4.

- · Bursts may be aborted for fewer than 4 words.

- Supports 2 or 4 SDRAM banks.

- · Provides 4 commands

- Mode Register Write

- Burst Write

- Burst Read

- Refresh (manual)

- Automatic refresh occurs 15.6µs after the last manual or automatic refresh.

- Manual refresh can be used to ensure continuous SDRAM availability for 15.6μs.

- Throughput of up to 6.4 Gbits/sec per memory chip.

| AllianceCORE M Facts                  |                                                                                                |        |  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------|--------|--|--|

| Core Specifics                        |                                                                                                |        |  |  |

| Supported Family                      | 4000XL/XLA                                                                                     | Virtex |  |  |

| Device Tested                         | 4013XL/A                                                                                       | V100-6 |  |  |

| CLB Slices                            | 62                                                                                             | 129    |  |  |

| Clock IOBs                            | 4                                                                                              | 1      |  |  |

| IOBs <sup>1</sup>                     | 53+92                                                                                          | 53+92  |  |  |

| Performance (MHz)                     | 200                                                                                            | 200    |  |  |

| Xilinx Tools                          | 1.5i                                                                                           | 1.5i   |  |  |

| Special Features                      | 1 BUFG<br>3 BUFGE<br>2 BUFGLS<br>1 OSC                                                         | 1 DLL  |  |  |

| Pro                                   | vided with Core                                                                                |        |  |  |

| Documentation                         | User guide, Design guide,<br>ViewSim .vwf files                                                |        |  |  |

| Design File Formats                   | EDIF netlist                                                                                   |        |  |  |

| Constraints File                      | sdram_controller.ucf                                                                           |        |  |  |

| Verification                          | Functional and timing simulation<br>(with .cmd files),<br>Hardware testing on FastRAM<br>board |        |  |  |

| Instantiation<br>Templates            | VHDL, Verilog, Viewlogic symbol                                                                |        |  |  |

| Reference designs & application notes | None                                                                                           |        |  |  |

|                                       |                                                                                                |        |  |  |

### Simulation Tool Used

Viewlogic ViewSim 7.4

Additional Items

#### Support

Demo board available extra

Support provided by Rapid Prototypes Inc. 90 days email and telephone support (not including user modifications) included in core price.

# **Applications**

- Real-time image processing applications

- High performance reconfigurable computing

- · High performance digital signal processing

- · Realtime video processing

- Digital neural networks

- · Algorithmic research

- · PC peripherals

- Digital video

January 10, 2000 3-1

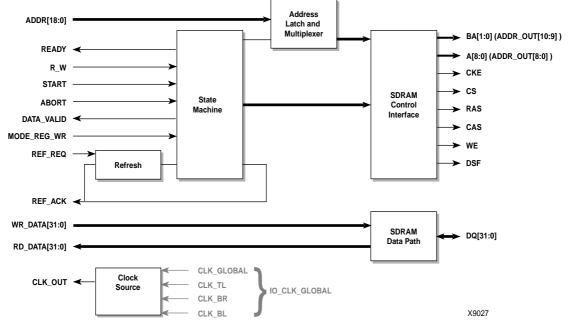

Figure 1: SDRAM Controller Block Diagram

# **General Description**

The SDRAM controller provides a static-RAM-like interface to synchronous dynamic RAMs, for use by application circuits within the remainder of the FPGA or external to it.

200MHz operation was achieved by floor-planning and using multiple fast BUFGE and BUFGLS clocks. So the design is pin-locked to 0FP 240 package relative to the SDRAM and clocks but modifications are possible.

The SDRAM controller is supplied as an EDIF netlist and constraint files, with VHDL and Verilog templates and a Viewlogic symbol file.

The core is currently available for 4000XL/XLA, and Virtex FPGAs.

# **Functional Description**

The SDRAM Controller is partitioned into modules as shown in Figure 1 and described below.

#### State Machine

In response to requests on its START, ABORT, MODE\_REG\_WR and internal ref\_req inputs, the State Machine sends the required sequence of commands and addresses to the SDRAM Control Interface. The direction of data transfer is determined by the state of R\_W when START is asserted. Commands are only accepted when the READY output is asserted. When reading from the

SDRAM, the DATA\_VALID output is asserted when valid data is on the RD\_DATA bus.

## **Address Latch and Multiplexer**

The Address Latch and Multiplexer takes the full 19 bit address and under the control of the State Machine passes the bank address and either the row address or the column address and auto-precharge bit to the SDRAM Control Interface at the appropriate time.

#### SDRAM Control Interface

The SDRAM Control Interface provides the appropriate timing and drive to the address and control pins of the SDRAM.

#### Refresh

The Refresh unit issues a refresh request to the State Machine 15.6 us after the last refresh, whether it was manual or automatic. It accepts manual refresh requests on the REF\_REQ input. The State Machine acknowledges receipt of a refresh request by pulsing the REF\_ACK output.

#### **SDRAM Data Path**

The Data Path unit handles the direction of data flow and provides the appropriate drive and timing to and from the SDRAM data (DQ) pins. It also maintains zeros on the SDRAM data mask (DQM) pins.

3-2 January 10, 2000

#### **Clock Source**

The Clock Source takes four copies of the (200MHz) clock from four FPGA pins, buffers them and supplies them (not shown) to various parts of the SDRAM controller. It is the physical layout of these clocks and the circuits they drive, that allows the controller to operate at 200MHz. The Clock Source also provides a clock to other circuitry within the FPGA, via CLK\_OUT.

External to the FPGA, a fifth copy of the clock must be fed to the CLK input of the SDRAM.

## **Core Modifications**

The SDRAM core can be modified to unlock the pin locations, but will result in slower performance than the basic core. The design is matched to the QFP 240 packages. Cores for other packages can be provided for an additional fee.

Rapid Prototypes will contract to modify the core to your specifications. We regret that Rapid Prototypes cannot provide support for user modifications.

## **Pinout**

The pinout of the SDRAM Controller is described in Table 1. The SDRAM signals are padded and part of the core.

The SDRAM signals connect to the FPGA via suitable terminations. You will find more detail on these in the datasheet for any SDRAM or SGRAM. e.g. MoSys® MG802C512.

## **Verification Methods**

Functional simulation has been carried out using ViewSim from Viewlogic's Workview Office™ version 7.4. Static timing analysis has been carried out for all paths using the Xilinx 1.5i tools. Hardware testing has been carried out at 200 MHz using the FastRAM board which Rapid Prototypes developed for Xilinx.

# Recommended Design Experience

Users should be familiar with Xilinx design flows and their chosen design entry format (schematic or HDL). They should also be familiar with PCB layout considerations for operation at 200MHz, including microstrip transmission lines, termination techniques, high-frequency power supply decoupling and parasitic capacitance minimization.

# **Available Support Products**

The FastRAM demo board is available from Rapid Prototypes, Inc. This board demonstrates the SDRAM core operating at 200 MHz and 800 MBytes/sec peak.

**Table 1: Core Signal Pinout**

| Signal                     | Signal<br>Direction | Description                                                                            |

|----------------------------|---------------------|----------------------------------------------------------------------------------------|

| <b>Application Signals</b> |                     | •                                                                                      |

| ADDR[18:0]                 | Input               | SDRAM address (de-<br>multiplexed)                                                     |

| READY                      | Output              | Controller is ready for data transfer (reading or writing data)                        |

| R_W                        | Input               | Direction of data<br>transfer to be initiated<br>by START                              |

| START                      | Input               | Initiate data transfer if READY                                                        |

| ABORT                      | Input               | Aborts a write com-<br>mand to allow writing<br>of less than 4 words                   |

| DATA_VALID                 | Output              | Read data is on the bus                                                                |

| MODE_REG_WR                | Input               | Write ADDR[17:9] to<br>the SDRAM mode<br>register                                      |

| REF_REQ                    | Input               | Perform an early re-<br>fresh now so as to<br>leave 15.6µs clear for<br>data transfers |

| REF_ACK                    | Output              | Acknowledge for REF_REQ                                                                |

| WR_DATA[31:0]              | Input               | Data bus from appli-<br>cation to SDRAM                                                |

| RD_DATA[31:0]              | Output              | Data bus from SDRAM to application                                                     |

| CLK_OUT                    | Output              | The system clock out.<br>The clock source is<br>internal to the control-<br>ler        |

| SDRAM Signals              |                     |                                                                                        |

| BA[1:0]                    | Output              | SDRAM bank address (ADDR_OUT[10:9]). LOC'ed to specific pad                            |

| A[8:0]                     | Output              | SDRAM address<br>(multiplexed,<br>ADDR_OUT[8:0]).<br>LOC'ed to specific<br>pad         |

| CKE                        | Output              | SDRAM clock enable (always high).<br>LOC'ed to specific pad                            |

January 10, 2000 3-3

Table 1: Core Signal Pinout (Cont.)

| Signal        | Signal<br>Direction | Description                                                                                                        |  |

|---------------|---------------------|--------------------------------------------------------------------------------------------------------------------|--|

| CS            | Output              | SDRAM chip select.                                                                                                 |  |

|               |                     | Loc'ed to specific pad                                                                                             |  |

| RAS           | Output              | SDRAM row address                                                                                                  |  |

|               |                     | strobe                                                                                                             |  |

| CAS           | Output              | SDRAM column address strobe. LOC'ed to specific pad                                                                |  |

| WE            | Output              | SDRAM write enable.<br>LOC'ed to specific<br>pad                                                                   |  |

| DSF           | Output              | Special function se-<br>lector for SGRAM (al-<br>ways low). LOC'ed to<br>specific pad                              |  |

| DQM[3:0]      | Output              | SDRAM data mask<br>bits (always low).<br>LOC'ed to specific<br>pad                                                 |  |

| DQ[31:0]      | In/Out              | Perform an early re-<br>fresh now so as to<br>leave 15µs clear for<br>data transfers.<br>LOC'ed to specific<br>pad |  |

| Clock Signals |                     |                                                                                                                    |  |

| CLK_GLOBAL    | Input               | Clock for reading<br>SDRAM and general<br>use. Only in 4000XL/<br>XLA                                              |  |

| CLK_TL        | Input               | Clock to top left of<br>FPGA. Only in<br>4000XL/XLA                                                                |  |

| CLK_BR        | Input               | Clock to bottom right<br>of FPGA. Only in<br>4000XL/XLA                                                            |  |

| CLK_BL        | Input               | Clock to bottom left of<br>FPGA. Only in<br>4000XL/XLA                                                             |  |

| IO_CLK_GLOBAL | Input               | Clock signal in Virtex core                                                                                        |  |

# **Ordering Information**

To make further inquiries or purchase the SDRAM Controller Core contact Rapid Prototypes Inc. directly. Rapid Prototypes Inc. retains the right to make changes to these specifications at any time, without notice. All trademarks, registered trademarks, or servicemarks are the property of their respective owners. Contact Rapid Prototypes for more information on this or other company products.

## **Related Information**

## Xilinx Programmable Logic

For information on Xilinx programmable logic or development system software, contact your local Xilinx sales office, or:

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 Phone: +1 408-559-7778

Phone: +1 408-559-7778 Fax: +1 408-559-7114 URL: www.xilinx.com

For general Xilinx literature, contact:

Phone: +1 800-231-3386 (inside the US)

+1 408-879-5017 (outside the US)

E-mail: literature@xilinx.com

For AllianceCORE™ specific information, contact:

Phone: +1 408-879-5381 E-mail: alliancecore@xilinx.com

URL: www.xilinx.com/products/logicore/alliance/

tblpart.htm

3-4 January 10, 2000