One Dimensional ROM-Based Correlator

July 31, 1997

XILINX®

DSP CORE Generator

Xilinx Inc.

2100 Logic Drive San Jose, CA 95124

Phone: +1 408-559-7778

Fax: +1 408-559-7114

E-mail: dsp@xilinx.com

URL: www.xilinx.com

#### **Features**

- Data can be loaded in either serial or parallel (broadside) fashion

- Supports data words from 4 to 128 bits in steps of 4

- Mask register that selects which bits within the data pattern to compare

- · Cascadable to any length

- Easily extendible to 2 dimensions

- High performance implementation utilizing efficient look-up table (LUT) design

**Product Specification**

- · Requires relatively few CLBs

- Single level of logic (1 LUT) per pipeline stage

- Density and performance guaranteed through Relationally Placed Macro (RPM) mapping and placement technology

## **Functional Description**

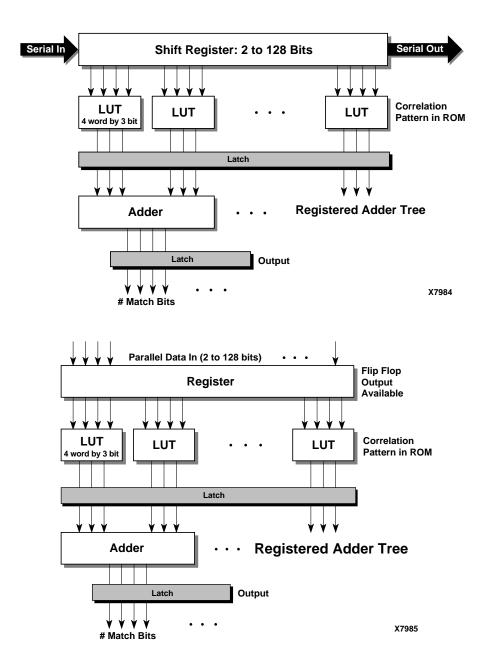

This parameterized core accepts data in a serial or parallel fashion and looks for a predetermined bit pattern that is stored in ROM look-up tables. The output is a binary representation of the number of bits that match the desired bit pattern after a bit mask has been applied to remove all of the "don't care" bits.

The match register, the mask register, and all of the logic to implement the compare is implemented in look-up table logic so the function can be realized as a series of small LUTs (one for each 4 bits of data) followed by a small adder tree

Latency is equal to one input buffer plus one pipeline register for each level of the 4-bit adder tree. For example, if the match register is 24 bits, the adder tree is 3 levels deep with a 5-bit wide output. The total latency is two (registers) + three (adder trees) = five.

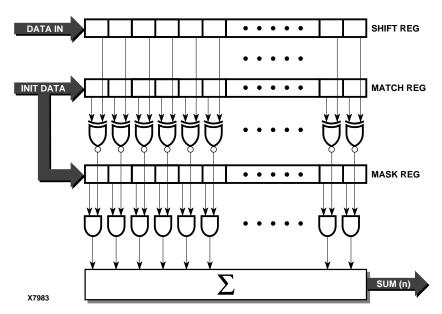

Figure 1. Serial In Correlator Block Diagram

Figure 2. CORE Generator Implementation for Serial Data (top) and Parallel Data (bottom)

This function is used in data communications to establish synchronization in a serial bit stream, and in any application that requires pattern recognition.

# Using Look-Up Tables for Implementing Correlators

The following example illustrates what the CORE Generator calculates to produce the contents of the distributed look-up tables. For a 4-bit correlator with an input search pattern of 1101 and a mask pattern of 1111 (include all bits), the LUT contains the following data.

Any n-stage correlator can be decomposed into (n/4) 4-stage correlators. The LUTs contain all potential outputs for each 4-stage correlation. For example, the correlation pattern 1101 stores 4 at address D in the LUT (all four bits match) and 3 at addresses 5, 9, C, and F in the LUT (three bits match).

**Table 1. LUT Contents**

| Address | Data                |

|---------|---------------------|

| 0000    | 001 (1 bit matches) |

| 0001    | 010 (2 bits match)  |

| 0010    | 000 (0 bits match)  |

| 0011    | 001 (1 bit matches) |

| 0100    | 010 (2 bits match)  |

| 0101    | 011 (3 bits match)  |

| 0110    | 001 (1 bit matches) |

| 0111    | 010 (2 bits match)  |

| 1000    | 010 (2 bits match)  |

| 1001    | 011 (3 bits match)  |

| 1010    | 001 (1 bit matches) |

| 1011    | 010 (2 bits match)  |

| 1100    | 011 (3 bits match)  |

| 1101    | 100 (4 bits match)  |

| 1110    | 010 (2 bits match)  |

| 1111    | 011 (3 bits match)  |

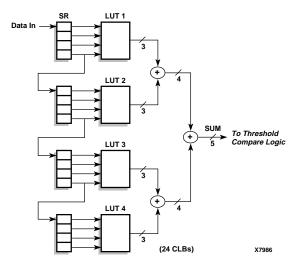

### **Combining 4-Input Sections**

Each four-input correlator section can be combined by summing the outputs with an adder tree. The look-up tables are 16 words (4 address lines) by 3 bits wide each. The adder tree grows by one bit for each level and the resulting output is a binary number representing the number of matches in the input data word after the mask register has been applied.

Figure 3. Combining 4-Input Sections

#### **Pinout**

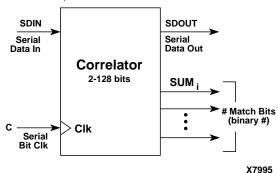

Signal names for the schematic symbols are shown in Figures 4 and 5, and described in Tables 2 and 3.

Figure 4. Core Schematic Symbol – Serial Data In Table 2. Core Signal Pinout – Serial Data In

| Signal | Signal Direction | Description                                                                                                                                 |

|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| SDIN   | Input            | Serial Data In – Serial data stream for correlation.                                                                                        |

| С      | Input            | Serial Data Clock                                                                                                                           |

| SDOUT  | Output           | Serial Data Out – SDIN de-<br>layed N clocks.                                                                                               |

| SUMi   | Output           | Binary representation of the<br>number of bits that match the<br>correlation pattern excluding<br>any bits defined in the mask<br>register. |

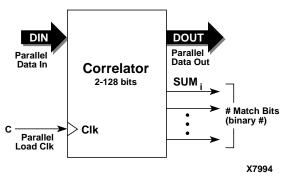

Figure 5. Core Schematic Symbol - Parallel Data In

Table 3. Core Signal Pinout - Parallel Data In

| Signal | Signal Direction | Description                                                                                                                                 |

|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| DIN    | Input            | Parallel Data In – 2 to 128 bits                                                                                                            |

| С      | Input            | Clock – Parallel load clock                                                                                                                 |

| DOUT   | Output           | Parallel Data Out – DIN de-<br>layed 1 clock.                                                                                               |

| SUMi   | Output           | Binary representation of the<br>number of bits that match the<br>correlation pattern excluding<br>any bits defined in the mask<br>register. |

The CORE Generator accepts the parameters entered through the dialog box and creates the specific design from the values entered using a parameterized VHDL recipe. VHDL instantiation code and a schematic symbol are created along with the netlist for the design.

#### **CORE Generator Parameters**

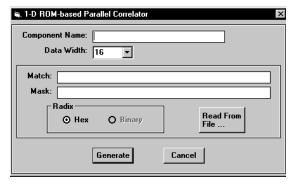

This macro has two CORE Generator dialog boxes. The one for the parallel correlator is shown in Figure 6. The serial correlator dialog box has a different title, but the parameters are the same. The parameters are as follows:

- Component Name: Enter a name for the component.

- Data Width: Select an input width from the pull-down menu for the data string to be compared. The valid range is 4-128 in multiples of 4.

- Match: Hexadecimal string specifying the pattern to look for.

- Mask: A zero in this hexadecimal string specifies that the data bit in the same position should be ignored when calculating the number of match bits.

- Radix: Hexadecimal or Binary representation of the Match and Mask values.

Read From File: Read the Match and Mask values from a text file.

Figure 6. CORE Generator Dialog Box

#### Bit Width and CLB Count

Table 4 lists the number of CLBs required for example bit widths. The maximum speed is for XC4000E-1 devices.

Table 4. Bit Width versus CLB Count

| Bit Width | CLB Count |

|-----------|-----------|

| 4         | 4         |

| 7         | 11        |

| 8         | 14        |

| 9         | 16        |

| 10        | 17        |

| 11        | 19        |

| 12        | 20        |

| 13        | 22        |

| 14        | 24        |

| 15        | 26        |

| 16        | 25        |

| 17        | 29        |

| 20        | 36        |

| 32        | 54        |

# **Ordering Information**

This macro comes standard with the Xilinx CORE Generator. For additional information contact your local Xilinx sales representative, or e-mail requests to dsp@xilinx.com.