# ChipScope Software and ILA Cores User Manual

0401884 (v2.0) December 15, 2000

Software v2001.1

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, Fast-Map, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, Selectl/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACT step, XACT step Advanced, XACT step Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5.838.954; 5.841.296; 5.841.867; 5.844.422; 5.844.424; 5.844.829; 5.844.844; 5.847.577; 5.847.579; 5.847.580; 5.847.993: 5.852.323: 5.861.761: 5.862.082: 5.867.396: 5.870.309: 5.870.327: 5.870.586: 5.874.834: 5.875.111: 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

Xilinx Development System

# **Chapter 1**

# Introduction

# **ChipScope Tools Overview**

As the density of FPGA devices increases, so does the impracticality of attaching test equipment probes to these devices under test. The ChipScope Analyzer integrates key logic analyzer hardware components with the target design inside the Virtex® device. The ChipScope Tools communicate with these components and provide the designer with a complete logic analyzer, without the need for cumbersome probes or expensive test equipment.

# **ChipScope Tools Description**

The ChipScope Tools include:

- the ChipScope Core Generator

- the ChipScope Core Inserter, and

- the ChipScope Analyzer

The Core Generator provides netlists and instantiation templates for the Integrated CONtroller (ICON) core and the Integrated Logic Analyzer (ILA) core.

The Core Inserter automatically inserts these two cores into the user's synthesized design.

The Analyzer allows setup and trace display for the ILA core. The ILA core provides the trigger and trace capture capability. The ICON core communicates to the dedicated Boundary Scan pins.

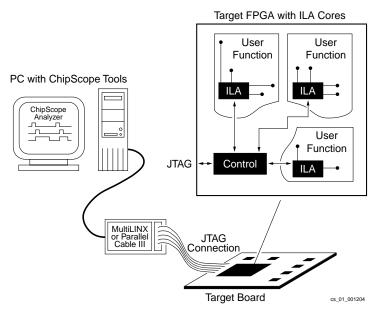

The Analyzer supports both the Xilinx MultiLINX<sup>™</sup> and Parallel Cable III download cables for communication between the PC and FPGA(s). The MultiLINX cable supports both USB (Windows 98 and Windows 2000) and RS-232 serial communication from the PC (Figure 1). The Parallel Cable III

supports only parallel port communication from the PC to the Boundary Scan chain.

Figure 1: ChipScope Block Diagram

Users can place the ILA and ICON cores into their design by:

- generating the cores with the Core Generator and instantiating them into the source HDL code, or

- inserting the cores into the post-synthesis EDIF netlist using the Core Inserter

The design is then placed and routed using the Xilinx Alliance Series<sup>TM</sup> or Foundation Series<sup>TM</sup> tools. Next, the user downloads the bitstream and analyzes the design with the ChipScope software Analyzer.

The ChipScope Analyzer contains many features that Xilinx FPGA designers need for thoroughly verifying their logic (Table 1-1). User-selectable data channels range from 1 to 256, and the number of sample sizes ranges from 256 to 4096, effectively doubling any FPGA logic analysis capability on the market today. Users can change the triggers in real time without affecting

their logic. The easy-to-use ChipScope Analyzer leads designers through the process of modifying triggers and analyzing the data.

| Feature                                                                           | Benefit                                                                                                           |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 1 to 256 user-selectable data channels                                            | Accurately captures wide data bus functionality                                                                   |

| User-selectable sample buffers<br>ranging in size from 256 to 4096<br>samples     | Large sample size increases<br>accuracy and probability of<br>capturing infrequent events                         |

| Separate bus trigger with user-selectable width of 1-64 bits                      | Separate trigger bus reduces need for sample storage                                                              |

| All data and trigger operations are<br>synchronous to user clock up to<br>155 MHz | Capable of high-speed data capture                                                                                |

| Trigger conditions are in-system<br>changeable without affecting user<br>logic    | No need to single step or stop a design for logic analysis                                                        |

| Can write waveforms to VCD,<br>FBDF, and ASCII formats                            | Compatible with Agilent<br>Technologies and other waveform<br>viewers                                             |

| Easy-to-use graphical interface                                                   | Guides users through selecting the correct options                                                                |

| Up to 15 independent ILA capture cores per device                                 | Can segment logic and test smaller<br>sections of a large design for greater<br>accuracy                          |

| Multiple trigger settings                                                         | Records duration and number of<br>events along with matches and<br>ranges for greater accuracy and<br>flexibility |

| Downloadable from the Xilinx website                                              | Tools are easily accessible from the ChipScope Suite                                                              |

Table 1-1 ChipScope Features and Benefits

#### **Design Flow**

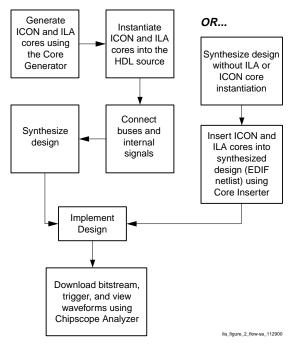

The ChipScope Tools design flow (Figure 2) merges easily with any standard FPGA design flow that uses a standard HDL synthesis tool and the Alliance Series or Foundation Series implementation tools.

Figure 2: ChipScope Tools Design Flow

# **Trigger Settings**

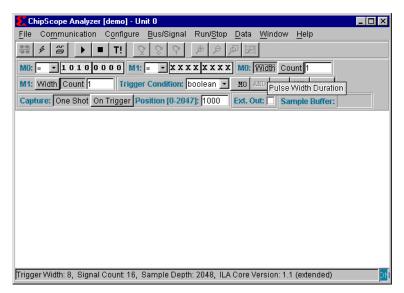

The ILA core has two trigger modes: *basic* and *extended*. The basic trigger mode provides up to two trigger match units capable of detecting a single exact match for every trigger condition. The extended trigger mode adds the ability to do range matching, trigger pulse width duration measurement, trigger event counting, and *if-then* trigger macros. Table 1-2 compares the basic and extended trigger modes.

| Trigger Mode Feature                                  | Basic<br>Mode | Extended<br>Mode |

|-------------------------------------------------------|---------------|------------------|

| Up to two match units                                 | Yes           | Yes              |

| Trigger function combining all match units            | Yes           | Yes              |

| Match value and edge comparison                       | Yes           | Yes              |

| Match range comparison (such as >, $\geq$ <, $\leq$ ) | No            | Yes              |

| Trigger pulse duration measurement                    | No            | Yes              |

| Trigger event count measurement                       | No            | Yes              |

| If-then trigger macros                                | No            | Yes              |

#### Table 1-2 Basic and Extended ILA Trigger Modes

# **External Trigger Description**

The ChipScope software Analyzer can accept a trigger input signal and generate a trigger output signal for use with external test equipment.

An external trigger input signal must enter the device on a normal input pin connected to the ICON core unit where it is distributed to each of 15 possible ILA components in the design.

Similarly, each ILA core unit can generate an output signal that is connected to the ICON unit. The ICON unit then logically OR's all of the external trigger output signals and drives them to a single output pin on the device. Users can enable each ILA core component to drive each respective external trigger output signal to the ICON core component without having to resynthesize the design.

#### **Capture Modes**

Each ILA core can capture data independently from all other ILA cores in the design. Furthermore, the ILA core can capture data using one of two capture modes: *one shot* and *on trigger*.

The one shot capture mode uses a single trigger event (such as a boolean or macro combination of the individual trigger match unit events) to collect enough data to fill the sample buffer (up to 4096 samples). The trigger position can be set to the beginning of the sample buffer (trigger first, then collect), the end of the sample buffer (collect until the trigger event), or anywhere in between.

The on trigger capture mode uses multiple trigger events to perform repetitive measurements on the design under test. Each trigger event can cause a capture of 1 to 16 data samples. These repetitive measurements can continue until the captured data fills the sample buffer.

### ILA and ICON Core Resource Usage

Tables 1-3, 1-4, and 1-5 show the ILA and ICON core resource usage.

| Number of<br>Control<br>Ports | LUTs | Flops | Slices | Percentage<br>of XCV300 |

|-------------------------------|------|-------|--------|-------------------------|

| 1                             | 68   | 40    | 34     | 1.1                     |

| 2                             | 103  | 40    | 52     | 1.7                     |

| 3                             | 138  | 40    | 69     | 2.2                     |

| 4                             | 171  | 40    | 86     | 2.8                     |

#### Table 1-3 ICON Core CLB Resource Usage

| Trigger/<br>Data Width | LUTs | Flops | Slices | Percentage<br>of XCV300 |

|------------------------|------|-------|--------|-------------------------|

| 2                      | 57   | 103   | 52     | 1.7                     |

| 4                      | 60   | 111   | 56     | 1.8                     |

| 8                      | 66   | 127   | 64     | 2.1                     |

| 16                     | 78   | 159   | 80     | 2.6                     |

| 32                     | 105  | 225   | 113    | 3.7                     |

| 64                     | 154  | 355   | 178    | 5.8                     |

Table 1-4 ILA Core CLB Usage<sup>a</sup>

a. This table describes the ILA core with one match unit and the basic trigger function.

| Trigger/   | Data Samples |     |      |      |      |

|------------|--------------|-----|------|------|------|

| Data Width | 256          | 512 | 1024 | 2048 | 4096 |

| 2          | 1            | 1   | 1    | 1    | 2    |

| 4          | 1            | 1   | 1    | 2    | 4    |

| 8          | 1            | 1   | 2    | 4    | 8    |

| 16         | 1            | 2   | 4    | 8    | 16   |

| 32         | 2            | 4   | 8    | 16   | 32   |

| 64         | 4            | 8   | 16   | 32   | 64   |

Table 1-5 ILA Core Block RAM Usage<sup>a</sup>

a. This table describes the ILA core with one match unit and the basic trigger function.

#### Synthesis/Insertion Requirements

Users can modify many options in the ILA and ICON cores without resynthesizing (in the case of the core generator) or re-inserting (in the case of the core inserter). However, after changing selectable parameters (such as width of the data port or the depth of the sample buffer), the design must be resynthesized either with new cores, or with the cores re-inserted. Table 1-6 describes which design changes require this.

| Design Parameter Change            | Resynthesis<br>or<br>Re-Insertion<br>Required |

|------------------------------------|-----------------------------------------------|

| Change trigger pattern             | No                                            |

| Running and stopping the trigger   | No                                            |

| Enabling the external triggers     | No                                            |

| Changing the trigger signal source | Yes <sup>a</sup>                              |

| Changing the data signal source    | Yes <sup>a</sup>                              |

| Changing the ILA clock signal      | Yes                                           |

| Changing the sample buffer depth   | Yes                                           |

#### Table 1-6 Design Parameter Changes Requiring Resynthesis

a. This feature is supported by the Alliance Series 3.1i FPGA Editor and Foundation Series 3.1i FPGA Editor.

# System Requirements

#### **Communications Requirements**

ChipScope software Analyzer uses either the MultiLINX or Parallel Cable III download cable to communicate with the target devices in Boundary Scan chain of the board-under-test.

The MultiLINX cable uses the USB port found on newer PCs and downloads at speeds up to 12 Mb/s throughput. The MultiLINX cable also supports communication through the PC's RS-232 serial port at speeds up to 57.6 kb/s. MultiLINX also features an adjustable voltage interface that enables it to communicate with systems and I/Os operating at 5V, 3.3V, or 2.5V. The MultiLINX cable is available from Silicon Xpresso<sup>TM</sup> Cafe (from www.xilinx.com choose Purchase>Programming Cables).

The Parallel Cable III uses the parallel port (i.e., printer port) to communicate with the Boundary Scan chain of the board-under-test. The Parallel Cable III supports only JTAG configuration of target FPGA devices and does not support slave serial configuration. The Parallel Cable III is also available from Silicon Xpresso Cafe (from <u>www.xilinx.com</u> choose Purchase>Programming Cables).

# **Board Requirements**

For the ChipScope Analyzer and download cable to work properly with the board-under-test, the following board-level requirements must be met:

- One or more Virtex, Virtex-E, or Spartan-II target devices must be connected to a JTAG header that contains the TDI, TMS, TCK, and TDO pins

- If another device would normally drive the TDI, TMS, or TDI pins of the JTAG chain containing the target device(s), then jumpers on these signals are required to disable these sources, preventing contention with the download cable

- If using the MultiLINX download cable,  $V_{CC}$  (2.5-5.0V) and GND headers must be available for powering the MultiLINX cable

- If using the Parallel Cable III download cable,  $V_{CC}$  (2.5-3.3V) and GND headers must be available for powering the Parallel Cable III cable

- If the slave-serial configuration mode is to be used by the MultiLINX cable, then a header containing the DIN, CCLK, INIT, PROGRAM, and DONE signals is required

- Note that the Parallel Cable III should only be used in JTAG configuration mode. The slave serial flying wires should not be attached to the Parallel Cable III device when used in conjunction with ChipScope Analyzer.

#### **Host System Requirements**

The ChipScope Analyzer runs on any of the following PC systems having these minimum requirements:

- Windows 98, Windows 98 SE, or Windows 2000 OS, 32 MB of memory, RS-232 port (MultiLINX), USB port (MultiLINX), or parallel port (Parallel Cable III)

- Windows NT 4.0, 64 MB of memory, RS-232 port (MultiLINX) or parallel port (Parallel Cable III)

- Java Run-time Environment version 1.1.8 (available for downloading from the ChipScope Suite)

#### Note:

In order to use the MultiLINX USB interface under Windows 98 Second Edition or Windows 2000, the correct driver must be used. The updated driver is included in all versions of Xilinx software beginning with 3.1i Service Pack 1.

# Installing ChipScope Tools

The ChipScope Tools include three separate programs: the ChipScope Core Inserter, the ChipScope Core Generator, and the ChipScope Analyzer.

After downloading the tools in the form of a self-extracting archive file (**ChipScope***m***-***n***.exe**, where *m***-***n* denotes the current version):

- 1. Select Start>Run.

- 2. Browse for ChipScopem-n.exe.

- 3. Click Run.

- 4. Follow the install wizard instructions. The Analyzer can be installed separately from the Core Inserter and Core Generator.

### Installing the Java Run-time Environment

If you have not already installed the Java Run-time Environment 1.1.8, then download it from the ChipScope Suite the same way you downloaded the ChipScope Tools. Next:

- 1. Select **Start>Run** to run the self-extracting installation file.

- 2. Browse for the jre1\_1\_8-win.exe file you just downloaded.

- 3. Click Run.

- 4. Follow the install wizard instructions.

### Installing MultiLINX USB Driver for Windows 98

If you need to install the MultiLINX<sup>TM</sup> cable under Windows 98 or Windows 2000 for USB:

- 1. Make sure that the PWR and GND wires of the MultiLINX cable are connected to power and ground sources, respectively.

- 2. Plug the cable into the USB port of the host computer. (An installation dialog box opens.)

- 3. Click Have Disk.

- 4. Browse the ChipScope Tools installation for the mltlnx.inf file. This is typically installed in folder C:\Program Files\Xilinx\ChipScope\data.

- 5. Click **OK** and follow the installation wizard instructions.

#### Installing the Parallel Cable III Driver

ChipScope requires a device driver for the Parallel Cable III to function properly. If you have the Alliance Series or Foundation Series software on the system, the driver is most likely installed. If you need to install the driver, follow these steps:

- 1. Use Windows Explorer to locate the ChipScope installation (usually C:\Program Files\Xilinx\ChipScope).

- 2. Open the cablell folder in the ChipScope installation directory.

- 3. Run the **cablelli** installation by double clicking the **Setup.exe** file in the **cablelli** folder. Setup will guide you through the installation process.

# **Chapter 2**

# Using the ChipScope Core Generator

# **Core Generator Overview**

The ChipScope Core Generator tool offers users an intuitive graphical user interface to generate the ILA controller core (ICON) and the analyzer (ILA) cores. Once the cores are generated, users can use the instantiation templates (that are provided) to quickly and easily insert the cores into their VHDL or Verilog design. After completing the instantiation and running synthesis, then users implement the design, using the Xilinx implementation tools.

# **Generating an ICON Core**

The Core Generator gives users the ability to define and generate a customized Integrated CONtroller (ICON) unit to use with one or more Integrated Logic Analyzer (ILA) units in VHDL and Verilog designs. The easy-to-use interface allows users to customize control ports (the number of ILA cores to be connected to the ICON core) and control whether or not to use USER2 Boundary Scan port signals.

After the Core Generator validates the user-defined parameters, it generates an EDIF netlist (\*.edn) and example code in VHDL and Verilog specific to the synthesis tool used. Users can easily generate the netlist and code examples for use in normal Virtex<sup>TM</sup>, Virtex<sup>TM</sup>-E, and Spartan®-II design flows.

The first screen in the Core Generator offers users the choice to generate either an ICON core or an ILA core. Choose ICON (Integrated Controller) core, and click **Next**.

### **Choosing the File Destination**

The destination for the ICON EDIF file (icon.edn) is displayed in the Output Netlist field. The default directory is the Core Generator install path. To

change it, the user can either type a new path in the field, or select **Browse** to navigate to a new destination.

#### **Entering the Number of Control Ports**

The ICON core can communicate with up to 15 ILA core units at any given time. However, no ILA core unit may share its control port with any other ILA unit. Therefore, the ICON core needs up to 15 distinct control ports to handle this requirement. Users can select the number of control ports from the **Number of Control Ports** pull-down list.

### **Enabling the External Triggers**

Users can configure the ICON core to implement an external trigger input and an external trigger output (i.e. two separate pins) to trigger external test equipment. To enable instantiation of the external input and output trigger pins, select the appropriate **Enable External Trigger Input** and **Enable External Trigger Output** check box. If the design does not require external triggers, or if there are no usable pins for triggers, be sure to not check these boxes.

If the pins are enabled, then set their IOB location using the following steps:

- 1. Find the external input and output trigger pad signals in the \*.pad file produced by the place and route (par) tool. The signals have the following suffixes:

- \*/U\_icon\_core/ext\_in\_pad (input)

- \*/U\_icon\_core/ext\_out\_pad (output)

- 2. Add pin LOC constraints to the **\*.ucf** file so that **par** correctly places the external trigger pins.

#### **Disabling JTAG Clock BUFG Insertion**

The ICON core communicates to the outside world via the USER1 JTAG scan chain that is clocked by the JTAG clock (TCK). By default, this clock is placed on a global clock resource (BUFG). Checking this box disables that insertion. This should be done only if global resources are very scarce; placing the JTAG clock on regular routing, even high-speed backbone routing, introduces skew. To minimize this skew, make sure the design is adequately constrained.

## **Including Boundary Scan Ports**

The BSCAN\_VIRTEX primitive has two sets of ports: USER1 and USER2. These provide an interface to the Boundary Scan TAP controller of the Virtex or Virtex-E device. Since the ICON core uses only the USER1 port for communication purposes, the USER2 port signals are available. To use the USER2 interface to the BSCAN\_VIRTEX primitive, click the Include Boundary Scan Ports check box.

#### Note:

The Boundary Scan ports should be included *only* if the design needs them. If they are included and not used, some synthesis tools do not connect the ICON core properly which causes errors during the synthesis and implementation stages of development.

# **Choosing the Instantiation Template**

After choosing the parameters for the ICON core, you can construct an instantiation template. Click **Next** to view the Sample Code Generation Options, then choose which synthesis tool and language to use. The synthesis tools supported are:

- Exemplar LeonardoSpectrum<sup>™</sup>

- Synopsys FPGA Compiler<sup>™</sup>

- Synopsys FPGA Compiler II<sup>™</sup>

- Synopsys FPGA *Express*<sup>™</sup>

- Synplicity Synplify®

- XST (Xilinx Synthesis Technology)

Specifically tailored attributes and options are embedded in the instantiation template for the various synthesis tools. To generate the ICON core without any example files, deselect the **Generate Example Files** checkbox.

# **Generating the Core**

After entering the ICON core parameters, click **Generate Core** to create the netlist and applicable code examples. A message window opens, the progress information appears, and the CORE GENERATION COMPLETE message signals the end of the process. The user can choose to either go back to respecify options or **Start Over**.

### Using the ICON Core

To instantiate the example ICON core HDL files into your design, use the following guidelines to connect the ICON core port signals to various signals in your design:

- Connect one of the ICON core's unused CONTROL\* port signals to a control port of only one ILA core instance in the design.

- Leave any unused CONTROL\* ports of the ICON core unconnected. (They are removed automatically during the implementation process.)

# **Generating an ILA Core**

The ChipScope Core Generator gives users the ability to define and generate a customized ILA capture core to use with VHDL and Verilog designs. The easy-to-use interface allows users to customize the maximum number of data sample words stored by the ILA core, the width of the data sample words, and the width of the trigger word (if different from the data word).

After the Core Generator validates the user-defined parameters, it generates an EDIF netlist (\*.edn) and VHDL and Verilog example code specific to the synthesis tool used. Users can easily generate the netlist and code examples for use in normal Virtex<sup>TM</sup>, Virtex<sup>TM</sup>-E, and Spartan<sup>®</sup>-II design flows.

The first screen in the Core Generator offers users the choice to generate either an ICON or ILA core. Choose ILA (Integrated Logic Analyzer), and click **Next**.

#### **Choosing the File Destination**

The destination for the ILA EDIF (ila.edn) is displayed in the **Output Netlist** field. The default directory is the Core Generator install path. To change it, the user can either type a new path in the field, or select **Browse** to navigate to a new destination.

The user can choose from three types of names: a long name in which the options are specified in the component name; a short name (ila.edn); or a custom name for the netlist (the component name will be changed accordingly). Either a long name or a custom name should be chosen if multiple ILA cores with different parameters are used in the design.

The long file name indicates the various parameters specified for the ILA core. Table 2-1 shows the meaning of the abbreviations.

| Abbreviation | Meaning                                 |  |

|--------------|-----------------------------------------|--|

| ddx          | Data Depth of size x                    |  |

| dwx          | Data Width of size <i>x</i>             |  |

| twx          | Trigger Width of size <i>x</i>          |  |

| t_eq_d       | Trigger Equals Data                     |  |

| ex or bx     | Extended or Basic Matching with x Units |  |

Table 2-1

ILA Long Filename Abbreviations

# Selecting the Trigger Type

To generate the first part of the ILA core, select one of the following trigger types:

- **Trigger separate from data**: The trigger word is completely independent of the data word

- **Trigger same as data**: The trigger and data words are identical. This mode is very common in most logic analyzers, since users can trigger on any bit in the data word being collected. This mode also conserves CLB and routing resources in the ILA core, but limits the data sample word width to the maximum trigger width of 64 bits

# Selecting the Trigger Match Unit Type

An ILA core trigger unit comprises one or more match units that contribute to the overall trigger condition by looking for a specific pattern on the trigger input. The types of patterns and their occurrence over time that are looked for depend on the type of the match unit. The ChipScope core generator handles *basic* and *extended* trigger match units.

The basic trigger match unit:

- Finds only one occurrence of an exact match of a trigger value or edge

- Can be used in conjunction with other trigger match units to build the trigger condition boolean equation (using AND/OR)

The extended trigger match unit:

- Finds **one or more** occurrences of an exact match of a trigger value or edge

- Finds one or more occurrences of a range of trigger values

- Detects contiguous (pulse width) or non-contiguous (event count) trigger match conditions over a number of clock cycles

- Can be used in conjunction with other trigger match units to build the trigger condition boolean equation (using AND/OR)

- Can be used in conjunction with other trigger match units to build the trigger condition macro equation (using IF/THEN)

For the ILA core that is being generated, the Trigger Match Unit Type is selected for all match units at the same time.

# Selecting the Number of Trigger Match Units

The number of Trigger Match Units can be set to either one or two. Selecting two trigger match units allows a more flexible trigger condition equation to be a combination of both match units. Selecting one match unit conserves resources while still allowing some flexibility in triggering.

## Selecting the Data Depth

The maximum number of data sample words that the ILA core can store is called the *data depth*. The data depth determines the number of data width bits contributed by each block RAM unit used by the ILA unit. You can set the data depth to one of five values:

- Data Depth = 256 samples, data width of one block RAM unit = 16 bits

- Data Depth = 512 samples, data width of one block RAM unit = 8 bits

- Data Depth = 1024 samples, data width of one block RAM unit = 4 bits

- Data Depth = 2048 samples, data width of one block RAM unit = 2 bits

- Data Depth = 4096 samples, data width of one block RAM unit = 1 bits

# **Entering the Data Width**

The width of each data sample word stored by the ILA core is called the *data width*. If the data and trigger words are independent from each other, then the maximum allowable data width depends on the target device type and data depth. However, if the data and trigger words are the same, then the data/trigger width must be any even number in the range of 2 to 64.

## **Selecting the Trigger Width**

The width of the trigger word used by the ILA core is called the *trigger width*. If the data and trigger words are independent from each other, then the trigger width can be any even integer in the range of 2 to 64. However, if the data and trigger words are the same, then both the data and trigger widths must be set to any even integer value in the range of 2 to 64.

## **Choosing the Instantiation Template**

After choosing the parameters for the ILA core, you can construct an instantiation template. Click **Next** to view the Sample Code Generation Options, then choose which synthesis tool and language to use. The synthesis tools supported are:

- Exemplar LeonardoSpectrum

- Synopsys FPGA Compiler

- Synopsys FPGA Compiler II

- Synopsys FPGA Express

- Synplicity Synplify

- XST (Xilinx Synthesis Technology)

Specifically tailored attributes and options are embedded in the instantiation template for the various synthesis tools. To generate the ILA core without any example files, deselect the **Generate Example Files** checkbox.

## **Generating the Core**

After entering the ILA core parameters, click **Generate Core** to create the netlist and applicable code examples. A message window opens, the progress information appears, and the CORE GENERATION COMPLETE message signals the end of the process. The user can choose to either go back to respecify options or **Start Over**.

## Using the ILA Core

To instantiate the example ILA core HDL files into your design, use the following guidelines to connect the ILA core port signals to various signals in your design:

- Connect the ILA core's CONTROL port signal to an **unused** control port of the ICON core instance in the design.

- Connect all unused bits of the ILA core's data and trigger port signals to "1". This prevents the mapper from removing the unused trigger and/or data signals and also avoids any DRC errors during the implementation process.

- If **Trigger Same As Data** is selected, connect the data/trigger signal(s) to the ILA core's DATA port signal. The ILA core's TRIG port signal is disconnected in this case. In the source code, this port can be connected to the same bus as the DATA port or to all "1"s.

- Make sure the data and trigger source signals are synchronous to the ILA clock signal.

# **Chapter 3**

# Using the ChipScope Core Inserter

# **Core Inserter Overview**

The ChipScope Core Inserter is a post-synthesis tool for users to generate a netlist that includes the user design as well as ICON and ILA cores, parameterized accordingly. The Core Inserter gives users the flexibility to quickly and easily use the ILA functionality without resynthesizing the entire design, and without any HDL instantiation.

# **ChipScope Core Inserter Menu Features**

# **Working with Projects**

Core Inserter projects hold all relevant information about source files, destination files, core parameters, and core settings. This allows the user to conveniently store and retrieve information about core insertion between sessions.

When the ChipScope Core Inserter is first opened, all the relevant fields are completely blank.

| 👹 ChipScope Core Inserter          |                                                                                                                                                     |                                                |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| <u>File Edit Insert Tools Help</u> |                                                                                                                                                     |                                                |

|                                    |                                                                                                                                                     | 8                                              |

| ⊡ • DEVICE                         | DEVICE                                                                                                                                              | Select Device Options                          |

| LCON                               | Design Files Input Design Netlist Input Constraints File: Output Design Netlist Output Constraints File: Output Constraints File: Output Directory: | Browse<br>Browse<br>Browse<br>Browse<br>Browse |

| Messages                           | < Eitaviona NeXt >                                                                                                                                  |                                                |

Figure 3: Blank Core Inserter Project

The condition in Figure 3 can also be achieved by selecting File>New.

#### **Opening an Existing Project**

To open an existing project, select it from the list of recently opened projects, or select **File>Open Project**, and browse to the project location. When the desired project is located, double-click on it, or select **Open**.

#### **Saving Projects**

If a project has changed during the course of a session, the user will be prompted to save the project upon exiting the Core Inserter. A project can also be saved by selecting **File>Save**. To rename the current project or save it to another filename, select **File>Save As**, type in the new name, and click **Save**.

#### **Exiting the Core Inserter**

To exit the ChipScope Core Inserter, select File>Exit. If the current project has not been saved, the user will be prompted to save or quit.

#### **Inserting and Removing ILA Units**

New ILA units can be inserted into the project by selecting Edit>New ILA Unit. An ILA unit can be removed by selecting Edit>Remove Unit after selecting which ILA unit to delete.

#### **Setting Preferences**

Three external programs (Design Manager, ChipScope Analyzer, and Edif2Ngd) can be called by the ChipScope Core Inserter. The manner in which these programs are called can be altered by selecting **Edit>Preferences**.

#### **Inserting the Cores**

ICON and ILA Cores are inserted when the flow is completed, or by selecting **Insert>Insert Core**. If all channels of all the ILA cores are not connected to valid signals, an error message results.

### Launching Related Tools

Both the Xilinx Design Manager and the ChipScope Analyzer can be launched from the ChipScope Core Inserter by selecting **Tools>Design Manager** or **Tools>ChipScope**. The locations of these programs can be specified in the Preferences.

# **Specifying Input and Output Files**

The ChipScope Core Inserter works in a step-by-step process. The first screen you see (Figure 3) shows what needs to be specified first: the input design netlist and constraints file. Click **Browse** to navigate to the directory where the netlist and constraint files are. The Core Inserter will not write over the netlist or UCF files specified. Instead, a new netlist and UCF will be

created with the \_ila extension appended by default. Figure 4 shows a project with input and output files specified. When this step is completed, click **Next**.

| 🛃 ChipScope Core Inse         | iter                     |                                         |                       |

|-------------------------------|--------------------------|-----------------------------------------|-----------------------|

| <u>File Edit Insert Tools</u> | s <u>H</u> elp           |                                         |                       |

|                               | <b>±</b>                 |                                         | ?                     |

| - DEVICE                      | DEVICE                   | 1                                       | Select Device Options |

| ICON                          | Design Files             |                                         |                       |

|                               | Input Design Netlist:    | E:\projects\ila\usage_test\base.edf     | Browse                |

|                               | Input Constraints File:  | E:\projects\ila\usage_test\base.ucf     | Browse                |

|                               | Output Design Netlist:   | E:\projects\ila\usage_test\base_ila.ngo | Browse                |

|                               | Output Constraints File: | E:\projects\ila\usage_test\base_ila.ucf | Browse                |

|                               | Output Directory:        | E:\projects\ila\usage_test\             | Browse                |

|                               | < Previous Next          | >                                       |                       |

| Messages                      |                          |                                         |                       |

|                               |                          |                                         | ×                     |

| 4                             |                          |                                         | ۲                     |

Figure 4: Core Inserter Project with Files Specified

### **Choosing ICON Options**

The first options that need to be specified are for the ICON core. The ICON core is the controller core that all ILA units connect to. The ICON core has the options shown in Figure 5.

#### **Enable External Trigger Input**

This option causes a PAD to be added to the design; the pin location specified in Figure 5 is added in the output UCF file specified in Figure 4. This signal is a logical OR'd condition of all the trigger states of all ILA cores in the design.

#### **Enable External Trigger Output**

This option causes a PAD to be added to the design; the pin location specified in Figure 5 is added in the output UCF file specified in Figure 4. This signal can be used in the ChipScope Analyzer to trigger the ILA cores.

#### **Disable JTAG Clock BUFG Insertion**

The ICON core communicates to the outside world via the USER1 JTAG scan chain that is clocked by the JTAG clock (TCK). By default, this clock is placed on a global clock resource (BUFG). To disable this insertion, check the Disable JTAG Clock BUFG Insertion box. This should only be done if global resources are very scarce; placing the JTAG clock on regular routing, even high-speed backbone routing, introduces skew. Make sure the design is adequately constrained to minimize this skew.

Figure 5 shows a sample of the ICON options. When all ICON options have been set, click **Next**.

| EhipScope Core Insert          | er                                 |                              | _ 🗆 ×    |

|--------------------------------|------------------------------------|------------------------------|----------|

| <u>File Edit Insert T</u> ools | <u>H</u> elp                       |                              |          |

|                                | 4                                  |                              | ?        |

|                                | ICON                               | Select Integrated Controller | Options  |

| CON                            | Parameters                         |                              |          |

|                                | 🔽 Enable External Trigger Input    | Pin Location: p154           |          |

|                                | Enable External Trigger Output     | Pin Location: p87            |          |

|                                | Disable JTAG Clock BUFG Insertio   | n                            |          |

|                                |                                    |                              |          |

|                                |                                    |                              |          |

|                                |                                    |                              |          |

|                                |                                    |                              |          |

|                                |                                    |                              |          |

|                                | < <u>P</u> revious Ne <u>x</u> t > | New                          | ILA Unit |

| Messages                       |                                    |                              |          |

|                                |                                    |                              | *        |

| 1                              |                                    |                              | •        |

Figure 5: ICON Options

# **Choosing ILA Parameters and Options**

Notice that a new ILA unit has been created in the device hierarchy on the left. The next step is to set up the ILA unit (Figure 6). The top set of parameters specify the Trigger Settings.

#### **Trigger Same as Data**

Use this option when the signals that you want to trigger on are exactly the same signals that you want captured. This option also conserves CLB and routing resources in the ILA core, but limits the data sample word width to the maximum trigger width of 64 bits. This is the common mode with most

logic analyzers. Notice that when this option is checked, the Data Width field disappears and Trigger Width is renamed to Trigger/Data Width.

#### **Trigger Width**

This specifies the width of the trigger bus, or the width of the Trigger/Data bus when trigger is the same as data. Valid numbers are even integers from 2 to 64.

#### Data Depth

The maximum number of data sample words that the ILA core can store is called the *data depth*. The data depth determines the number of data width bits contributed by each block RAM unit used by the ILA unit. You can set the data depth to one of five values in the following list:

- Data Depth = 256 samples, data width of one block RAM = 16 bits

- Data Depth = 512 samples, data width of one block RAM = 8 bits

- Data Depth = 1024 samples, data width of one block RAM = 4 bits

- Data Depth = 2048 samples data width of one block RAM = 2 bits

- Data Depth = 4096 samples, data width of one block RAM = 1 bit

#### Data Width (if necessary)

The width of each data sample stored by the ILA core is called the *data width*. If the data and trigger words are independent from each other, the maximum allowable data width depends on the target device type and data depth, with a maximum of 256. However, if trigger = data, the data/trigger width must be an even number between 2 and 64.

#### **Extended Matching**

If this option is checked, a sophisticated set of match options is available for all match units. The match options include:

- Finding one or more occurrences of an exact match of a trigger value or edge

- Finding one or more occurrences of a range of trigger values

- Detecting contiguous (pulse width) or non-contiguous (event count) trigger match conditions over a number of clock cycles

- Enabling usage in conjunction with other trigger match units to build the trigger condition boolean equation (using AND/OR)

- Enabling usage in conjunction with other trigger match units to build the trigger condition macro equation (using IF/THEN)

#### **Basic Matching**

If Extended Matching is not checked, a subset of the above features are available for all match units, saving CLB usage of the ILA core. These options include:

- Finding only one occurrence of an exact match of a trigger value or edge

- Enabling usage in conjunction with other trigger match units to build trigger condition boolean equation (using AND/OR)

#### Match Units

The number of match units can be set to one or two. Selecting two units allows a more flexible trigger condition equation to be a combination of both match units. Selecting one match unit conserves resources while allowing some flexibility in triggering.

Figure 6 shows a sample of the ILA parameters and options.

| ILA                              | Select Internal Logic Analyzer Options |

|----------------------------------|----------------------------------------|

| Trigger Settings                 | Trigger Width: 8                       |

| Data Settings<br>Data Depth: 256 | Data Width: 16                         |

| Match Settings                   | Match Units: 2                         |

Figure 6: ILA Options and Parameters

## **Choosing Net Connections for ILA Signals**

The Net Connections box (see Figure 7) under the Match Settings is where the user selects the signals that connect to the ILA core. If trigger is separate from data, then Clock, Trigger, and Data must be specified; when trigger equals data, only Clock and Trigger/Data must be specified. Double-clicking on the **Clock Net** label or clicking on the plus sign (+) next to it expands into the following (only the Net Connections box is shown):

| Net Connections |      |  |

|-----------------|------|--|

| ⊡ILA UNIT       |      |  |

| CLOCK N         | Т    |  |

| CH0:            |      |  |

| TRIGGER         | IETS |  |

| DATA NE         | S    |  |

| 1               |      |  |

Figure 7: ILA Core Clock Specification

Modifying the Clock Connection can be achieved by double-clicking on the CH0: label or highlighting it and clicking **Modify Connections**. The Select Net dialog box appears (see Figure 8).

| Select Net |         |             | × |  |  |  |

|------------|---------|-------------|---|--|--|--|

| Pattern:   |         | Ellter      |   |  |  |  |

| Structure  |         | Nets        |   |  |  |  |

| / [top]    | <b></b> | cik         |   |  |  |  |

|            |         | clk_c       |   |  |  |  |

|            |         | cnt[0]      |   |  |  |  |

|            |         | cnt[1]      |   |  |  |  |

|            |         | cnt[2]      |   |  |  |  |

|            |         | cnt[3]      |   |  |  |  |

|            |         | counter[0]  |   |  |  |  |

|            |         | counter[10] |   |  |  |  |

|            |         | counter[11] |   |  |  |  |

|            |         | counter[12] |   |  |  |  |

|            |         | counter[13] |   |  |  |  |

|            |         | counter[14] |   |  |  |  |

|            | -       | counter[15] | - |  |  |  |

| 4          | ▶       | •           | • |  |  |  |

|            | Select  | Cancel      |   |  |  |  |

Figure 8: Select Net Dialog

This dialog provides an easy interface to choose nets to connect to the ILA core. All the design's nets of the given hierarchical level appear in the **Nets** panel on the right, and the structure of the design can be traversed using the **Structure** panel on the left. Net names can be filtered for key phrases using the **Pattern** text box and **Filter** button. Once the net has been found, click **Select** to choose it and return to the main Core Inserter window.

All the nets for Trigger and Data must be chosen in this fashion. Once all the nets have been chosen for a given bus, the ILA bus name changes from red to black (see Figure 9).

| Net Connections   |  |

|-------------------|--|

|                   |  |

| CH0: /clk         |  |

| TRIGGER NETS      |  |

| DATA NETS         |  |

| CH0: /counter[8]  |  |

| CH1: /counter[9]  |  |

| CH2:              |  |

| CH3: /counter[11] |  |

| CH4:              |  |

| CH5:              |  |

| CH6:              |  |

| CH7:              |  |

Figure 9: Specifying Data Connections

Once all the Clock, Trigger, and Data nets are specified, click **Next**. A dialog appears asking if you want to proceed with Core Insertion. If Yes is chosen, the cores will be generated, inserted into the netlist, and a .ngo file is created by running the edif2ngd program. Details of this process can be viewed in the **Messages** panel at the bottom of the window. A Core Generation Complete message in the **Messages** panel signals success.

## Adding ILA Units

Each device can support up to 15 ILA units (the number of units may also be restricted by block RAM availability and ILA unit parameters). Additional units can be added to the project by selecting **Edit>New ILA Unit**, or going to the ICON Options window by clicking on ICON in the tree on the left panel (see Figure 5) and selecting the **New ILA Unit** button. Parameters for the additional ILA units are set up using the same procedure as above.

# **Chapter 4**

# Using the ChipScope Analyzer

# **Analyzer Overview**

The ChipScope Analyzer tool interfaces directly to the ILA and ICON cores. Users can configure their device, choose triggers, and view the results of the capture on the fly. The waveforms and triggers can be manipulated in many ways, providing an easy and intuitive interface to determine the functionality of the design.

# **Analyzer Menu Features**

# Selecting a Device/ILA Unit

A single target device (i.e., a Virtex, Virtex-E, or Spartan-II device) can contain up to 15 ILA units. The host communicates through a separate ChipScope Analyzer window for each ILA unit. You can select the current ILA unit only after you connect to the download cable and detect the Boundary Scan chain.

Select File>New ILA Unit>Unit n (where n is the ILA unit number) to choose a specific ILA unit. Note that the ILA unit number corresponds to the control port the ILA core is connected to in the case of instantiation, or the Unit

number in the case of Core Insertion. Figure 10 shows how ILA Unit 1 is selected.

| 🕻 ChipScope Analyzer [demo] - Unit O              |                    |                    |                   |              |                |              |  |  |  |

|---------------------------------------------------|--------------------|--------------------|-------------------|--------------|----------------|--------------|--|--|--|

| File Communication                                | C <u>o</u> nfigure | <u>B</u> us/Signal | Run/ <u>S</u> top | <u>D</u> ata | <u>W</u> indow | <u>H</u> elp |  |  |  |

| <u>N</u> ew ILA Unit ►                            | Unit 0             | \$ <u></u>         | ₽ ₽               | ø be         |                |              |  |  |  |

| Save Project As                                   | Unit 1             |                    |                   |              |                |              |  |  |  |

| Import Waveform                                   | Unit 2             |                    |                   |              |                |              |  |  |  |

| Export WaveForm ▶                                 | Unit 3             |                    |                   |              |                |              |  |  |  |

| <u>C</u> lose                                     | Unit 4             |                    |                   |              |                |              |  |  |  |

| <u> </u>                                          | Unit 5             |                    |                   |              |                |              |  |  |  |

|                                                   | Unit 6             |                    |                   |              |                |              |  |  |  |

|                                                   | Unit 7             |                    |                   |              |                |              |  |  |  |

|                                                   | Unit 8             |                    |                   |              |                |              |  |  |  |

|                                                   | Unit 9             |                    |                   |              |                |              |  |  |  |

|                                                   | Unit 10            |                    |                   |              |                |              |  |  |  |

|                                                   | Unit 11            |                    |                   |              |                |              |  |  |  |

|                                                   | Unit 12            |                    |                   |              |                |              |  |  |  |

|                                                   | Unit 13            |                    |                   |              |                |              |  |  |  |

|                                                   | Unit 14            |                    |                   |              |                |              |  |  |  |

|                                                   |                    | _                  |                   |              |                |              |  |  |  |

|                                                   |                    |                    |                   |              |                |              |  |  |  |

|                                                   |                    |                    |                   |              |                |              |  |  |  |

| Successfully opened Parallel Cable (port = LPT1). |                    |                    |                   |              | D              | ONE          |  |  |  |

Figure 10: Selecting New ILA Unit

If the Boundary Scan chain contains multiple devices that can serve as ILA targets, then select communication to one of the 15 possible ILA units in the target device using File>New ILA Unit>Device m>Device m Unit n (where m is the target device number n is the ILA unit number). Note that the ILA unit number corresponds to the control port number of the ICON unit to which the ILA component is connected, or the Unit number in the case of Core Insertion. Figure 11 shows how to select ILA Unit 0 in target Device 1.

If the trigger setup toolbar is not present in the current ChipScope window, then selecting a new ILA unit using this method simply refocuses the current window to the new ILA unit. However, if you select a new ILA unit after you have set up the trigger for the current one, a new ChipScope window opens. This feature allows you to view the waveforms of multiple ILA units at the same time.

| 🌔 ChipScope Analyzer     | [demo] - Unit (      | )                                 |                           |      |

|--------------------------|----------------------|-----------------------------------|---------------------------|------|

| File MultiLinx Config    | ure <u>B</u> us/Sign | al Run/ <u>S</u> top <u>D</u> ata | <u>W</u> indow <u>H</u> e | lp   |

| New ILA Unit             | Device 0 🕨           | R 9 9 R                           |                           |      |

| <u>O</u> pen Project     | Device 1 🕨           | Device 1 Unit 0                   |                           |      |

| Save Project             |                      | Device 1 Unit 1                   | 1                         |      |

| S <u>a</u> ve Project As |                      | Device 1 Unit 2                   |                           |      |

| Import Waveform          |                      | Device 1 Unit 3                   |                           |      |

| Export WaveForm 🕨        |                      | Device 1 Unit 4                   |                           |      |

| Close                    |                      | Device 1 Unit 5                   |                           |      |

| Exit                     |                      | Device 1 Unit 6                   |                           |      |

|                          |                      | Device 1 Unit 7                   |                           |      |

|                          |                      | Device 1 Unit 8                   |                           |      |

|                          |                      | Device 1 Unit 9                   |                           |      |

|                          |                      | Device 1 Unit 10                  |                           |      |

|                          |                      | Device 1 Unit 11                  |                           |      |

|                          |                      | Device 1 Unit 12                  |                           |      |

|                          |                      | Device 1 Unit 13                  |                           |      |

|                          |                      | Device 1 Unit 14                  |                           |      |

|                          |                      |                                   |                           |      |

|                          |                      |                                   |                           |      |

| JTag Chain Info          |                      |                                   |                           | DONE |

#### Figure 11: Selecting New ILA Unit in Target Device 1

New ILA units are displayed in their own window and the Device/Unit for a particular window is displayed in the title bar. All the ILA units may be triggered at the same time by configuring each trigger in turn. There is no current way to combine the waveform display or trigger setup amongst separate ILA units.

# **Working with Projects**

Projects hold important information about the ChipScope program state, such as signal naming, signal ordering, bus configurations, and trigger conditions. They allow you to conveniently store and retrieve this information between Analyzer sessions

When you first run the ChipScope Analyzer tool, the **Select Project** dialog box (Figure 12) opens, allowing you to create a new project or open an existing project.

| ChipScope                |

|--------------------------|

| -Select Project          |

| Open an Existing Project |

| Random More Projects     |

| Counter16                |

| PCI32                    |

| C:\ila\041\example       |

| C Create a new Project   |

|                          |

| OK cancel                |

Figure 12: Selecting a Project

#### **Creating A New Project**

To create a new project, select **Create a new Project** (Figure 12) and click **OK**. In the **Choose New Project File** dialog box (Figure 13), enter a new project filename name (using the .cpj extension) and click **Open**.

| ChipScope -        | Choose New Project File |            | ? ×          |

|--------------------|-------------------------|------------|--------------|

| Look jn:           | 🔄 example               | <b>• E</b> | <b>*</b>     |

| Counter16          |                         |            |              |

| PCI32.cpj          |                         |            |              |

| 🔊 Random.c         | pi                      |            |              |

|                    |                         |            |              |

|                    |                         |            |              |

|                    |                         |            |              |

|                    |                         |            |              |

|                    |                         | 1          |              |

| File <u>n</u> ame: | *.cp                    |            | <u>O</u> pen |

| Files of type:     | All Files (*.*)         | •          | Cancel       |

|                    |                         |            |              |

Figure 13: Creating a New Project

## **Opening An Existing Project**

To open an existing project, select it from the list of recently opened projects. To browse through all available project files, select **More Projects**. When you locate the desired project click **Open**.

# **Saving Projects**

Projects are automatically saved when you exit the ChipScope software.

To rename the current project, or to save a copy to another filename, select **File>Save Project As** (Figure 14), type the new name in the dialog box, and click **Save**.

| ChipScope Analyzer       | ChipScope - Choose New Project File          | ? × |

|--------------------------|----------------------------------------------|-----|

| File Communication       | Look jn: 🔄 example 🔽 🗈 🛅                     |     |

| New ILA Unit             |                                              |     |

| S <u>a</u> ve Project As | i and Counter16.cpj                          |     |

| Import Waveform          | Man PCI32.cpj<br>Random.cpj                  |     |

| Export WaveForm 🕨        | Mandolit.cp                                  |     |

| <u>C</u> lose n          |                                              |     |

| <u>E</u> xit             |                                              |     |

| BUS/SIGNAL X             |                                              |     |

| Signal_0 0               |                                              |     |

| Signal_1 1               |                                              |     |

| Signal_2 1               | File <u>n</u> ame: <u>*.cp</u> i <u>O</u> pe | en  |

|                          | Files of type: All Files (*.*)               | cel |

Figure 14: Saving a Project

# Importing and Exporting

Only VCD waveforms can be imported. You can import the waveform display from a VCD file and export to VCD, FBDF, and ASCII files. The VCD format is a common waveform viewer file format and the FBDF format is compatible with the Agilent Technologies' 16700 Series logic analyzers. The ASCII format is a text-only list format that is well suited to a script parser or spreadsheet import.

To import a waveform, select **File>Import Waveform**. A dialog box opens, allowing you to browse for waveform files. After locating and selecting the desired file, click **Open**. The waveform display in the ChipScope window now contains the imported waveform.

You can export a waveform file in a similar fashion. To export the waveform to a VCD file, select File>Export Waveform>VCD Export. To export the

waveform to a FBDF file, select File>Export Waveform>FBDF Export. To export the waveform to an ASCII file, select File>Export Waveform>ASCII Export. In each case, a dialog box opens and you can browse for the desired storage folder location. After finding the target location and entering the waveform file name, click Save. The waveform is now stored in the desired format.

# Closing and Exiting ChipScope

To close a ChipScope window, select File>Close. To exit the ChipScope program, select File>Exit. In both cases, if you have not stored the waveform, a dialog box opens, asking if you want to store the current waveform before closing/exiting. If you select Yes, another dialog box opens, from which you can save the waveform.

The difference between closing and exiting is: closing closes the current ChipScope window; exiting closes all ChipScope windows and ends the program. However, if only one ChipScope window is open, closing and exiting have the same effect.

## **Opening and Closing a MultiLINX Connection**

You can connect the MultiLINX cable to the host computer by using a serial communications port (e.g., COM1), the USB (Universal Serial Bus) port connection, or both. However, only one connection to the MultiLINX cable is supported at a time.

## **Opening a Serial Port MultiLINX Connection**

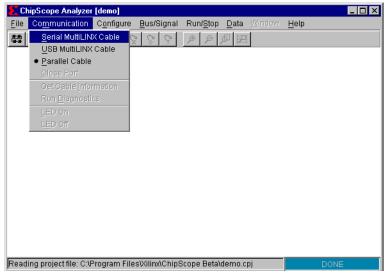

If the MultiLINX cable connects to the host computer by way of the serial port, then select **Communication>Open Serial Port** (Figure 15).

Figure 15: Opening a Serial Port Connection to MultiLINX

After you select **Communication>Open Serial Port**, a small dialog box opens (Figure 16). Enter the proper serial port name, select the baud rate for the serial port connected to the MultiLINX cable, then click **OK**. Make sure you select a port that is not in use by another resource.

| 🃒 ChipSc | оре                   | х |

|----------|-----------------------|---|

| ?        | Serial Port Selection |   |

|          | Port: COM1            |   |

|          | Baud Rate: 🛛 🗖        |   |

|          |                       |   |

|          | OK Cancel             |   |

Figure 16: Selecting a Serial Port

When the connection opens, a success message appears in the status bar at the bottom of the ChipScope window. At this point, ChipScope queries the

Boundary Scan chain to determine its composition (see "Configuring the Target Device(s)" on page 11). If the MultiLINX connection fails to open, a dialog box opens, notifying you of the problem.

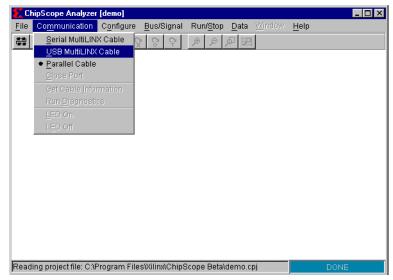

#### **Opening a USB Port MultiLINX Connection**

If the MultiLINX cable connects to the host computer by way of the USB port, then select Communication>Open USB Port (Figure 17).

When the connection opens, a success message appears in the status bar at the bottom of the ChipScope window. At this point, ChipScope queries the Boundary Scan chain to determine its composition (see "Configuring the Target Device(s)" on page 11). If the MultiLINX connection fails to open, a dialog box opens, notifying you of the problem.

Figure 17: Opening a USB Connection to MultiLINX

## **Closing the MultiLINX Connection**

Select **Communication>Close Port** to close the connection to the MultiLINX cable. You must re-establish a connection to the MultiLINX cable before any communication between the ChipScope program and the ILA units in the target device can resume.

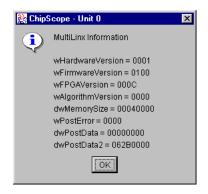

#### **Getting MultiLINX Cable Information**

You can upload information pertaining to the MultiLINX cable (such as the hardware version, memory size, etc.) by selecting **Communication>Get Cable Information**. See the sample dialog in Figure 18 for the MultiLINX cable information.

Figure 18: Getting Cable Information

## **Running MultiLINX Cable Diagnostics**

To verify that the MultiLINX cable is properly connected to and communicating with the host computer, select **Communication>Run Diagnostics**. A dialog box opens, reporting whether or not the cable is functioning properly.

You can also quickly verify that the MultiLINX cable is communicating with the host computer by turning the LED on the MultiLINX cable on and off. To do this, select the **Communication>LED On** and **Communication>LED Off**, respectively.

## **Opening a Parallel Cable III Connection**

ChipScope supports the Parallel Cable III (HW-JTAG-PC). To open a connection to the Parallel Cable III, make sure the cable is connected to one of the computer's parallel ports. Select **Communication>Parallel Cable** (Figure 19). ChipScope prompts you for the port name. Type the printer port name in the port selection box (usually the default LPT1 is correct) and click **OK**. If successful, ChipScope queries the Boundary Scan chain to determine its composition (see "Configuring the Target Device(s)" on page 11).

If ChipScope returns the error message Failed to Open Communication Port, verify that the Parallel Cable III is connected to the correct LPT port. If you have not installed the Parallel Cable III driver, follow the instructions in "Installing the Parallel Cable III Driver" on page 11 in Chapter 1 to install the required device driver software.

|                                                                                                                                                     |                                   | ChipScope - Unit 0                               | × |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------|---|

| ChipScope Analyze           File         Communication           Serial MultiLIN         USB MultiLIN           • Parallel Cable         Close Port | Configure<br>IX Cable 🙀<br>(Cable | Parallel Port Selection<br>Port PT1<br>OK Cancel |   |

| Get Cable [nfo<br>Run <u>D</u> jagnost<br>LED On<br>L <u>E</u> D Off                                                                                |                                   |                                                  |   |

#### Figure 19: Opening a Parallel Cable III Connection

# Configuring the Target Device(s)

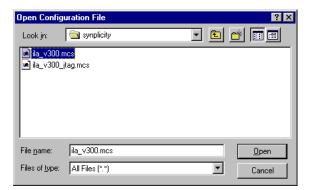

You can use ChipScope software with one or more target devices (Virtex, Virtex-E, or Spartan-II FPGAs). The first step is to set up all of the devices in the Boundary Scan chain.

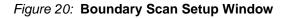

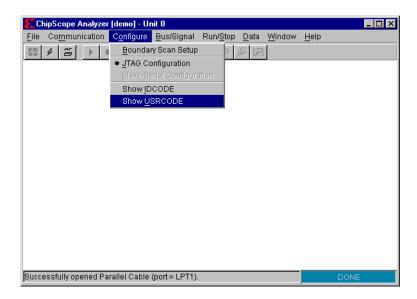

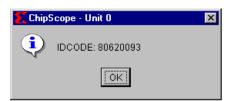

#### Setting Up the Boundary Scan Chain

Once ChipScope has successfully communicated with a download cable, it automatically queries the JTAG chain to find its composition. All Xilinx Virtex/E/EM, Spartan-II, Spartan-XL, 9500/XL/XV, 4000XL/XLA, and 18V00 devices are automatically detected. The entire IDCODE can be verified for Virtex, Virtex-E, Virtex-EM, and Spartan-II devices. To view the chain composition, select **Configure>Boundary Scan Setup**. A dialog appears with all detected devices in order. For devices that are not automatically detected, the IR (Instruction Register) length must be specified to insure proper communication to the ILA and ICON cores This information can be found in the device's BSDL file. The following example has a CoolRunner® CPLD, XC18V02 PROM, and Virtex V150 in a chain. A non-zero IR length must be specified for the unknown (CoolRunner) device in order to close the dialog (see Figure 20).

| hipScope |              |                   |               |           | ×       |

|----------|--------------|-------------------|---------------|-----------|---------|

| -Scan Ch | ain Device C | rder              |               |           |         |

| Index    | Name         | Device Name       | IR Length     | Device ID | User ID |

| 0        |              | Unknown           | 0             | 0494b02b  |         |

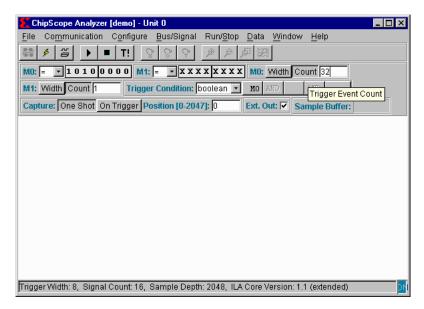

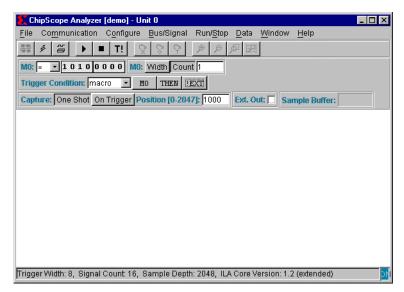

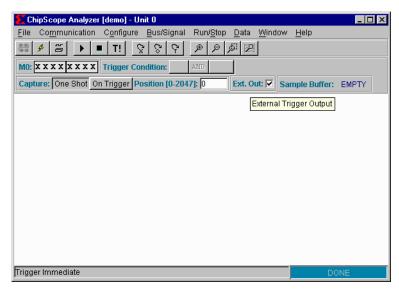

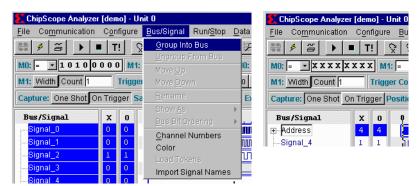

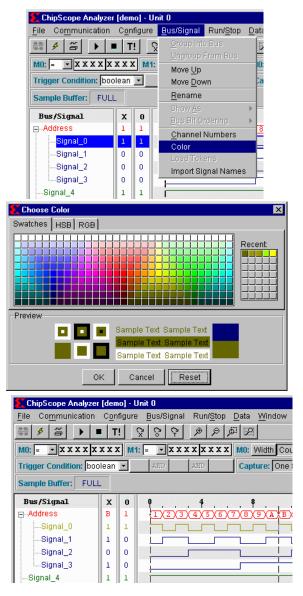

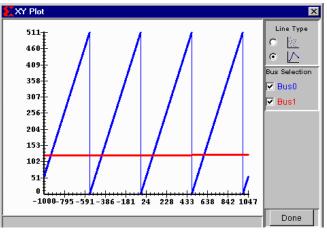

| 1        |              | XC1800 8 05006093 |               |           |         |