## **Package Specifications**

This section contains specifications for the following Virtex-II packages:

- "CS144 Chip-Scale BGA Package (0.80 mm Pitch)" on page 427

- "FG256 Fine-Pitch BGA Package (1.00 mm Pitch)" on page 428

- "FG456 Fine-Pitch BGA Package (1.00 mm Pitch)" on page 429

- "FG676 Fine-Pitch BGA Package (1.00 mm Pitch)" on page 430

- "BG575 Standard BGA Package (1.27 mm Pitch)" on page 431

- "BG728 Standard BGA Package (1.27 mm Pitch)" on page 432

- "FF896 Flip-Chip Fine-Pitch BGA Package (1.00 mm Pitch)" on page 433

- "FF1152 Flip-Chip Fine-Pitch BGA Package (1.00 mm Pitch)" on page 434

- "FF1517 Flip-Chip Fine-Pitch BGA Package (1.00 mm Pitch)" on page 435

- "BF957 Flip-Chip BGA Package (1.27 mm Pitch)" on page 436

Øfff(M)C

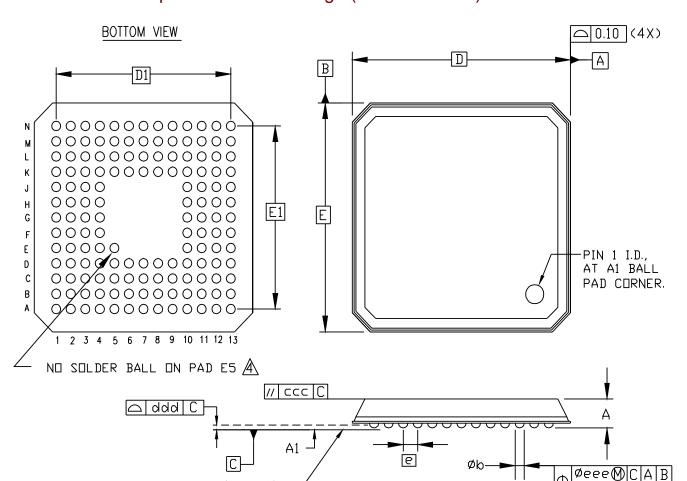

# CS144 Chip-Scale BGA Package (0.80 mm Pitch)

| S<br>M<br>B                    | MILLIMETERS |      |      |

|--------------------------------|-------------|------|------|

| L                              | MIN.        | N□M. | MAX. |

| Α                              | *           | *    | 1.20 |

| A <sub>1</sub>                 | 0.35        | 0.40 | 0.45 |

| D/E                            | 12.00 BSC   |      |      |

| D <sub>1</sub> /E <sub>1</sub> | 9.60 BSC    |      |      |

| е                              | 0.80 BSC    |      |      |

| Øb                             | 0.45        | 0.50 | 0.55 |

| ccc                            | Z           | X    | 0.10 |

| ddd                            | X           | X    | 0.12 |

| eee                            | *           | *    | 0.15 |

| fff                            | ×           | *    | 0.08 |

| М                              | 13          |      |      |

## NOTES:

SEATING PLANE

- 1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994

- 2. SYMBOL "M" IS THE PIN MATRIX SIZE,

- 3. CONFORMS TO JEDEC MO-205-BE (DEPOPULATED).

- A PAD 'E5' IS FOR PAD 'A1' CORNER INDICATION.

Figure 4-31: CS144 Chip-Scale BGA Package

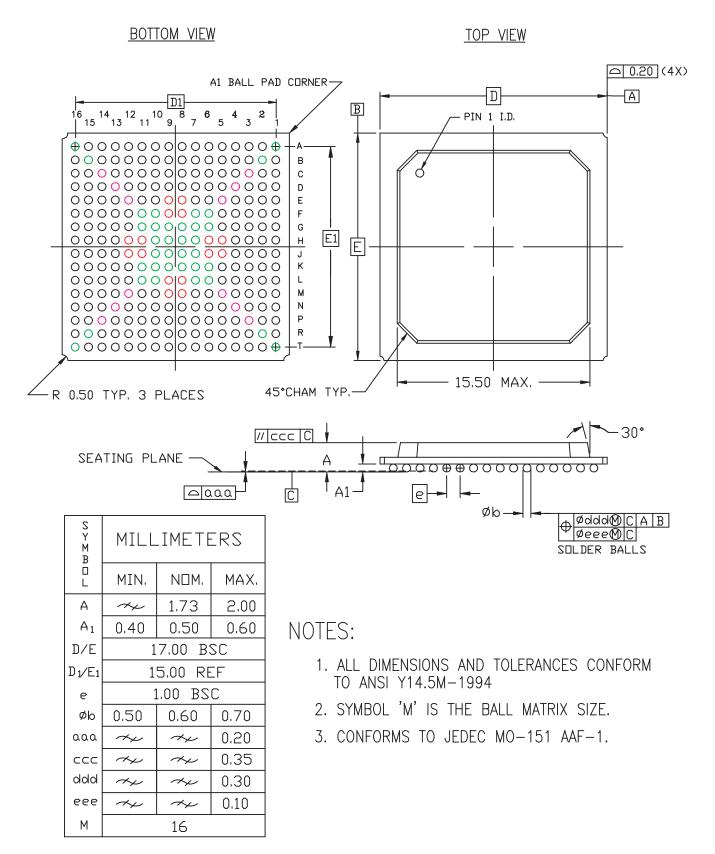

#### FG256 Fine-Pitch BGA Package (1.00 mm Pitch)

Figure 4-32: FG256 Fine-Pitch BGA Package

#### FG456 Fine-Pitch BGA Package (1.00 mm Pitch)

Figure 4-33: FG456 Fine-Pitch BGA Package

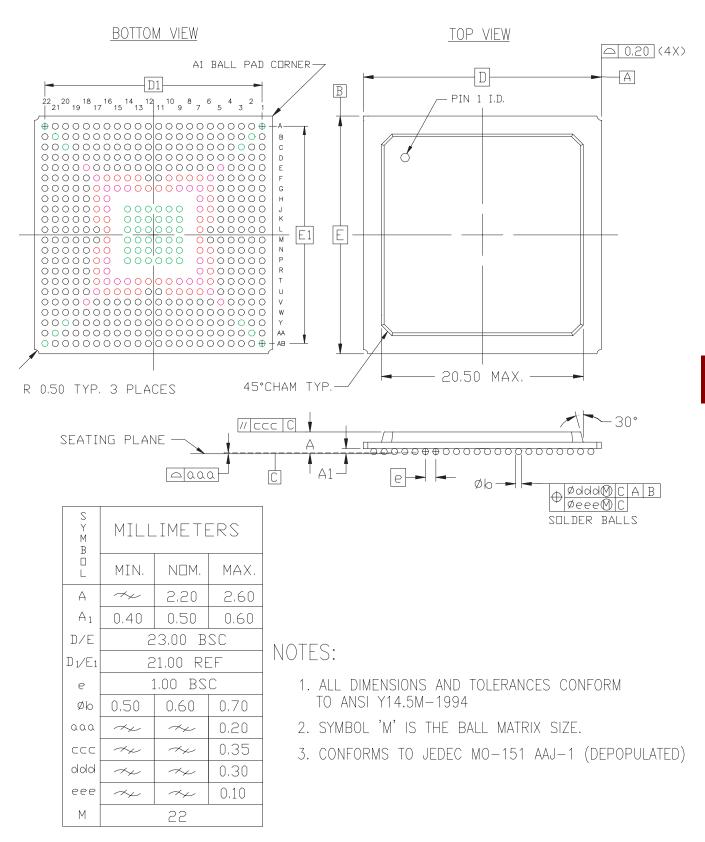

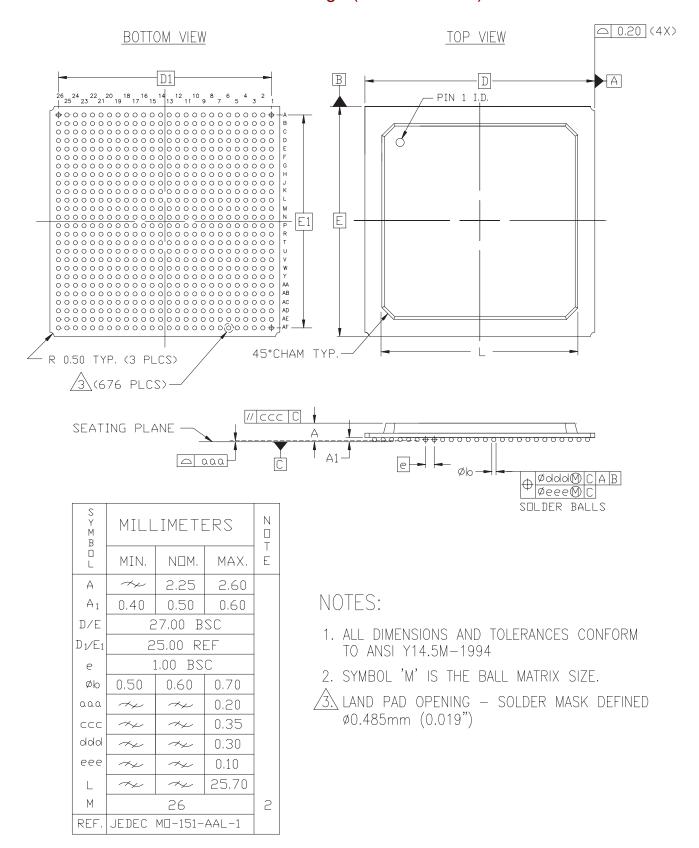

#### FG676 Fine-Pitch BGA Package (1.00 mm Pitch)

Figure 4-34: FG676 Fine-Pitch BGA Package

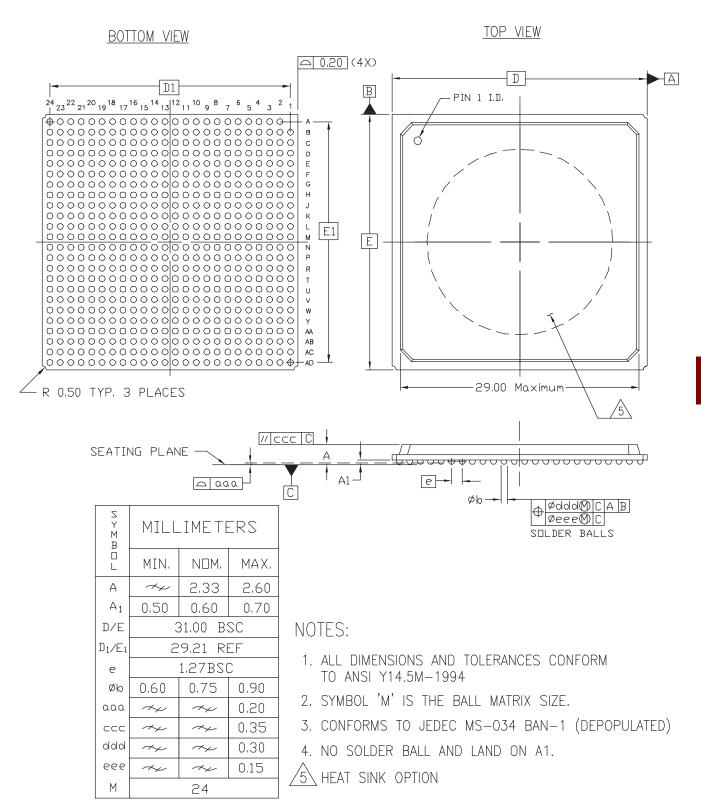

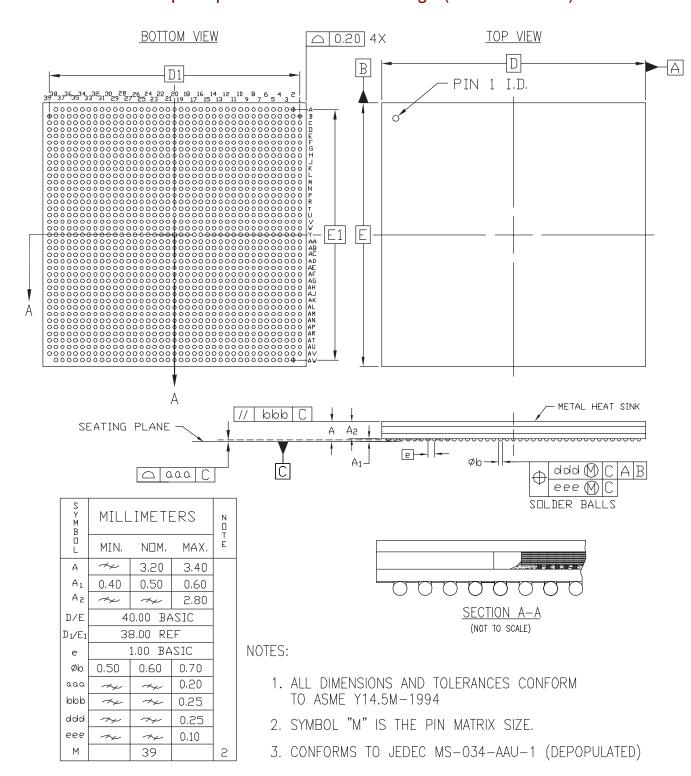

#### BG575 Standard BGA Package (1.27 mm Pitch)

Figure 4-35: BG575 Standard BGA Package

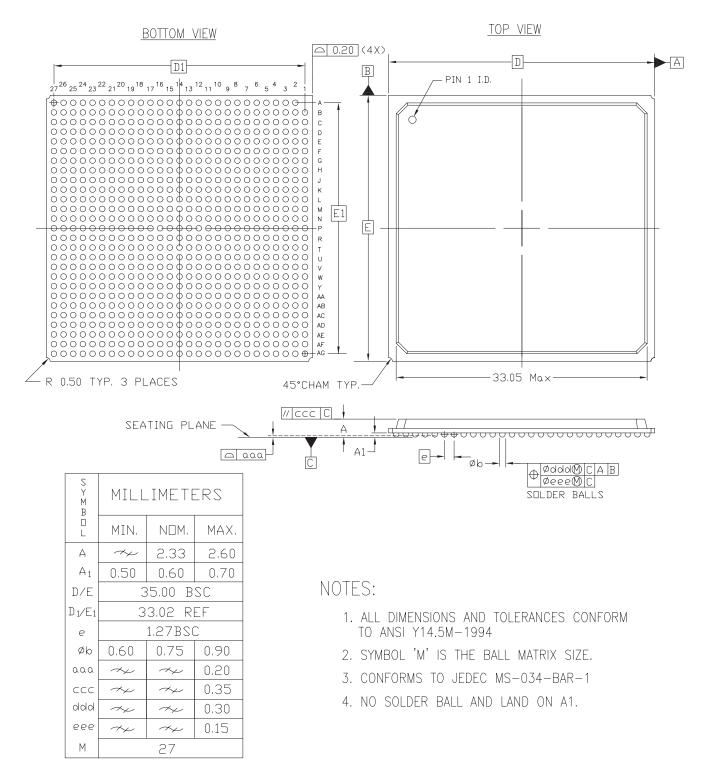

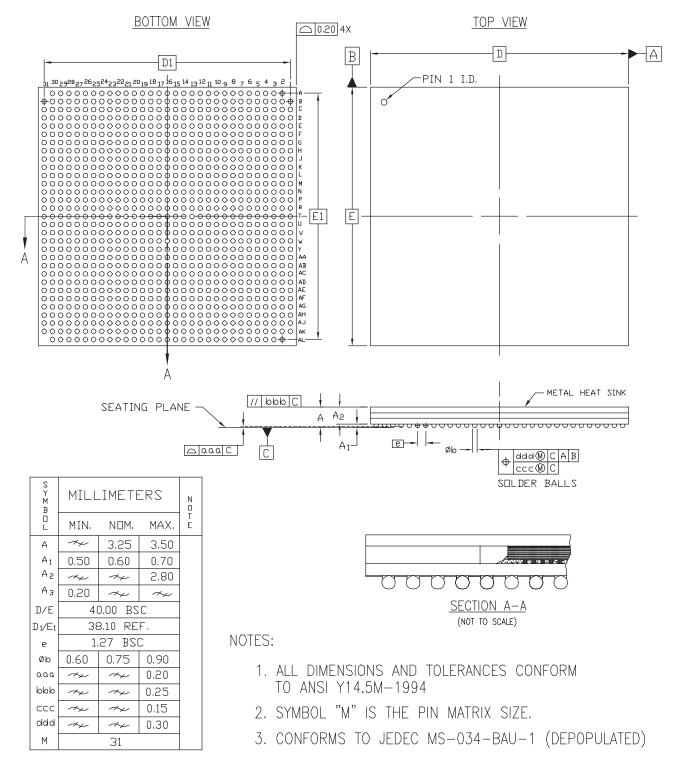

#### BG728 Standard BGA Package (1.27 mm Pitch)

Figure 4-36: BG728 Standard BGA Package

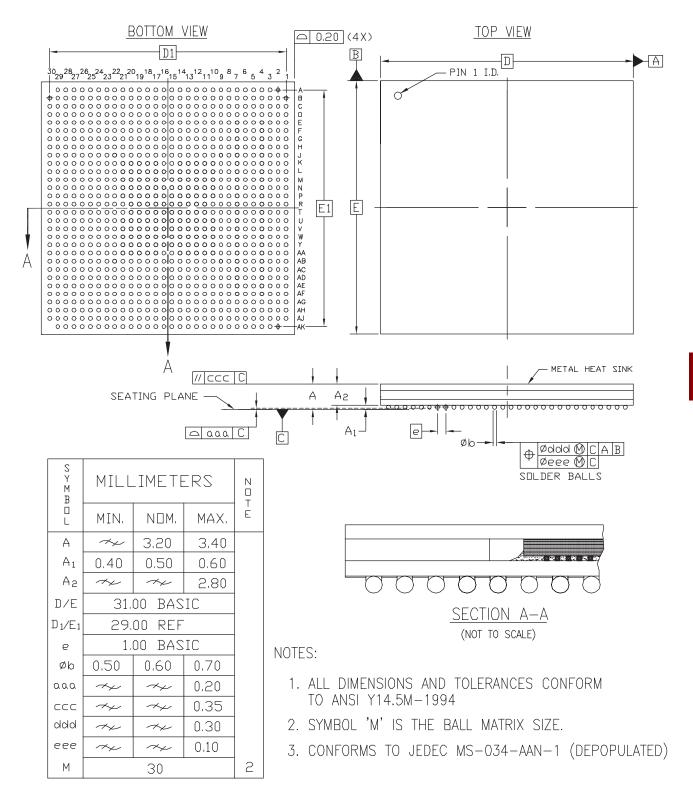

#### FF896 Flip-Chip Fine-Pitch BGA Package (1.00 mm Pitch)

Figure 4-37: FF896 Flip-Chip Fine-Pitch BGA Package

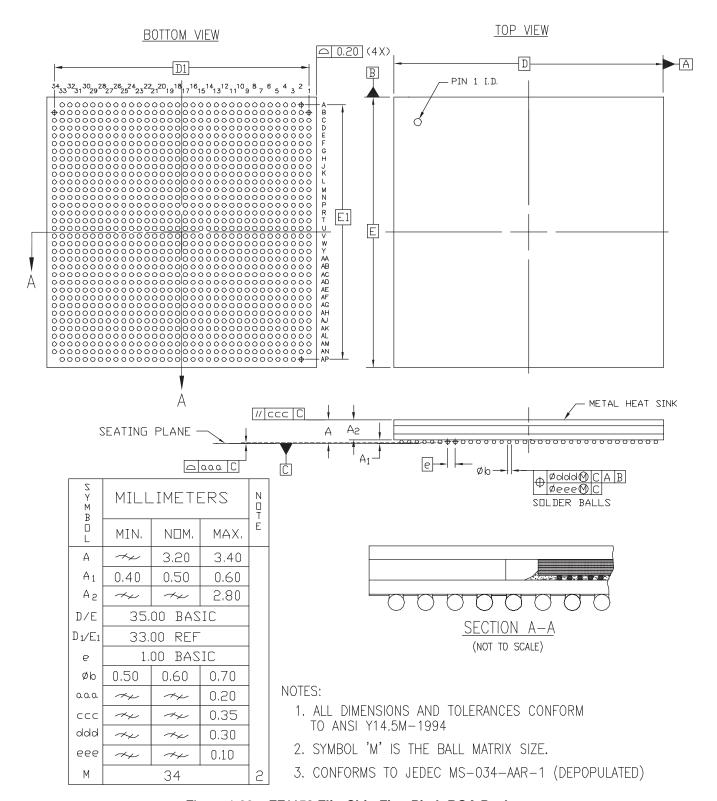

## FF1152 Flip-Chip Fine-Pitch BGA Package (1.00 mm Pitch)

Figure 4-38: FF1152 Flip-Chip Fine-Pitch BGA Package

## FF1517 Flip-Chip Fine-Pitch BGA Package (1.00 mm Pitch)

Figure 4-39: FF1517 Flip-Chip Fine-Pitch BGA Package

## BF957 Flip-Chip BGA Package (1.27 mm Pitch)

Figure 4-40: BF957 Flip-Chip BGA Package

# Flip-Chip Packages

As silicon devices become more integrated with smaller feature sizes as well as increased functionality and performance, packaging technology is also evolving to take advantage of these silicon advancements. Flip-chip packaging is the latest packaging option introduced by Xilinx to meet the demand for high I/O count and high performance required by today's advanced applications.

Flip-chip packaging interconnect technology replaces peripheral bond pads of traditional wire-bond interconnect technology with area array interconnect at the die/substrate interface.

The area array pads contain wettable metallization for solders (either eutectic or highlead), where a controlled amount of solder is deposited either by plating or screen-printing. These parts are then reflowed to yield bumped dies with relatively uniform solder bumps spread over the surface of the device. Unlike traditional packaging in which the die is attached to the substrate face up and the connection is made by using wire, the bumped die in a flip-chip package is flipped over and placed face down, with the conductive bumps connecting directly to the matching metal pads on the ceramic or organic laminate substrate. The solder material at molten stage is self-aligning and produces good joints even if the chip is placed offset on the substrate.

Flip-chip packages are assembled on high-density, multi-layer ceramic or organic laminate substrates. Since flip-chip bump pads are in area array configuration, very fine lines and geometry on the substrates are required to be able to successfully route the signals from the die to the periphery of the substrates. Multi-layer build-up structures offer this layout flexibility on flip-chip packages, and they provide improvements in power distribution and signal transmission characteristics.

#### Advantages of Flip-Chip Technology

Flip-chip interconnections in combination with the advanced multi-layer laminated substrates provide superior performance over traditional wire-bond packaging. Benefits include:

- Easy access to core power/ground and shorter interconnects, resulting in better electrical performance

- Better noise control since the inductance of flip-chip interconnect is lower

- Excellent thermal performance due to direct heatsinking to backside of the die

- Higher I/O density since bond pads are in area array format

- Smaller size