## Tech Topics

# High-Speed Transceiver Logic (HSTL)

### Introduction

Virtex<sup>™</sup> Series of FPGAs feature the Xilinx exclusive SelectI/O+<sup>™</sup> technology integrating support for 20 single-ended and differential I/O standards. HSTL is one of the single-ended I/O interfaces supported by every Virtex device, eliminating the need for external level translators to interface with high-speed memories and reducing overall system design complexity and cost. Virtex FPGAs are the only PLD solutions with integrated HSTL I/Os for memory intensive designs.

## The HSTL Standard

HSTL is a technology-independent interface standard for digital integrated circuits. It was developed for voltage scalable and technology independent I/O structures. The I/O structures required by this standard are; differential amplifier inputs (with one input internally tied to a user-supplied input reference voltage for single ended inputs), and outputs using output power supply inputs ( $V_{CCO}$ ) that may differ from those operating the device itself.

#### Advantages

- 1. HSTL compliance does not specify device supply voltages, making it a processindependent I/O standard. The lower voltage-level swing associated with this standard makes high-speed HSTL I/O solutions possible for any core voltage level device.

- 2. A given circuit need not have all four classes of output drivers, but each circuit must have at least one of the four classes to claim HSTL output compliance.

- 3. The HSTL nominal logic switching range is 0.0 V to 1.5 V, resulting in faster outputs with reduced power dissipation, and minimized EMI concerns.

- 4. HSTL gives system designers enhanced flexibility in optimizing system performance with adjustable trip-point (V<sub>REF</sub>) and output power supply voltage (V<sub>CCO</sub>).

## **Applications**

In computing, slow memory access times have traditionally hindered fast processor operations. In the mid-frequency range (between 100 MHz and 180 MHz), the I/O interface options for all single ended signals are; HSTL, GTL/GTL+, SSTL, and LVTTL. Beyond 180 MHz, the HSTL standard is the only single ended I/O interface available.

With HSTL speeds, faster I/O interface significantly improves overall system performance. HSTL is the I/O interface of choice for high-speed memory applications, and are ideal for driving address buses to multiple memory banks.

#### Terminated Loads

The HSTL I/O standard specifies the output characteristics for both series (Class II) and parallel (Class I, III, and IV) terminated loads. The limiting factors in high-speed digital I/O circuits are the typical transmission line effects (ringing, reflections, crosstalk, and EMI). Transmission line reflections are the greatest constraint. Controlling reflection requires impedance matching using parallel or series terminations.

There are four classes of HSTL output specifications depending on output drive requirements. Virtex devices support all the push-pull output buffers for parallel terminated loads (Class I, III, and IV.)

## HSTL Class I Output Buffers

HSTL Class 1 output buffers have two types of loads:

- Push-pull output buffers for unterminated loads.

- Push-pull output buffers for symmetrically parallel terminated loads ( $V_{TT} = V_{CCO}/2$ ).

HSTL Class I

It is not recommended to use the output buffers for unterminated loads because of signal integrity issues, specifically ringing, affecting overall performance by slowing down the outputs.

$$V_{CCO} = 1.5V$$

$V_{TT} = 0.75V$

$J_{TT} = 0.75V$

$V_{REF} = 0.75V$

$V_{REF} = 0.75V$

$V_{R133_{10_{111699}}}$

#### Figure 1: Symmetrically parallel terminated loads

| Parameter                               | Min                    | Тур                 | Max                    |

|-----------------------------------------|------------------------|---------------------|------------------------|

| V <sub>CCO</sub>                        | 1.40                   | 1.50                | 1.60                   |

| V <sub>REF</sub>                        | 0.68                   | 0.75                | 0.90                   |

| V <sub>TT</sub>                         |                        | $V_{CCO} 	imes 0.5$ |                        |

| V <sub>IH</sub>                         | V <sub>REF</sub> + 0.1 |                     |                        |

| V <sub>IL</sub>                         |                        |                     | V <sub>REF</sub> – 0.1 |

| V <sub>OH</sub>                         | V <sub>CCO</sub> -0.4  |                     |                        |

| V <sub>OL</sub>                         |                        |                     | 0.4                    |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | - 8                    | -                   | -                      |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 8                      | -                   | -                      |

#### Table 1: HSTL Class I Voltage Specification

### HSTL Class III Output Buffers

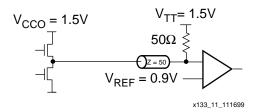

Push-pull output buffers for asymmetrically parallel terminated loads (V<sub>TT</sub> = V<sub>CCO</sub>). HSTL Class III

Figure 2: Asymmetrically parallel terminated loads

| Parameter                               | Min                    | Тур              | Max                    |

|-----------------------------------------|------------------------|------------------|------------------------|

| V <sub>CCO</sub>                        | 1.40                   | 1.50             | 1.60                   |

| V <sub>REF</sub> <sup>(1)</sup>         |                        | 0.90             |                        |

| V <sub>TT</sub>                         |                        | V <sub>CCO</sub> |                        |

| V <sub>IH</sub>                         | V <sub>REF</sub> + 0.1 |                  |                        |

| V <sub>IL</sub>                         |                        |                  | V <sub>REF</sub> – 0.1 |

| V <sub>OH</sub>                         | V <sub>CCO</sub> – 0.4 |                  |                        |

| V <sub>OL</sub>                         |                        |                  | 0.4                    |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | - 8                    | -                | -                      |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 24                     | -                | -                      |

Table 2: HSTL Class III Voltage Specification

Per EIA/JESD8-6, "The value of V<sub>REF</sub> is to be selected by the user to provide optimum noise margin in the use conditions specified by the user.

## HSTL Class IV Output Buffers

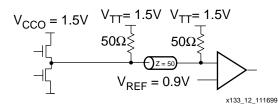

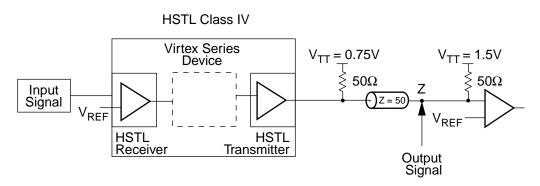

Push-pull output buffers for asymmetrically double parallel terminated loads (V<sub>TT</sub> = V<sub>CCO</sub>). HSTL Class IV

Figure 3: Asymmetrically double parallel terminated loads

| Parameter                               | Min                    | Тур              | Max                    |

|-----------------------------------------|------------------------|------------------|------------------------|

| V <sub>CCO</sub>                        | 1.40                   | 1.50             | 1.60                   |

| V <sub>REF</sub> <sup>(1)</sup>         |                        | 0.90             |                        |

| V <sub>TT</sub>                         |                        | V <sub>CCO</sub> |                        |

| V <sub>IH</sub>                         | V <sub>REF</sub> + 0.1 |                  |                        |

| V <sub>IL</sub>                         |                        |                  | V <sub>REF</sub> – 0.1 |

| V <sub>OH</sub>                         | V <sub>CCO</sub> – 0.4 |                  |                        |

| V <sub>OL</sub>                         |                        |                  | 0.4                    |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | - 8                    | -                | -                      |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 48                     | -                | -                      |

Table 3: HSTL Class IV Voltage Specification

Per EIA/JESD8-6, "The value of V<sub>REF</sub> is to be selected by the user to provide optimum noise margin in the use conditions specified by the user.

#### **Notes**

- 1. Customers may use IBIS models to compute the source impedance values.

- 2. Slew rate control is not provided for the HSTL I/Os.

### **Waveforms**

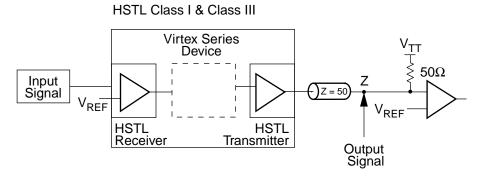

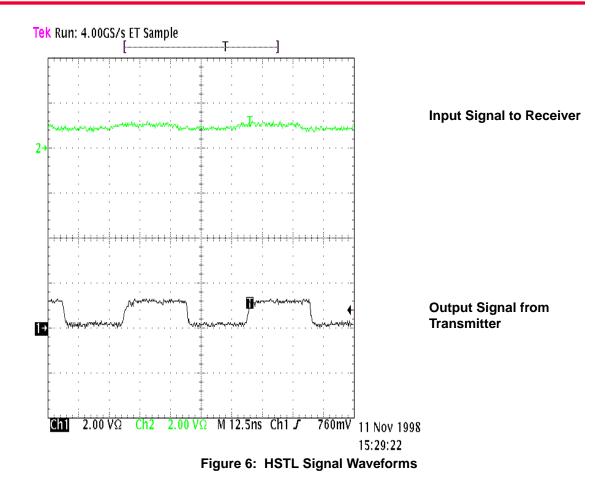

The input pulse in Figure 6 is the input signal of Figures 4 and 5. This pulse was produced from a pulse generator. The output waveform shown in Figure 6 is observed at the node Z shown in Figures 4 and 5. As shown in Figure 6, the Virtex series HSTL I/O produces a substantial output swing from a very small input swing.

Figure 5: HSTL Class IV Receiver/Transmitter

# Virtex Advantages

Using the Xilinx exclusive SelectI/O+ technology, the Virtex series delivers up to 804 single ended I/Os capable of supporting the HSTL standard listed in Table 4. With every I/O capable of supporting this array of I/O standards, the Virtex series of FPGAs provides maximum board lay-out flexibility. By reducing overall system design complexity and cost, the SelectI/O+ technology makes the Virtex series the ideal solution for direct interfacing to high performance memory devices. Virtex devices are the only FPGAs to support the HSTL I/O standard to seamlessly interface with other high performance HSTL standard devices.

## Supported Standards

|  | Table 4: | HSTL standards | s supported b | y the Virtex se | ries of devices |

|--|----------|----------------|---------------|-----------------|-----------------|

|--|----------|----------------|---------------|-----------------|-----------------|

| Standard | Virtex       | Virtex-E |

|----------|--------------|----------|

| HSTL-I   | $\checkmark$ |          |

| HSTL-II  | _            | _        |

| HSTL-III | $\checkmark$ |          |

| HSTL-IV  | $\checkmark$ |          |

### References

#### **Related Xilinx Documents**

XAPP133: "Using the Virtex Select I/O" at: http://www.xilinx.com/xapp/xapp133.pdf

#### **Standards**

EIA/JEDEC STANDARD EIA/JESD8-6

#### http://www.jedec.org/download/freestd/jesd8-xx/default.htm

© 1999 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <u>http://www.xilinx.com/legal.htm</u>. All other trademarks and registered trademarks are the property of their respective owners.