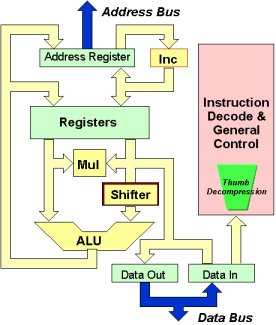

ARM7TDMI Block Diagram

|

|

|

|

|

The

ARM7TDMI is a 3-stage pipeline 32-bit RISC processor. Pipelining

is employed so that all parts of the processing and memory systems

can operate continuously. Typically, while one instruction is being

executed, its successor is being decoded, and a third instruction

is being fetched from memory. The ARM7TDMI processor is built around

a bank of 37 32-bit registers including six status registers.

|