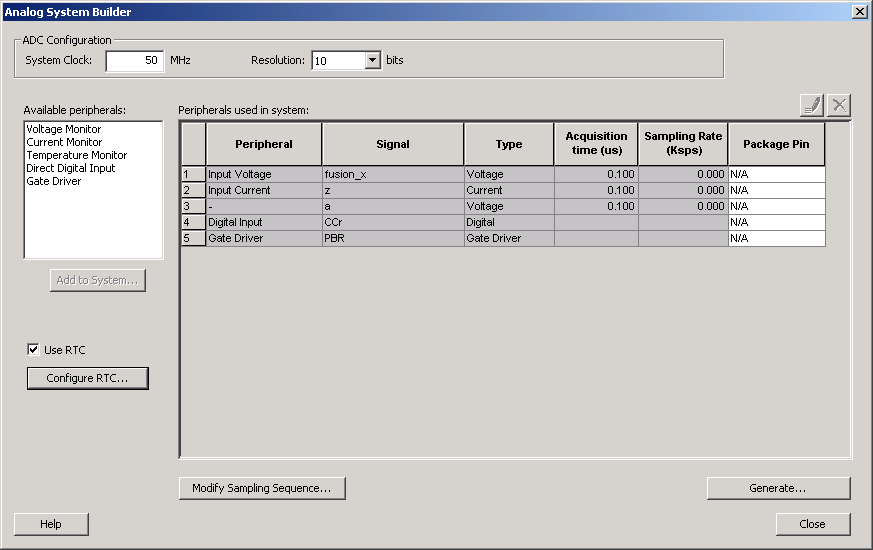

The Analog System Builder main window enables you to create and configure your analog system (as shown in the figure below).

Analog System Builder Dialog Box

The number of peripherals you can add to the system is limited by the size of your device.

The Analog to Digital Converter (ADC) Configuration sets your System Clock speed and resolution.

Available Peripherals lists all the analog peripherals you can add to your design. As you add peripherals, some resources are exhausted (used up). The Analog System Builder disables peripherals in the list for which there are insufficient resources. If you want to add additional peripherals, select a larger device, or remove some existing peripherals from your design.

The Peripherals used in system grid lists specific information about each peripheral, including

Peripheral - The type of the peripheral (such as Voltage Monitor, Temp. Monitor, etc.).

Signal - Name you specified for the signal of your service in the service configuration dialog box.

Type - Identifies channel type for the service.

Acquisition Time - The required acquisition time per a given input channel. SmartGen takes the required acquisition times for all peripherals and computes the ADC clock frequency and the number of ADC clocks per sample, per peripheral, such that each peripheral meets or exceeds your required acquisition time.

Sampling Rate (in ms) - The rate at which a given channel gets sampled by the ADC. See the Modify Sampling Sequence topic for more information on setting your sampling rate. Sampling rate is affected by the following parameters:

Package Pin - SmartGen automatically assigns a package pin for each channel in each peripheral added to the system. If you require a specific channel for a certain package pin (if you have board layout issues), you can choose a specific pin for that channel.

Use RTC (real time counter) / Configure RTC - You can configure the Real Time Counter so that it functions as a chronometer, configure it to generate periodic alarms in conjunction with other peripherals (such as the Voltage monitor), etc. Select Use RTC and click Configure RTC to configure the Real Time Counter.

Modify Sampling Sequence - Displays the Sample Sequencer. Since there is only one ADC and thirty analog input channels, the channels must be sequenced in the order in which they are required to be sampled.

If your Analog System resources you build on your device exceed the total system resources available for your device, SmartGen issues a warning. You cannot generate a system that exceeds your total system resources. The Analog System Builder also generates a warning if you have a port name conflict between two or more services. You cannot create generate a system with port name conflicts.

When you click Generate the system, SmartGen creates HDL source files, memory (MEM) files, configuration files, and log files. They all appear in your SmartGen project folder under the <core_name> directory. Do not modify any of these generated files or store additional files in this folder. This folder will be recreated every time you overwrite the core.