Date: Tue Nov 15 2011 - 05:10:50 PST

Hi All,

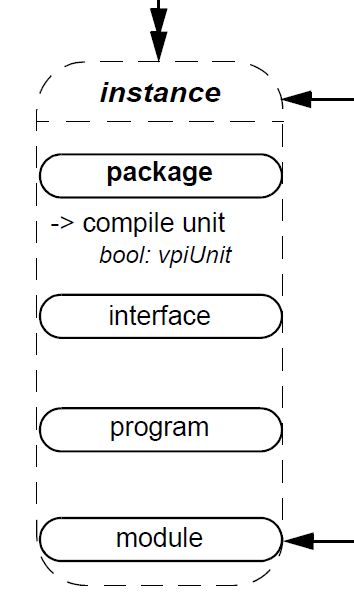

I have question about vpiUnit. Do we need it? In 1800-2008 It is in two

places :

and :

#define vpiUnit 602

SystemVerilog3.1a 31.2:

3) Compilation units are represented as packages that have a vpiUnit

property set to TRUE. Such implicitly

declared packages shall have implementation dependent names.

But 3.1a it's not a standard. Now in 1800-2009 37.10 we have defined

difference between package and compilation unit scope in vpiFullName

property:

5) vpiFullName for objects that exist within a compilation unit shall begin

with '$unit::'. As a result, the full

name for objects within a compilation unit may be ambiguous. vpiFullName for

a package shall be the name of the

package and should end with "::"; this syntax disambiguates between a module

and a package of the same name.

vpiFullName for objects that exist in a package shall begin with the name of

the package followed by "::". The

separator :: shall appear between the package name and the immediately

following name component. The .

separator shall be used in all cases except package and class defn.

So Think there are two ways:

* vpiIUnit can be obsolate (included image should be changed #define

should stay for backword compatibility)

or

* we need add into 37.10:

10.) Compilation units have a vpiUnit property set to TRUE.

Regards,

Radek Nawrot

-- This message has been scanned for viruses and dangerous content by MailScanner, and is believed to be clean.