Date: Thu Jun 06 2013 - 01:15:42 PDT

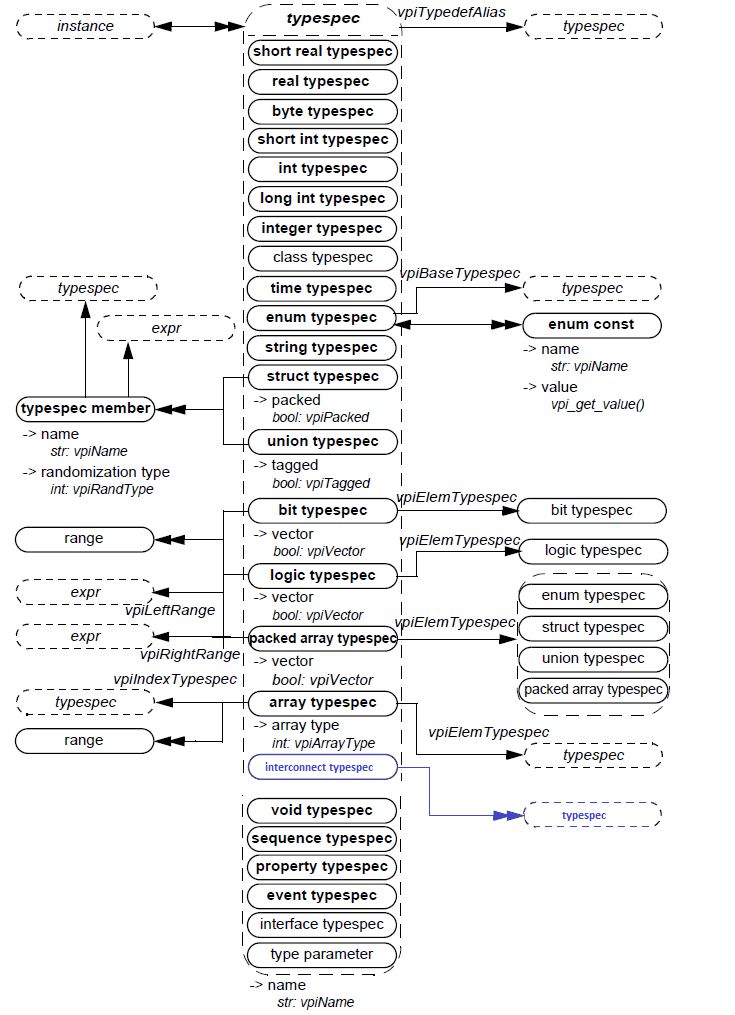

Yes. "A port without a packed dimension defined is a scalar; and for that object, the property vpiScalar shall return TRUE and the property vpiVector shall return FALSE..." If it we want to organize ports and net incuding 1800-2012 types: 1) vpiPortType shall be one of the following three types: vpiPort, vpiInterfacePort, vpiInterconnectPort or vpiModportPort. Port type depends on the formal, not on the actual. 6) A port without a packed dimension defined is a scalar; and for that object, the property vpiScalar shall return TRUE and the property vpiVector shall return FALSE. A port with one or more packed dimensions defined is a vector, and the property vpiVector shall return TRUE (vpiScalar shall return FALSE). Packed struct port and packed array port are vectors, and the property vpiVector shall return TRUE (vpiScalar shall return FALSE). For an array port, the vpiScalar and vpiVector properties shall return the values of the respective properties for an array element. The vpiScalar and vpiVector properties shall return FALSE for all other port objects. For interconnect port vpiScalar and vpiVector shall return undefined . header: #define vpiPortType 611 #define vpiInterfacePort 1 #define vpiModportPort 2 #define vpiInterconnectPort 3 /* vpiPort is also a port type. It is defined in vpi_user.h */ To add interconnect into vpi (37.16 Net) also should be changed: 25) A logic net without a packed dimension defined is a scalar; and for that object, the property vpiScalar shall return TRUE and the property vpiVector shall return FALSE. A logic net with one or more packed dimensions defined is a vector, and the property vpiVector shall return TRUE (vpiScalar shall return FALSE). Packed struct nets and packed array nets are vectors, and the property vpiVector shall return TRUE (vpiScalar shall return FALSE). A net bit is a scalar, and the property vpiScalar shall return TRUE (vpiVector shall return FALSE). The properties vpiScalar and vpiVector when queried on a handle to an enum net shall return the value of the respective property for an object for which the typespec is the same as the base typespec of the typespec of the enum net. For an integer net or a time net, the property vpiVector shall return TRUE (vpiScalar shall return FALSE). For an array net, the vpiScalar and vpiVector properties shall return the values of the respective properties for an array element. The vpiScalar and vpiVector properties shall return FALSE for all other net objects. For interconnect net vpiScalar and vpiVector shall return undefined . header: #define vpiNetType 22 /* net subtypes: */ #define vpiWire 1 /* wire net */ #define vpiWand 2 /* wire-and net */ #define vpiWor 3 /* wire-or net */ #define vpiTri 4 /* tri net */ #define vpiTri0 5 /* pull-down net */ #define vpiTri1 6 /* pull-up net */ #define vpiTriReg 7 /* three-state reg net */ #define vpiTriAnd 8 /* three-state wire-and net */ #define vpiTriOr 9 /* three-state wire-or net */ #define vpiSupply1 10 /* supply-1 net */ #define vpiSupply0 11 /* supply-0 net */ #define vpiNone 12 /* no default net type (1364-2001) */ #define vpiUwire 13 /* unresolved wire net (1364-2005) */ #define vpiInterconnect 14 /* interconnection*/ And (37.23 Typespec): 12) For an interconnect typespec, vpi_iterate(vpiTypespec, handle) shall return the set of typespeces used in that interconnection . header: /* typespecs */ #define vpiLongIntTypespec 625 #define vpiShortRealTypespec 626 #define vpiByteTypespec 627 #define vpiShortIntTypespec 628 #define vpiIntTypespec 629 #define vpiClassTypespec 630 #define vpiStringTypespec 631 #define vpiChandleTypespec 632 #define vpiEnumTypespec 633 #define vpiEnumConst 634 #define vpiIntegerTypespec 635 #define vpiTimeTypespec 636 #define vpiRealTypespec 637 #define vpiStructTypespec 638 #define vpiUnionTypespec 639 #define vpiBitTypespec 640 #define vpiLogicTypespec 641 #define vpiArrayTypespec 642 #define vpiVoidTypespec 643 #define vpiTypespecMember 644 #define vpiPackedArrayTypespec 692 #define vpiSequenceTypespec 696 #define vpiPropertyTypespec 697 #define vpiEventTypespec 698 #define vpiInterconnectTypespec 699 Radek _____ From: Jim Vellenga [mailto:vellenga@cadence.com] Sent: Wednesday, June 05, 2013 5:09 PM To: Radoslaw Nawrot; 'Bresticker, Shalom'; sv-cc@eda.org Subject: RE: [sv-cc] Array of net on module port But there are also array ports. For nets of an unpacked array type, vpiScalar and vpiVector have the same value as for the most containing non-unpacked element type. And there are also packed and unpacked struct ports, I believe. It’s also going to be interesting as to what we do with “interconnect” ports now, since their type depends on what they’re connected to, and via bit-selects they can connect to multiple kinds of elements. Keeping up with the implications of all the changes can boggle the mind. Jim From: owner-sv-cc@eda.org [mailto:owner-sv-cc@eda.org] On Behalf Of Radoslaw Nawrot Sent: Wednesday, 5 Jun 2013 10:28 AM To: 'Bresticker, Shalom'; sv-cc@eda.org Subject: RE: [sv-cc] Array of net on module port So it propose to change (37.14 Ports): 6) Properties vpiScalar and vpiVector shall indicate if the port is 1 bit or more than 1 bit. They shall not indicate anything about what is connected to the port. to: 6) A port without a packed dimension defined is a scalar; and for that object, the property vpiScalar shall return TRUE and the property vpiVector shall return FALSE. A port with one or more packed dimensions defined is a vector, and the property vpiVector shall return TRUE (vpiScalar shall return FALSE). Radek _____ From: Bresticker, Shalom [mailto:shalom.bresticker@intel.com] Sent: Tuesday, June 04, 2013 4:08 PM To: Radoslaw Nawrot; sv-cc@eda.org Subject: RE: [sv-cc] Array of net on module port Ø Maybe we should treat ports ther same way as nets? I would think so. Probably when this detail was added for nets, no one thought about ports. Shalom From: owner-sv-cc@eda.org [mailto:owner-sv-cc@eda.org] On Behalf Of Radoslaw Nawrot Sent: Tuesday, June 04, 2013 10:57 To: sv-cc@eda.org Subject: [sv-cc] Array of net on module port Hello, I have an example: module top; wire X [5]; test TEST(X); ..... endmodue module test(output OUT[5]); ... endmodule LRM says: for net's (37.16 Nets): 25) A logic net without a packed dimension defined is a scalar; and for that object, the property vpiScalar shall return TRUE and the property vpiVector shall return FALSE. A logic net with one or more packed dimensions defined is a vector, and the property vpiVector shall return TRUE (vpiScalar shall return FALSE). Packed struct nets and packed array nets are vectors, and the property vpiVector shall return TRUE (vpiScalar shall return FALSE). A net bit is a scalar, and the property vpiScalar shall return TRUE (vpiVector shall return FALSE). (..) For an array net, the vpiScalar and vpiVector properties shall return the values of the respective properties for an array element. The vpiScalar and vpiVector properties shall return FALSE for all other net objects. for ports (37.14 Ports): 6) Properties vpiScalar and vpiVector shall indicate if the port is 1 bit or more than 1 bit. They shall not indicate anything about what is connected to the port. So X : scalar : true vector : false OUT: scalar: false vector: true Is it correct? Maybe we should treat ports ther same way as nets? Regards, Radek -- This message has been scanned for viruses and dangerous content by <http://www.mailscanner.info/> MailScanner, and is believed to be clean. --------------------------------------------------------------------- Intel Israel (74) Limited This e-mail and any attachments may contain confidential material for the sole use of the intended recipient(s). Any review or distribution by others is strictly prohibited. If you are not the intended recipient, please contact the sender and delete all copies. -- This message has been scanned for viruses and dangerous content by <http://www.mailscanner.info/> MailScanner, and is believed to be clean. -- This message has been scanned for viruses and dangerous content by MailScanner, and is believed to be clean.