| |

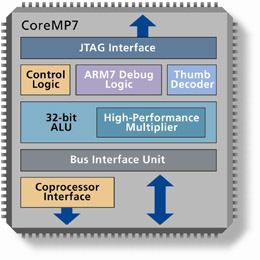

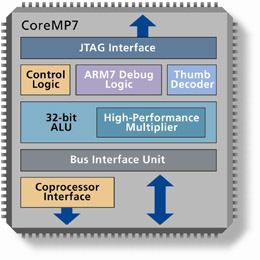

- Compatible with ARM7TDMI-S

- 32/16-bit RISC architecture

- 32-bit ARMv4T instruction set

- 16-bit Thumb instruction set

- 32-bit Arithmetic Logic Unit (ALU)

- 3-stage pipeline

- 32-bit external bus interface

- Embedded real-time debug and JTAG interface

- Optimized for Actel Flash-based M7 devices

- Implemented fully in the fabric

- All I/Os are accessible to the user

- Seamless FPGA design and debug tool flow and integration

CoreMP7 Subsystem:

An important set of functional blocks in a microprocessor is the

subsystem peripherals. These include all of the low-level functionality

that must be implemented around the processor for it to be used

in an application.

The

CoreMP7 subsystem peripherals include:

- AHB-Lite interface

- APB interface

- AHB to APB bridge

- Memory controller

- Interrupt controller

- Timers

- Serial interface

- Buffered I/O interface

The CoreMP7 subsystem peripherals are delivered as part of the

CoreConsole IP Deployment Platform (IDP).

CoreMP7 is available for use in M7 Flash family devices, which

have been made ARM-ready for seamless use of the processor core.

The devices are based on Actel's nonvolatile Flash technology and support

250 k to 3 M gates and up to 616 high-performance I/Os.

M7 Fusion Devices

The M7 Fusion devices combine the power of ARM7 with the world's first mixed-signal FPGAs. Fusion devices integrate configurable analog, large Flash memory blocks, SRAM memory, comprehensive clock generation and management circuitry, and high performance programmable logic all in a single chip. The devices interface to the real world with up to 30 high-voltage-tolerant analog inputs that can be directly connected to signals from -12 V to +12 V, eliminating the need for signal preconditioning. The on-chip Fusion analog to digital converter (ADC) is configurable and supports resolutions up to 12 bits, and sample rates up to 600 k samples per second (ksps). M7 Fusion devices give engineers a single-chip solution for their real world design challenges.

The M7 Fusion devices combine the power of ARM7 with the world's first mixed-signal FPGAs. Fusion devices integrate configurable analog, large Flash memory blocks, SRAM memory, comprehensive clock generation and management circuitry, and high performance programmable logic all in a single chip. The devices interface to the real world with up to 30 high-voltage-tolerant analog inputs that can be directly connected to signals from -12 V to +12 V, eliminating the need for signal preconditioning. The on-chip Fusion analog to digital converter (ADC) is configurable and supports resolutions up to 12 bits, and sample rates up to 600 k samples per second (ksps). M7 Fusion devices give engineers a single-chip solution for their real world design challenges.

| Package |

M7AFS600

|

M7AFS1500

|

| PQ208 |

95/46 (40) |

|

| FG256 |

119/58 (40) |

119/58 (40) |

| FG484 |

172/86 (40) |

228/86 (40) |

| FG676 |

|

278/139 (40) |

Note: The data in the table shows the single-ended I/Os / differential pairs (analog I/O) for the device in the package.

For more information, visit the Fusion Devices web page.

M7 ProASIC3/E Devices

The M7 ProASIC3/E devices are a secure, low-power, live at power-up, single-chip

solution. They are reprogrammable and offer fast time-to-market benefits

at an ASIC-level unit cost. These features enable engineers to create

high-performance, high-density system applications with ARM7

using existing FPGA design flows and tools. In addition, M7 ProASIC3/E

devices offer on-chip, user memory and clock conditioning circuitry

based on up to six on-board phase-locked loops (PLLs).

The M7 ProASIC3/E devices are a secure, low-power, live at power-up, single-chip

solution. They are reprogrammable and offer fast time-to-market benefits

at an ASIC-level unit cost. These features enable engineers to create

high-performance, high-density system applications with ARM7

using existing FPGA design flows and tools. In addition, M7 ProASIC3/E

devices offer on-chip, user memory and clock conditioning circuitry

based on up to six on-board phase-locked loops (PLLs).

| Package |

M7A3P250

|

M7A3P400

|

M7A3P600

|

M7A3P1000

|

M7A3PE600

|

M7A3PE1500

|

M7A3PE3000

|

| VQ100 |

68/13

|

|

|

|

|

|

|

| PQ208 |

151/34

|

151/34

|

154/35

|

154/35

|

147/65

|

147/65

|

147/65

|

| FG144 |

97/24

|

97/25

|

97/24

|

97/25

|

|

|

|

| FG256 |

|

178/38

|

179/45

|

177/44

|

165/79

|

|

|

| FG484 |

|

194/38

|

227/56

|

300/74

|

270/135

|

280/136

|

280/136

|

| FG676 |

|

|

|

|

|

439/209

|

|

| FG896 |

|

|

|

|

|

|

616/300

|

Note: The data in this table shows the single-ended I/Os / differential pairs available for the device in the package.

For more information, visit the ProASIC3 Devices web page.

A major benefit for users of Actel's CoreMP7 FPGA optimized ARM7

microprocessor is the huge ecosystem of tools and design support

as well as the large volume of embedded software code that exists

for it. To this rich selection of tools, Actel offers its world-class

set of FPGA development tools, a development kit, and device programming.

CoreConsole:

- Intellectual Property Deployment Platform (IDP)

- Includes a graphical interface and a block stitcher to simplify

the assembly of IP cores for embedded applications in FPGAs.

- Integrates with Actel Libero IDE, which includes Actel

Designer software for place-and-route.

- Read the latest CoreConsole Release Notes

and download software.

ARM RealView® Developer Kit:

- Provides tools for building, debugging, and managing software

development projects that run on the processor.

- Contains an optimized C compiler, debugger, assembler, and

instruction set simulator.

- Available from Actel.

Actel FlashPro3 Programmer:

- M7 ProASIC3/E and M7 Fusion devices support in-system programming (ISP).

- Configuration data is supplied through a standard JTAG interface

from a microprocessor, Silicon Sculptor II, or FlashPro3.

CoreMP7 Development Kit:

- Complete prototype and development environment

- Includes: board with an M7 ProASIC3 device, Actel Libero IDE Gold,

CoreConsole, C program development tools, an optional FlashPro3

programmer with a USB cable, a power supply, tutorials, and

support documentation.

- Enables application development with CoreMP7 in Actel nonvolatile

M7 ProASIC3/E devices, and supports ISP, device serialization,

and FlashLock on-chip system security.

- For more details, visit the CoreMP7 Development Kit page.

Datasheets:

CoreMP7:

CoreAI:

Fusion:

ProASIC3/E:

SysBASIC - CoreMP7 Subsystem Cores:

Packaging Data:

Application Notes:

CoreMP7:

Fusion:

ProASIC3/E:

Product Briefs:

CoreMP7:

Fusion:

ProASIC3/E:

White Papers:

ARM7:

Fusion:

ProASIC3/E:

Product Information Brochures (PIB):

CoreMP7:

ARM-ready Development Tools:

Fusion:

ProASIC3/E:

User's Guides & Manuals:

CoreConsole:

CoreMP7:

|

Terms and Conditions of Use

Terms and Conditions of Use

Privacy Policy

Privacy Policy

The M7 ProASIC3/E devices are a secure, low-power, live at power-up, single-chip

solution. They are reprogrammable and offer fast time-to-market benefits

at an ASIC-level unit cost. These features enable engineers to create

high-performance, high-density system applications with ARM7

using existing FPGA design flows and tools. In addition, M7 ProASIC3/E

devices offer on-chip, user memory and clock conditioning circuitry

based on up to six on-board phase-locked loops (PLLs).

The M7 ProASIC3/E devices are a secure, low-power, live at power-up, single-chip

solution. They are reprogrammable and offer fast time-to-market benefits

at an ASIC-level unit cost. These features enable engineers to create

high-performance, high-density system applications with ARM7

using existing FPGA design flows and tools. In addition, M7 ProASIC3/E

devices offer on-chip, user memory and clock conditioning circuitry

based on up to six on-board phase-locked loops (PLLs).